:54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ

t

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах для организации обмена между ЭВМ и периферийными устройствами.

Известны устройства для обмена информации, содержащие блок приоритета, выходной генератор сигналов, блок обнаружения паузы и входной каскад И .

Недостатки этих устройств состоят в низком быстродействии.

Наиболее близким к изобретению является устройство для обмена -информацией , содержащее блок обнаружения паузы, подключенный входом с первым выходом блока приема, а выходом - с первым входом блока формирования сигналов приоритета, дешифратор собственного адреса, подключенный входом к второму.выходу блока приема,а выходом - с входом блока формирования управляющих сигналов и блоком синхронизации, группа входов и выходов которого является входом и выходом устройства, выход блока синхронизации соединен через счетчик сообщений с блоком формирования управляющих сигналов и схемой сравнения, а вход - с выходом блока формирования сигналов приоритета, вход и выход приоритета которого является входом и выходом приоритета устройства, блок формирования запроса,

первый вход и выход которого соединены соответственно с первым входом и выходом схемы сравнения, второй вход и выход которого соединены соответственно с входом и выходом блока

10 формирования сигналов приоритета,

третий вход которого является входом запроса устройства, а третий выход соединен с вторым входом блока выдачи информации, первый вход и выход

15 которого являются соответственно входом и выходом устройства 2 .

Недостатком этого устройства является низкая надежность и ограниченные функциональные возможности,

20 не допускающие различения типа информации, например, числовой, адресной, управляющей и т.д., а также возможность занятия канала связи rta неограниченноевремя, вызванная тем,

25 что вызываемое устройство по какимлибо причинам не выдает ответного :;игнала.

Цель изобретения - повышение надежности устройства путем обнаружения аварийных ситуаций, вызванных

отсутствием ответного сигнала вызываемого устройства.

|Поставл Шная цель достигается те что в устройство, содержащее блок запроса, первые вход и выход которого соединены соответственно с первы выходом н входом схемы сравнения, второй вход - с входом запроса устройства, а второй выход - с первым входом блока приоритета, блок синхронизации, подключенный первым выXOJ3OM через счетчик сообщений с вторьгй входом схемы сравнения, а первыЦ входом - с выходом блока дешифрации и первым входом блока формироЬания управляющих сигналов, группа- выходов которого является группой управляющих выходов устройства, второй вход соединен с вторым входОм схемы сравнения, а третий вход с входом обнаружения паузы, выходом пЬдключеиного к второму входу блока пфюритета, вход - выход которого является входом-выходом приоритета устройства, а второй выход подключен к второму входу блока синхронизации, вход-выход которого является входом-выходом синхронизации устройства, первый вход блока дешифрации соеди - ен с информационным входомвыходом устройства, а вход блока обнаружения паузы соединен с управляющим входом-выходом устройства, введены счетчик времени и блок коммутации, причем выход счетчика времени соединен с выходом индикации устройства и третьим входом блока запроса, третьим выходом подключенным К: первому входу блока коммутации, второй вход которого соединен с первым входом счетчика времени и вторым -ВЫХОДОМ блока приоритета, третий вход - с вторым входом счетчика времени и выходом блока синхронизац 5И, первый выход - с информационны1л входом-выходом устройства, а второй выход - с управляющим входом-выходом устройства, вход и выход блока обнаружения паузы соединены соответственно с вторым и третьи 1 входами блока дешифрации.

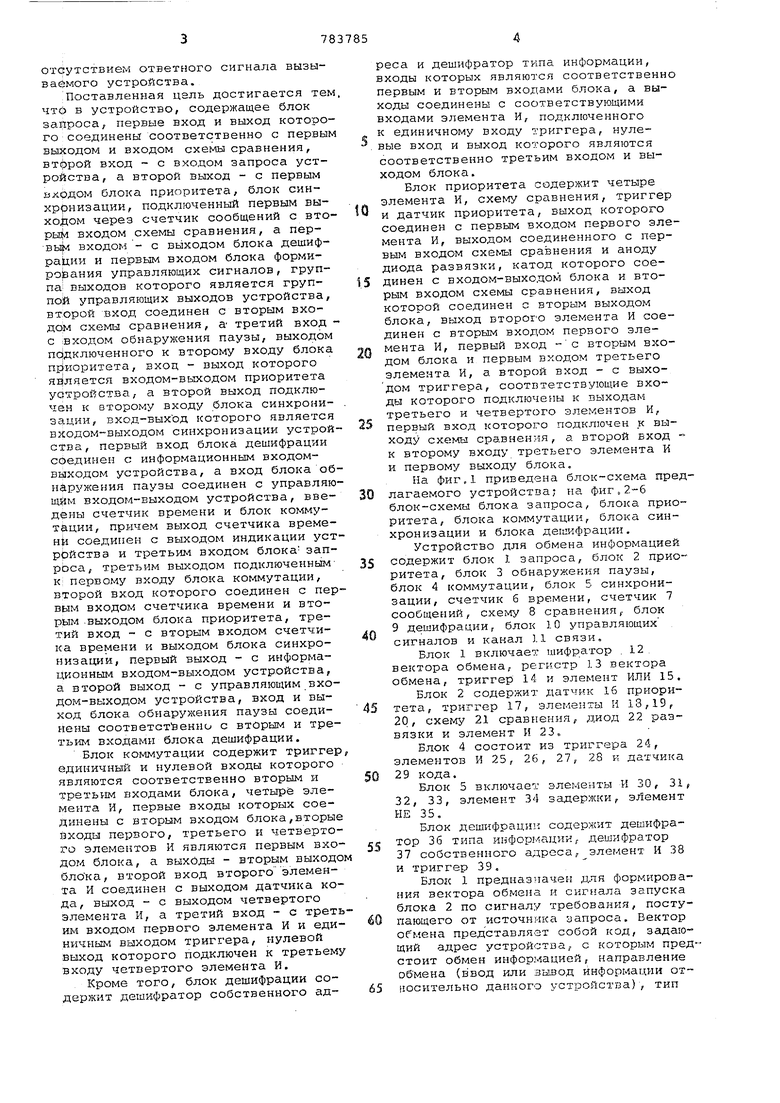

Блок коммутации содержит триггер единичный и нулевой входы которого являются соответственно вторым и треты-м входами блока, четыре элемента И, первые входы которых соединены с вторым входом блока,вторые входы первого, третьего и чштвертого элементов И являются первым входом блока, а выходы - вторым выходо блока, второй вход второго элемента И соединен с выходом датчика кода , выход - с выходом четвертого элемента И, а третий вход - с третьим входом первого элемента И и единичным выходом триггера, нулевой выход которого подключен к третьему входу четвертого элемента И.

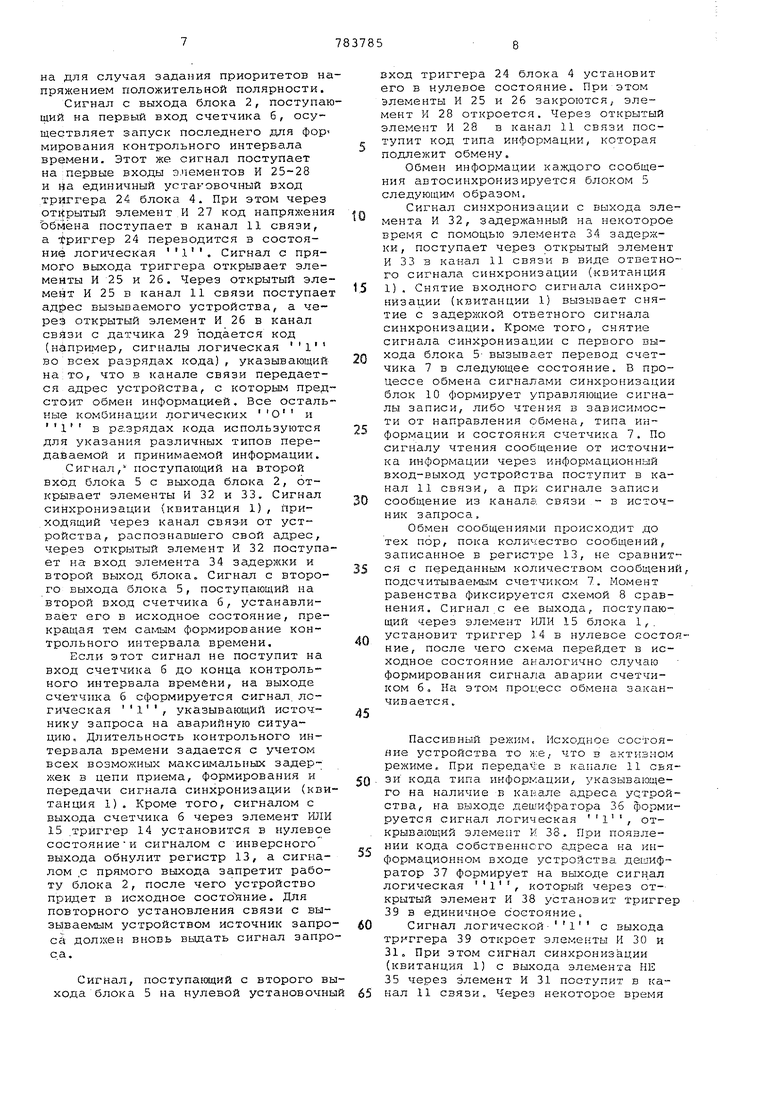

Кроме того, блок дешифрации содержит дешифратор собственного адраса и дешифратор типа информации, входы которых являются соответственно первым и вторым входами блока, а выходы соединены с соответствующими входами элемента И, подключенного к единичному входу триггера, нулевые вход и выход которого являются соответственно третьим входом и выходом блока.

Блок приоритета содержит четыре элемента И, схему сравнения, триггер и датчик приоритета, выход которого соединен с первым входом первого элемента И, выходом соединенного с первым входом схемы сравнения и аноду диода развязки, катод которого соединен с входом-выходом блока и вторым входом схемы сравнения, выход которой соединен с вторым выходом блока, выход второго элемента И соединен с вторым входом первого элемента И, первый вход с вторым входом блока и первым входом третьего элемента И, а второй вход - с выходом триггера, соотвтетствующие входы которого подключены к выходам третьего и четвертого элементов И, первый вход которого подключен к выходу схемы сравнения, а второй вход к второму входу третьего элемента И и первому выходу блока.

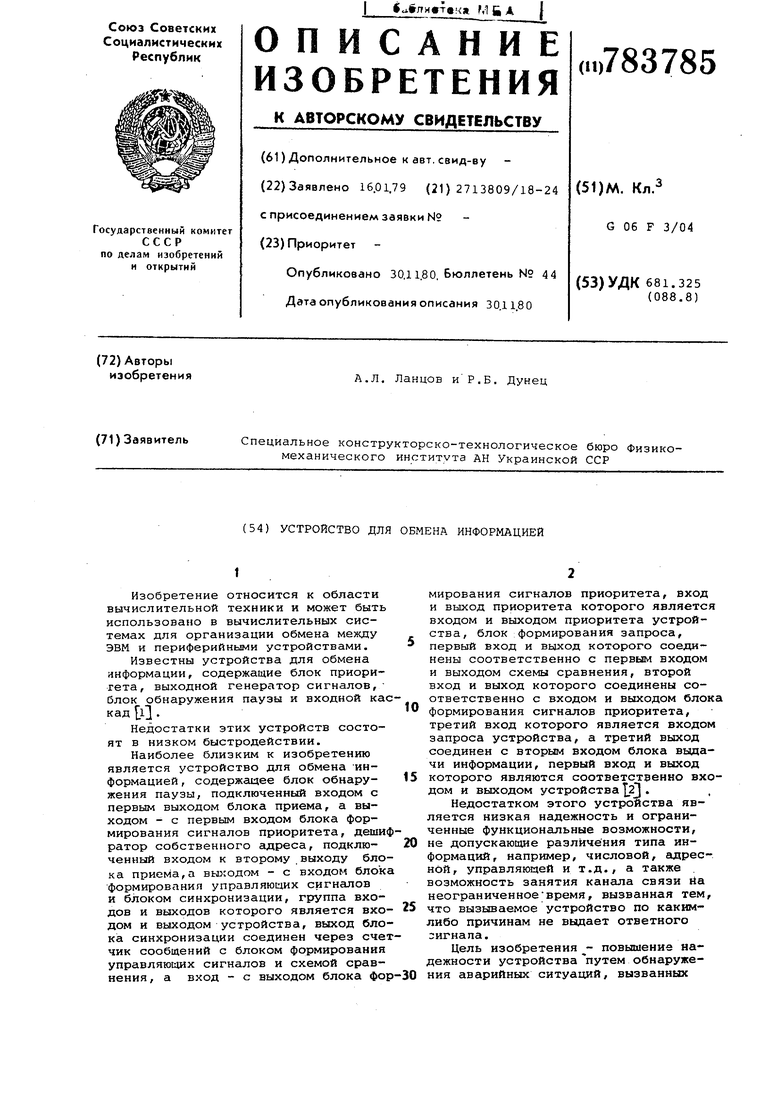

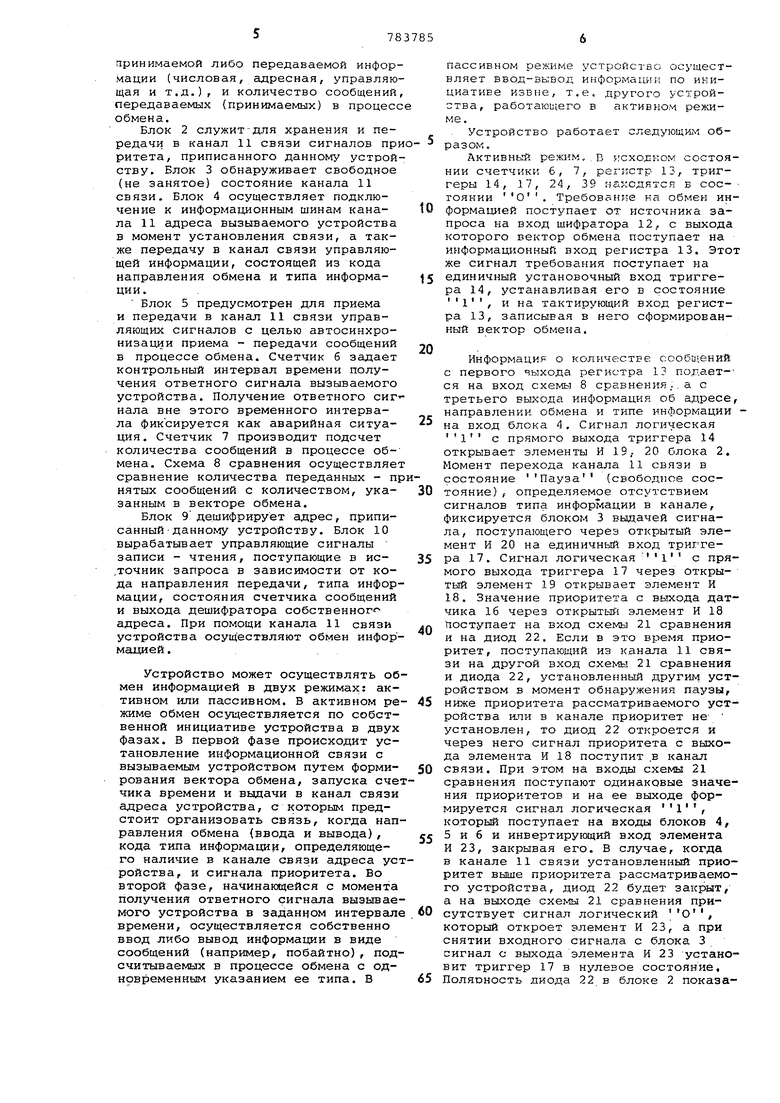

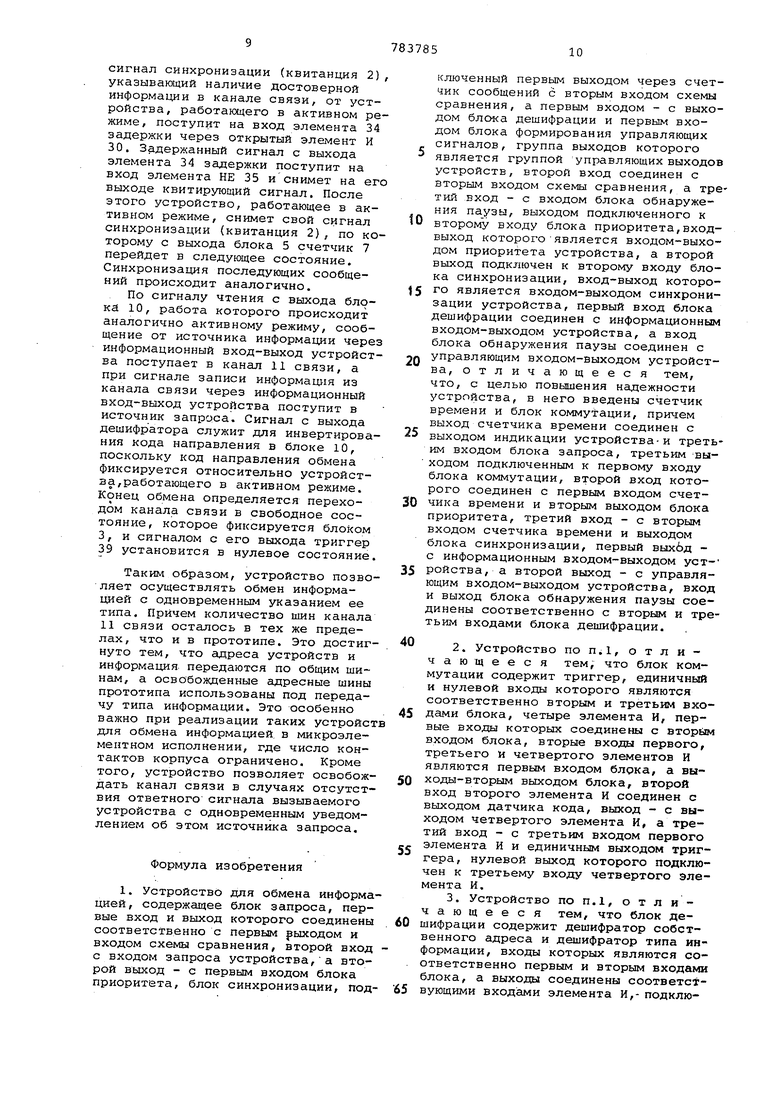

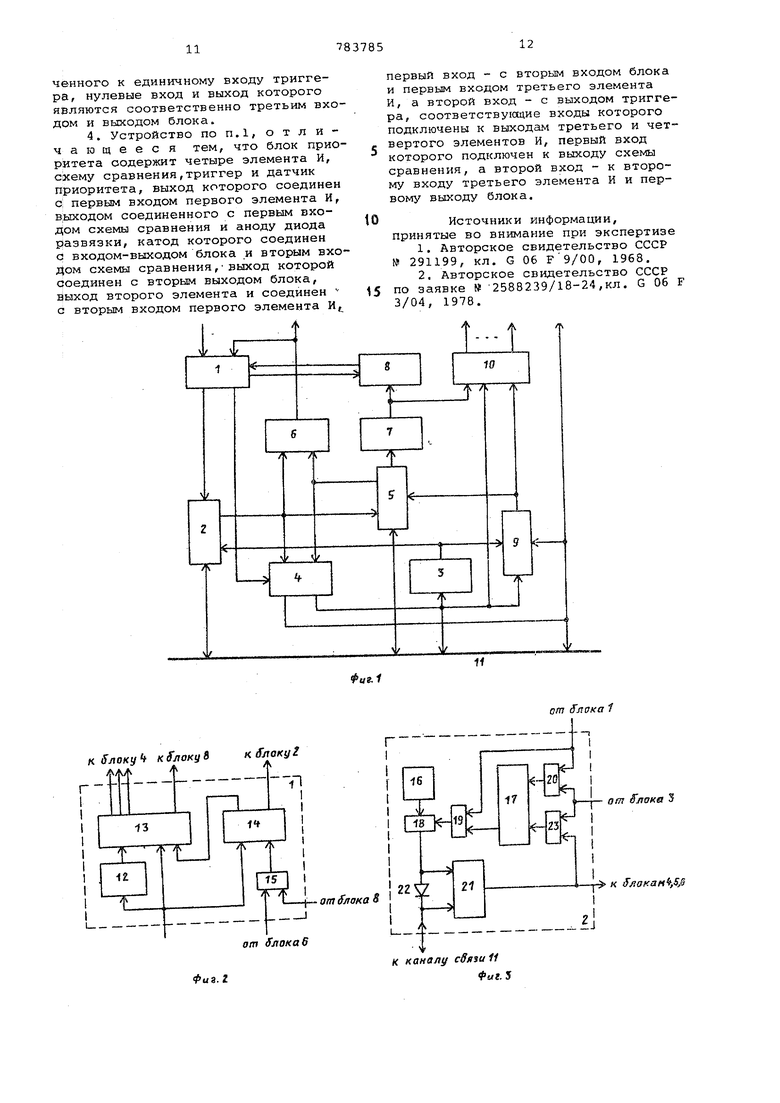

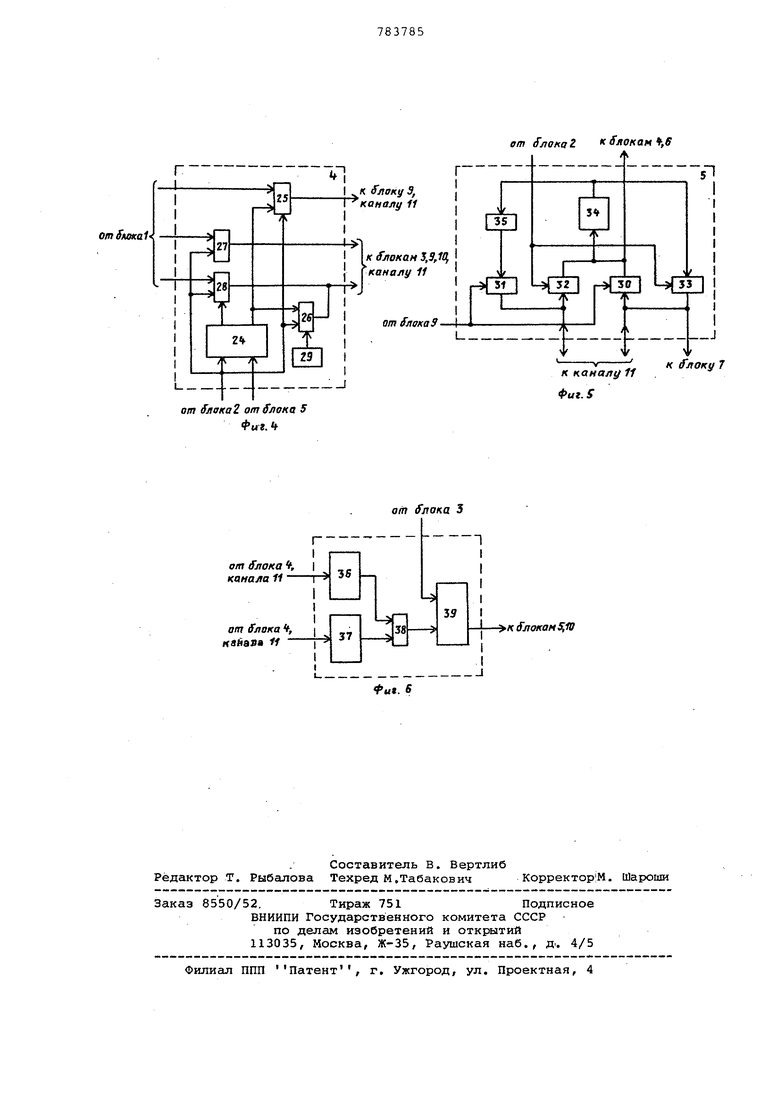

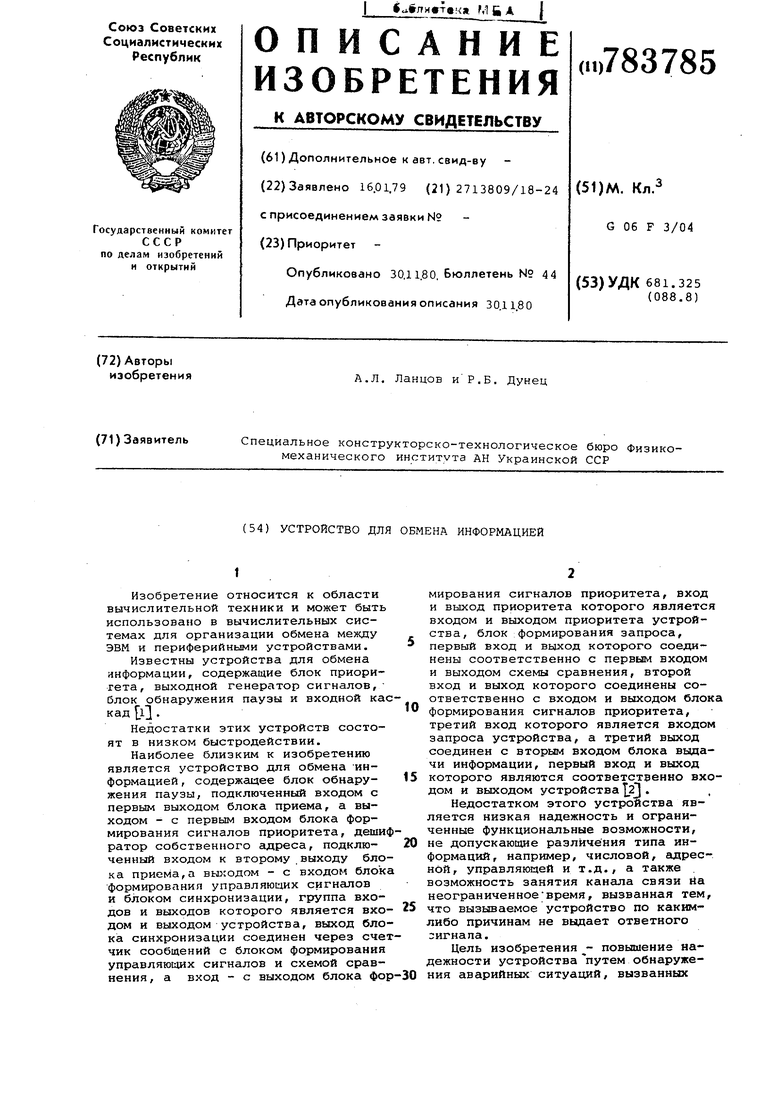

На фиг,1 приведена блок-схема прелагаемого устройства; на фиг,2-6 блок-схемы блока запроса, блока приоритета, блока коммутации, блока синхронизации и блока деишфрадии.

Устройство для обмена информацией содержит блок 1 запроса, блок 2 приоритета, блок 3 обнаружения паузы, блок 4 коммутации, блок 5 синхронизации, счетчик 6 времени, счетчик 7 сообщений, схему 8 сравнения,, блок 9 дешифрации, блок 10 управляющих сигналов и какал 3.1 связи.

Блок 1 включает шифратор , 12. вектора обмена, репстр 13 вектора обмена, триггер 14 и элемент ИЛИ 15,

Блок 2 содержит датчик 16 приоритета, триггер 17, элементы И 13,19, 20, схему 21 сравнения, диод 22 развязки и элемент И 23.

Блок 4 состоит из триггера 24, элементов И 25, 26, 27, 28 к датчика 29 кода.

Блок 5 включает элементы И 30, 31 32, 33, элемент 34 задержки, элемент НЕ 35.

Блок дешифрации содержит дешифратор 36 типа информацииf дешифратор 37 собственного адреса, элемент И 38 и триггер 39,

Блок 1 предназначен для формирования вектора обмена и сигнала запуска блока 2 по сигналу требования, поступающего от источника запроса. Вектор обмена представляет собой код, задающий адрес устройства,, с которым престоит обмен информацией, направление обмена (ввод или зьшод информация относительно данного устройстгза) , тип Принимаемой либо передаваемой информации (числовая, адресная, управляющая и т.д.), и количество сообщений передаваемых (принимаемых) в процесс обмена. Блок 2 служит-для хранения и передачи в канал 11 связи сигналов при ритета, приписанного данному устрой ству. Блок 3 обнаруживает свободное (не занятое) состояние канала 11 связи. Блок 4 осуществляет подключение к информационным шинам канала 11 адреса вызываемого устройства в момент установления связи, а также передачу в канал связи управляющей информации, состоящей из кода направления обмена и типа информации. Блок 5 предусмотрен для приема и передачи в канал 11 связи управляющих сигналов с целью автосинхронизации приема - передачи сообщений в процессе обмена. Счетчик б задает контрольный интервал времени получения ответного сигнала вызываемого устройства. Получение ответного сигнала вне этого временного интервала фиксируется как аварийная ситуация. Счетчик 7 производит подсчет количества сообщений в процессе обмена. Схема 8 сравнения осуществляет сравнение количества переданных - пр нятых сообщений с количеством, указанным в векторе обмена. Блок 9 дешифрирует адрес, приписанный- данному устройству. Блок 10 вырабатывает управляющие сигнсьлы записи - чтения, поступающие в ис.точник запроса в зависимости от кода направления передачи, типа информации, состояния счетчика сообщений и выхода дешифратора собственног--адреса. При помощи канала 11 связи устройства осуществляют обмен информадией. Устройство может осуществлять об мен информацией в двух режимах: активном или пассивном. В активном ре жиме обмен осуществляется по собственной инициативе устройства в двух фазах. В первой фазе происходит установление информационной связи с вызываемым устройством путем формирования вектора обмена, запуска сче чика времени и вьадачи в канал связи адреса устройства, с которым предстоит организовать связь, когда нап равления обмена (ввода и вывода), кода типа информации, определяющего наличие в канале связи адреса ус ройства, и сигнала приоритета. Во второй фазе, начинающейся с момента получения ответного сигнала вызывае мого устройства в заданном интервале времени, осуществляется собственно ввод либо вывод информации в виде сообщений (например, побайтно), под считываемых в процессе обмена с одновременным указанием ее типа. В пассивном режиме устройстве осуществляет ввод-вывод информации по инициативе извне, т.е. другого устройства, работающего в активном режиУстройство работает следующил1 образок. Активный режим..в }юхолном состоянии счетчики 6, 7, регистр 13, триггеры 14, 17, 24, 39 находятся в сое-Требование ка обмен ингоякииформацией поступает от источника запроса на вход шифратора 12, с выхода которого вектор обмена поступает на информационный вход регистра 13. Этот же сигнал требования поступает на единичный установочный вход триггера 14, устанавливая его в состояние , и на тактирующий вход регистра 13, записывая в него сформированный вектор обмена. Информация о кол1- честЕе сообиений с первого чыхода регистра 13 подает- ся на вход схемь 8 сравнения,., а с третьего выхода информация об адресе, направлении обмена и типе информации на вход блока 4. Сигнал логическая с прямого выхода триггера 14 открывает элементы И 19, 20 блока 2. Момент перехода канала 11 связи в состояние Пауза (свободное состояние) f определяемое отсутствием сигналов типа информации в канале, фиксируется блоком 3 выдачей сигнала, поступающего через открытый элемент И 20 на единичный вход триггера 17. Сигнал логическая с прямого выхода триггера 17 через открытый элемент 19 открывает элемент И 18. Значение приоритета с выхода датчика 16 через открыты 1 элемент И 18 поступает на вход схемы 21 сравнения и на диод 22. Если в это время приоритет, поступающий из канала 11 связи на другой вход схемы 21 сравнения и диода 22, установленный другим устройством в момент обнаружения паузы, ниже приоритета рассматриваемого устройства или в канале приоритет не установлен, то диод 22 откроется и через него сигнал приоритета с выхода элемента И 18 поступит .в канал связи. При этом на входы схемы 21 сравнения поступают одинаковые значения приоритетов и на ее выходе формируется сигнал логическая , который поступает на входы блоков 4, 5 и 6 и инвертиругощий вход элемента И 23, закрывая его. В случае, когда в канале 11 связи установленный приоритет выше приоритета рассматрИБа.емого устройства, диод 22 будет закрыт, а на выходе схемы 21 сравнения присутствует сигнал логический О, который откроет элемент И 23, а при снятии входного сигнала с блока 3 сигнал с выхода элемента И 23 установит триггер 17 в нулевое состояние. ПОЛЯРНОСТЬ диода 22 в блоке 2 показана для случая задания приоритетов н пряжением положительной полярности. Сигнал с выхода блока 2, поступа щий на первый вход счетчика 6, осуществляет запуск последнего для фор мирования контрольного интервала времени. Этот же сигнал поступает на первые входы элементов И 25-28 и на единичный устаковочный вход триггера 24 блока 4. При этом через от1 рытый элемент И 27 код напряжени обмена поступает в канал 11 связи, а триггер 24 переводится в состояние логическая . Сигнал с прямого выхода триггера открывает элементы И 25 и 26. Через открытый эле мент И 25 в канал 11 связи поступае адрес вызываемого устройства, а через открытый элемент И 26 в канал связи с датчика 29 пода.ется код (например, сигналы логическая i во всех разрядах кода), указывающий на то, что в канале связи передает ся адрес устройства, с которым пред стоит обмен информацией. Все осталь ные комбинацли логических О и в разрядах кода используются для указания различных типов передаваемой и принимаемой информации. Сигнал, поступающий на второй вход блока 5 с выхода блока 2, открывает элементы И 32 и 33. Сигнал синхронизации (квитанция 1), Приходящий через канал связи от устройства, распознавшего свой адрес, через открытый элемент И 32 поступ ет на вход элемента 34 задержки и второй выход блока. Сигнал с второ го выхода блока 5, поступающий на второй вход счетчика б, устанавливает его в исходное состояние, пре кращая тем саглым формирование контрольного интервала времени. Если этот сигнал не поступит на вход счетчика б до конца контрольного интервала времени, на выходе счетчика б сформируется с-игнал. лоуказывающий источгическаянику запроса на аварийную ситуацию. Длительность контрольного интервала времени задается с учетом всех возможных максимальных задержек в цепи приема, формирования и передачи сигнала синхронизации (кв танция 1). Кроме того, сигналом с выхода счетчика б через элемент ЮШ 15 .триггер 14 установится в нулево состояниеИ сигналом с инверсного выхода обнулит регистр 13, а сигна лом ,с прямого ВЕлхода запретит рабо ту блока 2, после чего устройство npi-одет в исходное состойние. Для повторного установления связи с вы зываемым устройством источник запр са должен вновь выдать сигнал запр с.а. Сигнал, поступающий с второго в хода блока 5 на нулевой установочн вход триггера 24 блока 4 установит его в нулевое состояние. При этом элементы И 25 и 26 закроются, элемент И 28 откроется. Через открытый элемент И 28 в канал 11 связи поступит код типа информации, которая подлежит обмену. Обмен информации каж,цого сообщения автосинхронизируется блоком 5 следующим образом. Сигнал синхронизации с выхода элемента И 32, задержанный на некоторое время с помощью элемента 34 задержки, поступает через открытый элемент И 33 в канал 11 связи в виде ответного сигнала синхронизации (квитанция 1). Снятие входного сигнала синхронизации (квитанции 1) вызывает снятие с задержкой ответного сигнала синхронизации. Кроме того, снятие сигнала синхронизации с первого выхода блока 5- вызывает перевод счетчика 7 в следующее состояние. В процессе обмена сигналами синхронизации блок 10 формирует управляющие сигналы записи, либо чтения в зависимости от направления обмена, типа информации и состояния счетчика 7. По сигналу чтения сообщение от источника информации через инфорг ационный вход-выход устройства поступит в канал 11 связи, а при сигнале записи сообщение из каналам связи - в источник запроса. Обмен сообщениями происходит до тех пор, пока количество сообщений, записанное в регистре 13, не сравнится с переданным количеством сообщений, подсчитывае1 «лм счетчиком 7. Момент равенства фиксируется схемой 8 сравнения. Сигнал с ее выхода, поступающий через элемент ИЛИ 15 блока 1,. установит триггер 14 в нулевое состояние, после чего сХема перейдет в исходное состояние аналогично случаю формирования сигнала аварии счетчиком б. На этом процесс обмена заканчивается . Пассивный режим. Исходное состояние устройства то же, что в активном режиме. При передаче в канале 11 связи кода типа информации, указывающего на наличие в канале адреса устройства, на выходе дешифратора 36 формируется сигнал логическая крывающий злемеат И 38. При появлении кода собственного адреса на информационном входе устройства дешифратор 37 формирует на выходе сигнал логическая , который через открытый элемент И 38 установит триггер 39 в единичное состояние, Сигнал логической- с выхода триггера 39 откроет элементы И 30 и 31. При этом сигнал синхронизации (квитанция 1) с выхода элемента НЕ 35 через элемент И 31 поступит в канал 11 связи. Через некоторое время

сигнал синхронизации (квитанция 2) указывакщий наличие достоверной информации в канале связи, от устройства, работанхдего в активном режиме, поступит на вход элемента 34 задержки через открытый элемент И 30. Задержанный сигнал с выхода элемента 34 задержки поступит на вход элемента НЕ 35 иснимет на его выходе квитирующий сигнал. После этого устройство, работающее в активном режиме, снимет свой сигнал синхронизации (квитанция 2), по которому с выхода блока 5 счетчик 7 перейдет в следующее состояние. Синхронизация последующих сообщений происходит аналогично.

По сигналу чтения с выхода блока 10, работа которого происходит аналогично активному режиму, сообщение от источника информации через информационный вход-выход устройства поступает в канал 11 связи, а при сигнале записи информация из канала связи через информационный вход-выход устройства поступит в источник запроса. Сигнал с выхода дешифратора служит для инвертирования кода направления в блоке 10, поскольку код направления обмена фиксируется относительно устройства, работающего в активном режиме. Конец обмена определяется переходом канала связи в свободное состояние , которое фиксируется блоком 3, и Сигналом с его выхода триггер 39 установится в нулевое состояние

Таким образом, устройство позволяет осуществлять обмен информацией с одновременным указанием ее типа. Причем количество шин канала 11 связи осталось в тех же пределах, что и в прототипе. Это достигнуто тем, что адреса устройств и информация передаются по общим шинам, а освобожденные адресные шины прототипа использованы под передачу типа информации. Это особенно важно при реализации таких устройс для обмена информацией в микроэлемеитном исполнении, где число контактов корпуса ограничено. Кроме того, устройство позволяет освобождать канал связи в случаях отсутствия ответного сигнала вызываемого устройства с одновременным уведомлением об этом источника запроса.

Формула изобретения

1. Устройство для обмена информацией, содержащее блок запроса, первые вход и выход которого соединены соответственно с первым рыходом и входом схемы сравнения, второй вход с входом запроса устройства,а второй выход - с первым входом блока приоритета, блок синхронизации, подключенный первым выходом через счетчик сообщений с вторым входом схемы сравнения, а первым входом - с выходом блока дешифрации и первым входом блока формирования управляющих сигналов, группа выходов которого является группой управляющих выходов устройств, второй вход соединен с вторым входом схемы сравнения, а третий вход - с входом блока обнаружения паузы, выходом подключенного к

0 второму входу блока приоритета,входвыход которого-является входом-выходом приоритета устройства, а второй выход подключен к второму входу блока синхронизации, вход-выход которо5го является входом-выходом синхронизации устройства, первый вход блока дешифрации соединен с информационным входом-выходом устройства, а вход блока обнаружения паузы соединен с управляющим входом-выходом устройст0ва, отличающееся тем, что, с целью повышения надежности устройства, в него введены счетчик времени и блок коммутации, причем выход счетчика времени соединен с

5 выходом индикации устройства-и третьим входом блока запроса, третьим выходом подключенным к первому входу блока коммутации, второй вход которого соединен с первым входом счет0чика времени и вторым выходом блока приоритета, третий вход - с вторым входом счетчика времени и выходом блока синхронизации, первый выхбд с информационным входом-выходом уст5ройства, а второй выход - с управляющим входом-выходом устройства, вход и выход блока обнаружения паузы соединены соответственно с вторым и третьим входами блока дешифрации.

0

2.Устройство ПОП.1, отличающееся тем, что блок коммутации содержит триггер, единичный и нулевой входы которого являются соответственно вторым и третьим вхо5дами блока, четыре элемента И, первые входы которых соединены с вторим входом блока, вторые входы первого, третьего и четвертого элементов И являются первым входом блрка, а выходы-вторым выходом блока, второй

0 вход второго элемента И соединен с выходом датчика кода, выход - с выходом четвертого элемента И, а третий вход - с третьим входом первого элемента И и единичным выходом триг5гера, нулевой выход которого подключен к третьему входу четвертого элемента И.

3.Устройство по п.1, отличающееся тем, что блок де0шифрации содержит дешифратор собственного адреса и дешифратор типа информации, входы которых являются соответственно первым и вторым входают блока, а выходы соединены соответст5вующими входами элемента И,- подключенного к единичному входу триггера, нулевые вход и выход которого являются соответственно третьим входом и выходом блока.

4. Устройство ПОП.1, отличающееся тем, что блок приоритета содержит четыре элемента И, схему сравнения,триггер и датчик приоритета, выход которого соединен с. первым входом первого элемента И, вдаодом соединенного с первым входом схемы сравнения и аноду диода развязки, катод которого соединен С входом-выходом блока и вторым входом схемы сравнения, выход которой соединен с вторым выходом блока, выход второго элемента и соединен с вторым входом первого элемента И,

первый вход - с вторым входом блока и первым входом третьего элемента И, а второй вход - с выходом триггера, соответствугадие входы которого подключены к выходам третьего и четвертого элементов И, первый вход которого подключен к выходу схемы сравнения, а второй вход - к второму входу третьего элемента И и первому выходу блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 291199, кл. G 06 F9/OO, 1968.

2,Авторское свидетельство СССР по заявке 2588239/18-24,кл. G Об 3/04, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией | 1978 |

|

SU723560A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Многоканальное устройство сопряжения | 1976 |

|

SU679973A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

KSnoKyt к fлаку 8 к. fлаку

АЛА

в т fjioKei S

к Sf.OHSHtf,

Фиа. I

к каналу связи 11 Фиг. 5

OiaSuiKal

от fjioKoZ от Улока 5 ФигЛ

от fлаки г к блокам t,S к. SnoKg 9, каналу 11 к fjtoKuH У,3,Ц каналу 11 от /лека 9

агп fлaкa 3

кfлoкaн Ю к к.анал{/ И Фиг.К

Авторы

Даты

1980-11-30—Публикация

1979-01-16—Подача