(54) ПРЕОБРАЗОВАТЕЛЬ КОД-АНАЛОГ

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЕНТИЛЬНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1991 |

|

RU2064730C1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Преобразователь постоянного напряжения в переменное программируемой формы с блоком управления | 1982 |

|

SU1019566A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

| Устройство для импульсно-фазового управления тиристорным преобразователем | 1982 |

|

SU1042153A1 |

| Автоматический измеритель импульсной мощности СВЧ радиосигналов | 1985 |

|

SU1287025A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов | 1985 |

|

SU1305856A1 |

1

Предлагаемый преобразователь коданалог предназначен для использования в автоматизированных системах управления технологическими процессами (АСУТН), в частности для управления 5 объектами с малой инерционностью.

Известны преобразователи код-мощность , соетоя1цие из преобразователя код-напряжение и тиристорного усилителя (бло.ка управления тиристбром)

(дд и

Недостаток этих преобразователей заключается в низком быстродействии, в пределе, ограниченном длительностью полупериода сетевого напряжения. Этот 15 недостаток особенно сильно проявляется при управлении об1 ектами с мгшой инерционностью.

Наиболее близким по технической 20 сущности к изобретению является преобразователь код-мощность, содержащий источник переменного напряжения, соединенный со йходом блока синхронизации, задатчик кода, выходы которого 25 подключены к первым входам входных вентилей, триггер, выход которого связан со входом блока запуска тиристоров, выход которого роединен с тиристорным блоком, счетчик, элементы за- ЗО

держки, генератор импульсов и элемент И ГЗ.

Недостатком данного преобразовате-. ля, так же как и аналогов, является низкое быстродействие.

Цель изобретения - повышение быстродействия преобразователя.

Быстродействие преобразователя повышается тем, что полупериод сетевого напряжения (минимально возможный период управлений тиристорами для схем аналогов и прототипа) делится на N частей, каждая из которых и является периодом управления тиристорами IB предлагаемом преобразователе.. При этом быстродействие преобразователя повышается в N раз. Длительности этих периодов выбираются различными из условия выполнения равенства максимгшьных мощностей, выделяемых в каждом периоде. Число же импульсов квантования в периодах задается постоянным, а квантования - различным для каж дого периода.

Поставленная цель достигается за счет того, что в преобразователь код- . аналог, содержащий источник переменното, напряжения, соединенный со входом блока синхронизации, задатчик кода, выходы которого подклк)Чены к первым

входам входных переключающих элементов, управляющий триггер, выход которого соединен со входом блока запуска тиристоров, выход которого соединен с блоком формирования выходного сигнала, счетчик, элементы задержки, генеjpaTop импульсов и элемент И, введены -Н,« счетчик и блок выбора шага квантования, первый вход которого соедин н с выходом генератора импульсов второй - с выходом блока синхронизации Ис первым входом масштабного счетчика, а выход - с первым входом счетчика и первым входом масштабного счетчика, выход которого через первый элемент задержки связан со вторым входом входных переключающих элементов, а через второй элемент задержки - с перрым входом управляющего триггера и третьим входом блока выбора шага квантования, выход счетчика через элемент И соединен со вторым входом управлякяцего триггера.

Кроме того, блок выбора шага квантования вьтолнен из счетчика, элемента И, ключевых элементов, элемента задержки, блока памяти, элемента ИЛИ и счетчика адреса. Первый вход счетчика соединен с первым входом блока выбора шага квантования, а выход через З: л емент И - с выходом блока выбора Шага квантования и с первым входом элемента ИЛИ. Первый вход, счетчика ад раса соединен со вторым входом блока выбора шага квантования, второй входсо вторым входом элемента ИЛИ и треTbstM входом блока выбора шага квантования, а выход - со входом блока памяти, выходами подключенного к первым входам ключевых элементов, выходы которых соединены со вторыми входами счет сика. Выход элемента ИЛИ соединен через элемент задержки со вторыми BXO дами ключевых элементов.

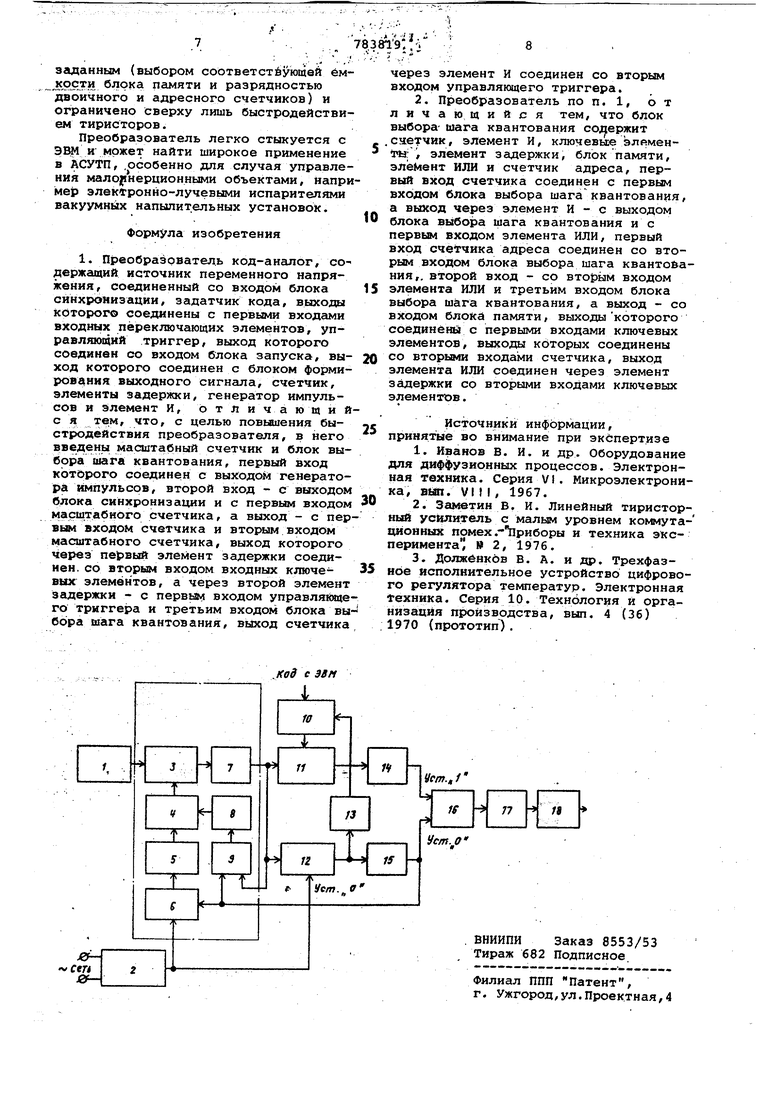

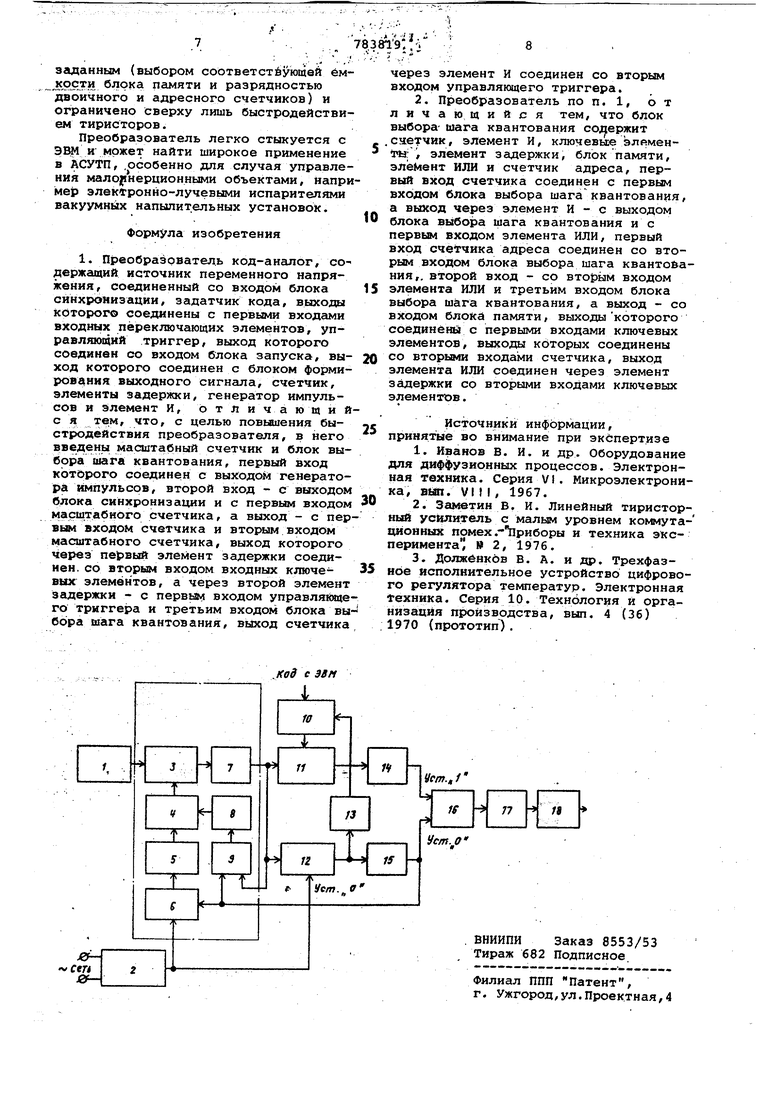

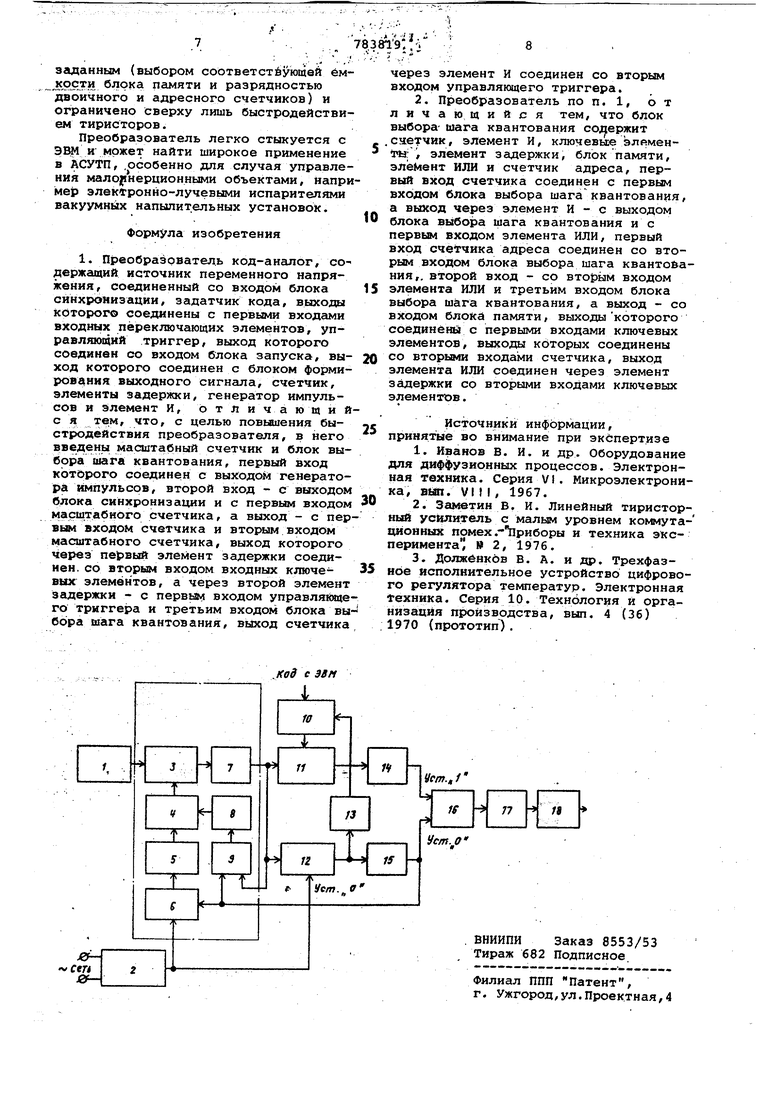

На чертеже представлена структурная схема преобразователя код-аналог.

Преобразователь код-аналог содержит генератор 1 импульсов, блок 2 синхронизации, блок выбора шага квантова ния, который состоит издвоичного счетчика 3, ключевого элемента 4, блока 5 памяти, счетчика б адреса, элемента И 7, элемента 8 задержки, элемента ИЛИ 9, входные ключевые элементы 10, двоичный счетчик 11, масштабный счетчик 12, элемент 13 задержки, элемент И 1.4, элемент 15 згшержки, управляющий триггер 16 с раздельными 4в; содами , блок 17 запуска, блок 18 формирования выходного сигнала.

Управляющий сигнал в виде параллелного двоичного кода подается на входные ключевые элементы 10, причем максимальный код соответствует максималь ной выходной мощности за период, который задается масштабным счетчиком 12. .

Входное сетевое напряжение поступает на вход блока 2 синхронизации ,

который формирует импульсы в момент, перехода сетевого напряжения через нулевое значение. Эти импульсы проходят на вход установки в нуль масштабного счетчика 12, который устанавливается в исходное состояние и на его выходе вырабатывается сигнал, который поступает на элементы 13 и 15 задержки. Одновременно импульсы с блока 2 синхронизации поступают на вход синхронизации блока выбора шага квантования, а именно на вход установки в нуль счетчика б адреса, который сбрасывается, в состояние готовности.

Импульс с выхода элемента 13 задержки поступает на входные ключевые элементы 10, ив двоичном счетчике 11 производится запись кода управлякицего сигнала. Импульс с выхода элемента 15 задержки подается на один из входов управляющего триггера 16 и устанавливает его в нуль/ т. е. выключает блок 17. Одновременно импульс с элемента

15задержки поступает на вход триггера 16, который устанавливает начало периода управления, и на вход блока выбора шага квантования, а именно на счетный вход счетчика б адреса и на один из входов элемента ИЛИ 9. Счетчик б адреса воздает сигнал на вход блока 5 памяти,и на его выходе появляется код, соответствующий длительност шага квантования в первом периоде, управления формированием выходного сигнала. Импульс с элемента ИЛИ 9 через элемент В задержки проходит на ключевые элементы 4/ и в двоичном счетчике

3 происходит запись кода шага квантования первого периода управления формированием выходного .

Элементы 13 и 15 задержки вводятся в схему преобразователя для устранения неопределенных состояний триггера

16с раздельными входами в случаях, когда.управляющий код имеет все нули или единицы. Элемент 8 задержки вводися в схему преобразователя для правилной работы блока выбора шага квантования. Время задержки элемента 8 выбирается меньше времени задержки элемента 15, которое, в свою очередь, меньше времени задержки элемента 13.

. Импульсами от генератора 1, которы подаются на вход блока выбора шага квантования-, а именно на счетный вход двоичного счетчика 3, происходит дополнение кода длительности шага квантования первого периода управления до максимального. В момент заполнения двоичного счетчика 3 срабатывает элемеНт И 7. Импульс с него поступает на другой вход элемента ИЛИ 9. Элемент ИЛИ 9 вырабатывает импульс, который через элемент 8 задержки проходит на ключевые элементы 4, и в Двоичном счетчике 3 пpoиcxoдиf запись кода шага квантования первого периода управления тиристорами. Этот процесс повторявтся до тех пор, пока не кончится этот период управления тиристорами.

Одновременно сигнал с элемента И 7, аыход которого является выходом блока выбора шага квантования, поступает на счетные входы двоичного счетчика 11 и масштабного счетчика 12. Импульсами с элемента И 7 происходит дополнение кода управляющего сигнала. В момент заполнения двоичного счетчика 11 срабатывает элемент И 14. Импульс с элемента И 14 поступает на другой вход триггера 16 и опрокидывае его. Триггер 16 включает блок 17 згшуска, который формирует импульсы управления блока 18 формирования выходного сигнала до тех пор, пока на первый вход триггера 16 через элемент 15 задержки не поступит импульс окончания периода управления блоком 18 с масш-. .табного счетчика 12.

Импульсы с выхода ма1сштабного счетчика 12 через элемент 13 задержки подаются на входные ключевые элементы 10, открывают их, и в двоичном .счетчике 11 происходит запись кода управляющего сигнала. Одновременно импульс окончания периода управления с масштабного счетчика 12 через элемент 15 задержки поступает на блок выбора шага квантования, а именно на элемент ИЛИ 9 и на счетчик 6 адреса. Счетчик 6 адреса выбирает сигнал на вход блока 5, и на его выходе появляется код, соответстйукяций длительности шага квантования во йтором периоде управления тиристорами. Импульс с элемента ИЛИ 9 через элемент 8 задержки поступает на ключевые элементы 4 , ив двоичном счетчике 3 происходит запись кода длительности шага квантования второго периода управления.

Импульсами от генератора 1, которые подаются на вход блока выбора шага квантования, а именно на счётный вход двоичного счетчика 3, происходит дополнение кода длительности шага квантования второго периода управЛения до максимального. -В момент заполнения двоичного счетчика 3 срак5атывает элемент И 7. Импульс с него через элемент ИЛИ 9 и элемент 8 задержки поступает на элементы 4, и в двоичном счетчике 3 происходит запись кода шага квантования. Этот процесс повторяется до конца второго периода управления, рдновременно импульсы с элемента И 7 поступают на двоичный счетчик 11 и дополняют код управляющего сигнала до максимального, а также на. масштабный счетчик 12, которьай формирует второй период управления тиристорами.

В момент заполнения двоичного сЧёт чика 11 срабатывает элемент И 14. Сигнал с него поступает на триггер 16 и опрокидывает его, тем самым запуская тиристоры в тиристорном блоке 18. Тригер 16 остается в Таком положении до

тех пор, пока на его вход с масштабного счетчика 12 через элемент 15 задержки не поступит импульс окончания второго перйода управления.

Этот же импульс через элемент 13 задержки открывает входные элементы 10, ив двоичном счетчике 11 происходит запись кода управляющего сигнала. Одновременно через элемент 15 задерж-; ки импульс окончания второго периода управления поступает на вход установки начала периода управления, а имеино на,счетный вход счетчика б адреса, который, в свою очередь подает сигнал блоку 5 на выдачу кода длительности Вага квантования Трётьегб пёрйода Уп-равления и т. д.

Этот процесс в преобразователе повторяется до тех пор, ПОКА блок 5 памяти не выдаст последний код шага квантования в последнем периоде управления формированием выходного сигнала. Окончание последнего периода управления совпадает с моментом перехода сетевого напряжения через нулевое значение. В этот момент импульс с блока 2 синхронизации устанавливает в исходное состояние блок выбора шага квантования, т. е. сбрасывает счетчик 6 адреса и масштабный счетчик 12 в состояние готовности.

Работа преобразователя в следующем полупериоде сетевого напряжения аналогична описанной.

Для правильной работы преобразователя разрядность Q двоичного счетчика 11 должна быть равна разрядности масштабного счетчика 12 и. выбирается из условия

2- СЯ,

где сГ - погрешность квантования периода управления.

Разрядность Р двоичного счетчика 3 Ьпределена числом импульсов L генератора 1 импульсов, укладывающихся в максймальном шаге квантования, т. е.

.

Разрядность S счетчика :б адреса связана с числЬм периодов управления в полупериоде сетевого напряжения неравенством:

N.

Частота f,,. генератора 1 импульсов находится из, соотношения

h, t woiKu/

ти

где Скд - длительность максимального шага квантования. ;

Предлагаемый преобразователь кодаНалог выгодно отличается от аналогов и прототипа своим быстродействием, которое легко может быть сделано любым

Авторы

Даты

1980-11-30—Публикация

1979-01-04—Подача