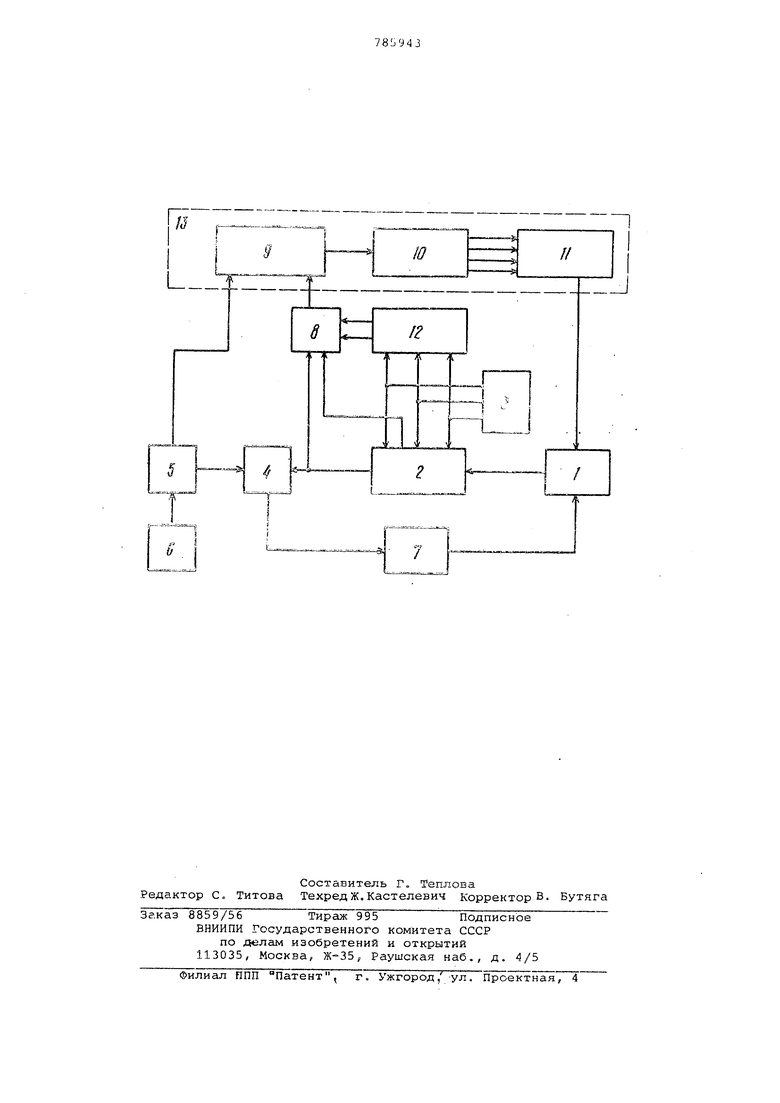

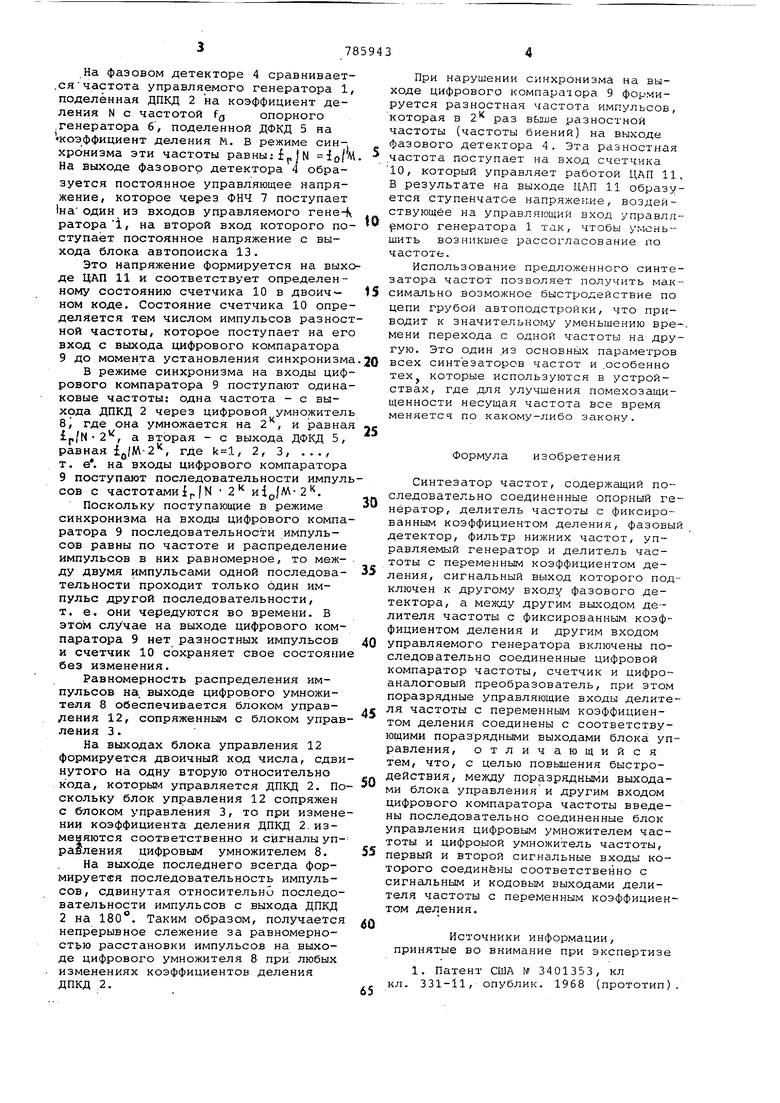

(54) СИНТЕЗАТОР ЧАСТОТ Изобретение относится к радиотех- нике и может использоваться в приеме/передающих и контрольно-измерительных устройствах. Известен синтезатор частот/ содержащий последовательно соединенные опорный генератор, делитель частоты с фиксированным коэффициентом деления фазовый детектор, фильтр нижних частот (ФНЧ) , управляемый генератор и де литель частоты с переменным коэффициентом деления, сигнальный выход которого подключен к другому входу фазо вого детектора, а между другим выходом делителя частоты с фиксирован.ным коэффициентом деления и другим входом управляемого генератора включены последовательно соединенные цифровой компаратор частоты, счетчик и Цифроаналоговый преобразователь (ЦАП) при этом поразрядные управляющие входы делителя частоты, с переменным коэффициентом деления соединены с соответствующими поразрядными выходами блока управления Ij . Однако известный синтезатор частот обладает невысоким быстродействием. Цель изобретеия - повышение быст.родействия. Для этого в известном синтезаторе частот ме)оду поразрядными выходами блока управления и другим входом цифрового компаратора частоты введены последовательно соединенные блок управления цифровым умножителем, частоты и цифровой умножитель частоты, первый и Второй сигнальные входы которого соединены соответственно с сигнальным и кодовым выходами делителя частоты с переменным коэффициентом деления. На чертеже приведена структурная электрическая схема предложенного синтезатора частот. Синтезатор частот содержит управляемый генератор 1, делитель частоты С переменным коэффициентом деления (ДПКД) 2, блок управления 3, фазовый детектор 4, делитель частоты с фиксированным коэффициентом деления (ДФКД) 5, опорный генератор 6, ФНЧ 7, цифровой умножитель 8 частоты, цифровой компаратор 9 частоты, счетчик 10, ЦАП 11, блок управления 12, цифровым умножителем частоты. Цифровой компаратор 9, счетчик 10 и ЦАП 11 составляют блок автопоиска 13. Синтезатор частот работает следу ющим образом. На фазовом детекторе 4 сравнивает,сячастота управляемого генератора 1, поделённая ДПКД 2 на коэффициент деления N с частотой f/i опорного .генератора 6, поделенной ДФКД 5 на «коэффициент деления М. В режиме син-, хрониэма эти частоты равны: f,,|N 1о/М На выходе фазового детектора 4 образуется постоянное управляющее напряжение, которое через ФНЧ 7 поступает на один из входов управляемого генеpaTopai, на второй вход которого поступает постоянное напряжение с выхода блока автопоиска 13. Это напряжение формируется на выхо де ЦАП 11 и соответствует определенному состоянию счетчика 10 в двоичном коде. Состояние счетчика 10 определяется тем числом импульсов разност ной частоты, которое поступает на его вход с выхода цифрового компаратора 9 до момента установления синхронизма В режиме синхронизма на входы цифрового компаратора 9 поступают одина ковые частоты: одна частота - с выхода ДПКД 2 через цифровой умножитель 8| где она умножается на 2, и равная /N2, а вторая - с выхода ДФКД 5, равная ij /M-2f где k l, 2, 3, ..., т. е. на входы цифрового компаратора 9 поступают последовательности импул сов с частотами 1р (N 2 и1р/М-2. Поскольку поступающие в режиме синхронизма на входы цифрового компа ратора 9 последовательности импульсов равны по частоте и распределение импульсов в них равномерное, то межДУ двумя импульсами одной последовательности проходит только один импульс другой последовательности, т. е. они чередуются во времени. В этом случае на выходе цифрового компаратора 9 нет разностных импульсов и счетчик 10 сохраняет свое состояни без изменения. Равномерность распределения импульсов на. выходе цифрового умножителя 8 обеспечивается блоком управления 12, сопряженным с блоком управ ления 3. На выходах блока управления 12 формируется двоичный код числа, сдви нутого на одну вторую относительно кода, которым управляется ДПКД 2. По скольку блок управления 12 сопряжен с блоком управления 3, то при измене нии коэффициента деления ДПКД 2. изменяются соответственно и сигналы управления цифровым умножителем 8. На выходе последнего всегда формируется последовательность импульсов, сдвинутая относительно последовательности импульсов с выхода ДПКД 2 на 180°. Таким образом, получается непрерывное слежение за равномерностью расстановки импульсов на выходе цифрового умножителя 8 при любых . изменениях коэффициентов деления ДПКД 2. При нарушении синхронизма на выходе цифрового компараюра 9 формируется разностная частота импульсов, которая в 2 раз выше разностной частоты (частоты биений) на выходе фазового детектора 4. Эта разностная частота поступает на вход счетчика 10, который управляет работой ЦАП 11, В результате на выходе ЦАП 11 образуется ступенчатое напряжен.ие, воздействующее на управляющий вход управлярмого генератора 1 так, чтобы уменьшить BOSHHKiiJee рассогласование по частоте. Использование предложенного синтезатора частот позволяет получить максимально возможное быстродействие по цепи грубой автоподстройки, что приводит к значительному уменьшению вре-. мени перехода с одной ч-астоты на другую. Это один из основных параметров всех синтезаторов частот и .особенно тех которые используются в устройствах, где для улучшения помехозащищенности несущая частота все время меняетсч по какому-либо закону. Формула изобретения Синтезатор частот, содержащий последовательно соединенные опорный генератор, делитель частоты с фиксированным коэффициентом деления, фазовый детектор, фильтр нижних частот, управляемый генератор и делитель частоты с переменным коэффициентом деления, сигнальный выход которого подключен к другому входу фазового детектора, а между другим выходом делителя частоты с фиксированным коэффициентом деления и другим входом управляемого генератора включены последовательно соединенные цифровой компаратор частоты, счетчик и цифроаналоговый преобразователь, при этом поразрядные управляющие входы делителя частоты с переменным коэффициентом деления соединены с соответствующими поразрядными выходами блока управления, отличающийся тем, что, с целью повышения быстродействия, между поразрядными выходами блока управления и другим входом цифрового компаратора частоты введены последовательно соединенные блок управления цифровым умножителем частоты и цифроыой умножитель частоты, первый и второй сигнальные входы которого соединены соответственно с сигнальным и кодовым выходами делителя частоты с переменным коэффициентом деления. Источники информации, принятые во внимание при экспертизе 1. Патент США №3401353, кл кл. 331-11, опублик. 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2416158C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Синтезатор частот с широкополосной модуляцией | 2019 |

|

RU2713569C1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2440668C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2009 |

|

RU2395899C1 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

Авторы

Даты

1980-12-07—Публикация

1979-01-10—Подача