(54) ТРИГГЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Триггер | 1987 |

|

SU1437969A2 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| Счетный триггер на МДП-транзисторах | 1982 |

|

SU1026291A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1985 |

|

SU1298766A1 |

| Устройство раздельного управления вентильными группами преобразователя частоты для асинхронного электропривода | 1988 |

|

SU1545305A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| Инжекционный к-триггер | 1977 |

|

SU705647A1 |

1

Изобретение относится к радиоэлектронике, может быть использовано в вычислительной, импульсной и измерительной технике.

Известен триггер, построенный на восьми логических элементах И-НЕ (ИЛИ-НЕ), содержащий основной и вспомогательный RSтриггеры tl). В этом триггерном устройстве основной RS-триггер переключается по фронту (срезу), a вспомогательный RS-триггер переключается по срезу.

Известен также синхронньш JK-триггер, построенный на восьми логических элементах И-гНЕ по схеме MS с запрещающими связями (2}.

Известные устройства обладают следующими недостатками:

на тех же логических элементах, что и сам триггер, так как на время переклююния одного логического элемента на инверсном и прямом выходах, триггера одновременно действуют два сигнала логической единицы, если

10 триггер построен на логических элементах И-НЕ или логического нуля, если триггер построен на логических элементах ИЛИ-НЕ. Это сужает функциональные возможности устройства.

15

Цель изобретения - повышение быстродействия, увеличение нагрузочной способности и расширение функциональных возможностей устройства.

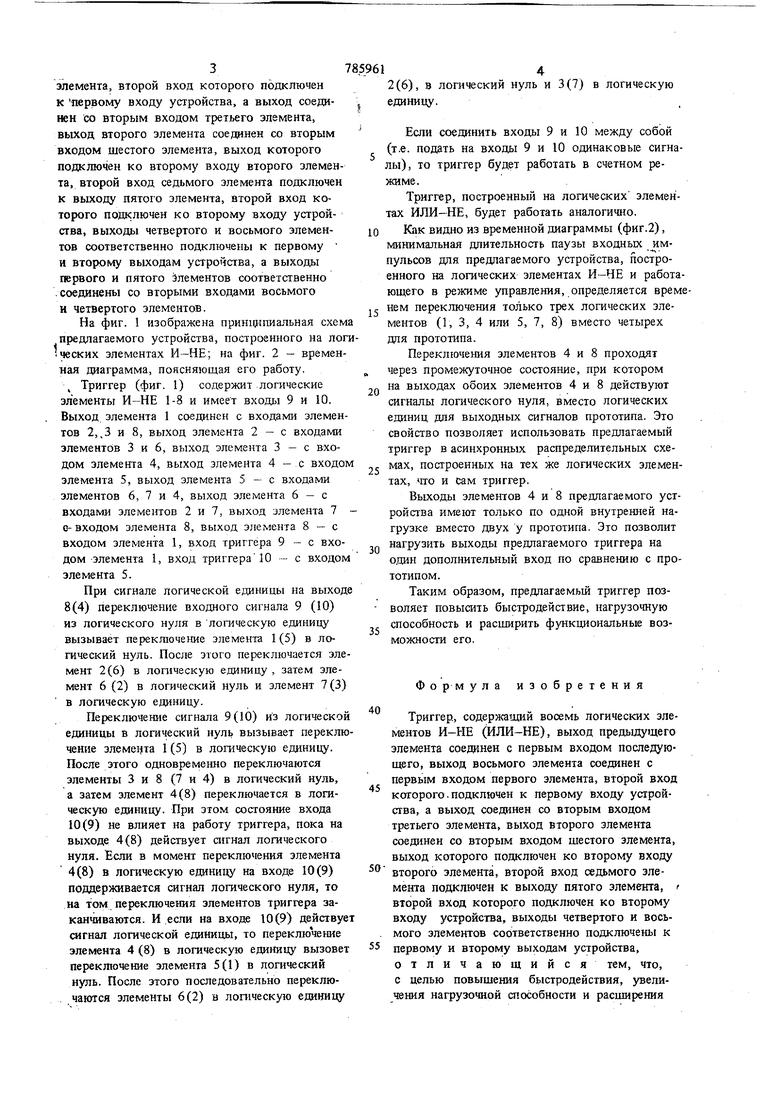

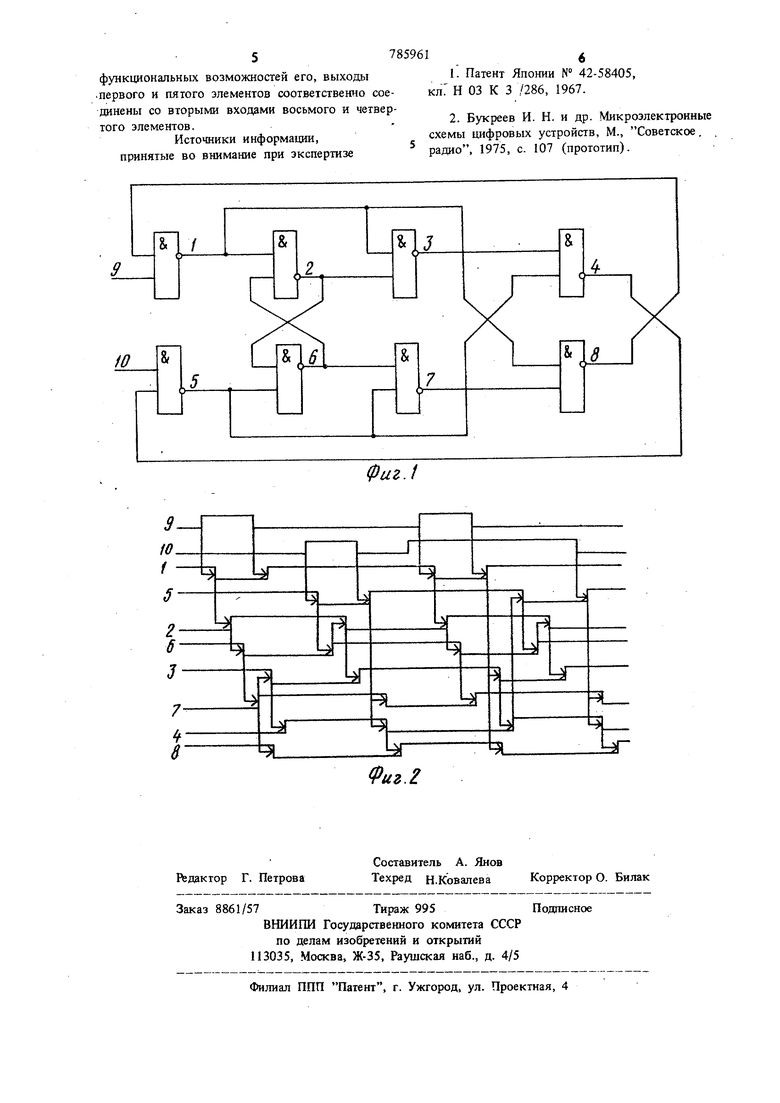

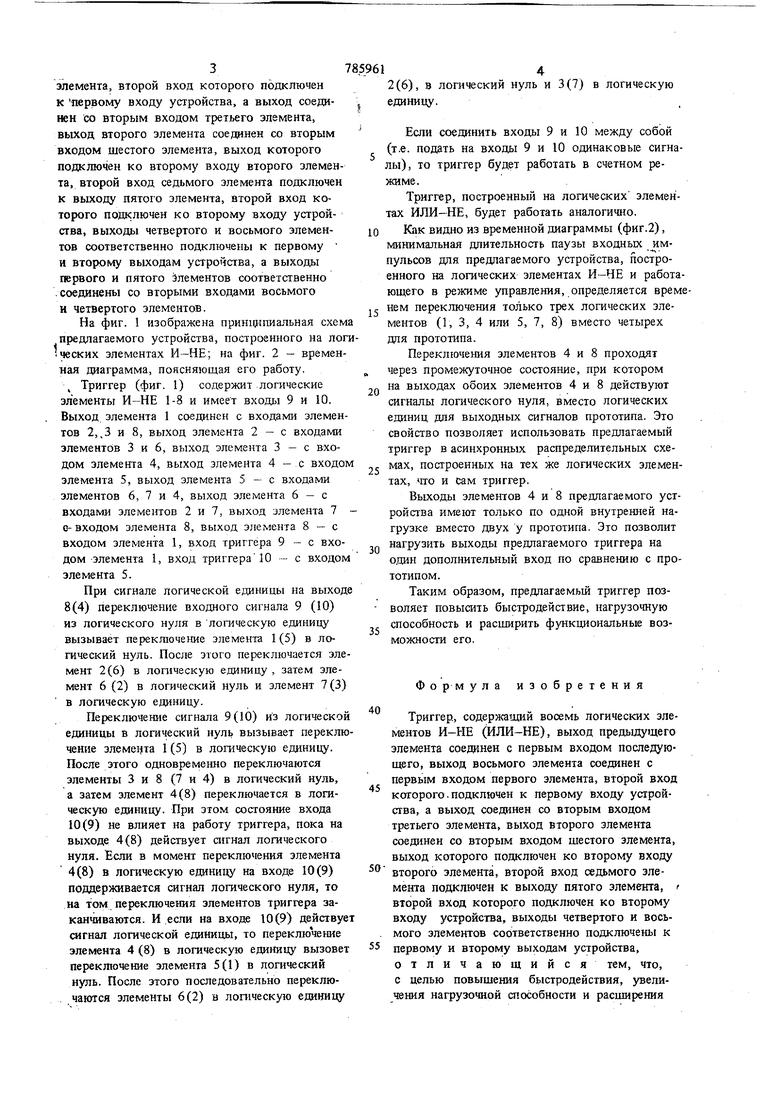

Дяя этого в устройстве, содержащем во20семь логических элементов И-НЕ (ИЛИ-НЕ), выход предыдущего элемента соединен с первым входом последующего, выход восьмого элемента соединен с первым входом первого элемента, второй вход которого подключен к первому входу устройства, а выход соединей со вторым входом третьего элемента, выход второго элемента соединен со вторым входом шестого элемента, выход которого подключен ко второму входу второго элемента, второй вход седьмого элемента подключен к выходу пятого элемента, второй вход которого подключен ко второму входу устройства, выходы четвертого и восьмого элементов соответственно подключены к первому и второму выходам устройства, а выходы первого и пятого Элементов соответственно соединены со вторыми входами восьмого и четвертого элементов. На фиг. 1 изображена принщгпиальная схем предлагаемого устройства, построенного на ло ческих элементах И-НЕ; на фиг. 2 - времен ная диаграмма, поясняющая его работу. , Триггер (фиг. 1) содержит логические элементы И-НЕ 1-8 и имеет входы 9 и 10. Выход элемента 1 соединен с входами элемен тов 2,,3 и 8, выход элемента 2-е входами элементов 3 и 6, выход элемента 3-е входом элемента 4, выход элемента 4 - ,с входо элемента 5, выход элемента 5 - с входами элементов 6, 7 и 4, выход элемента 6 - с входами элементов 2 и 7, выход элемента 7 с-входом элемента 8, выход элемента 8 - с входом элемента 1, вход триггера 9 - с входом -элемента 1, вход триггера10 - с входом элемента 5. При сигнале логической единицы на выход 8(4) переключение входного сигнала 9 (10) иэ логического нуля в логическую единину вызывает переключе1ше элемента 1 (5) в логический нуль. После этого переключается эле мент 2(6) в логическую единицу , затем элемент 6 (2) в логический нуль и элемент 7(3) в логическую единицу. Переключение сигнала 9(10) из логическо единицы в логический нуль вызывает переклю чение элемента 1 (5) в логическую единицу. После этого одновременно переключаются элементы 3 и 8 (7 и 4) в логаческий нуль, а эатем элемент 4(8) переключается в логическую единицу. При этом состояние входа 10(9) не влияет на работу триггера, пока на выходе 4(8) действует сигнал логического нуля. Если в момент переключения элемента 4(8) в логическую единицу на входе 10(9) поддерживается сигнал логического нуля, то на том переключения элементов триггера заканчиваются. И если на входе 10(9) действуе сигнал логической единицы, то переключение элемента 4 (8) в логическую единицу вызовет переключение элемента 5(1) в логаческий нуль. После этого последовательно переклю. чаются элементы 6(2) в логаческую единицу 4 2(6), в логический нуль и 3(7) в логическую единицу. Если соединить входы 9 и 10 между собой (т.е. подать на входы 9 и 10 одинаковые сигналы), то триггер будет работать в счетном режиме. Триггер, построенный на логических элементах ИЛИ-НЕ, будет работать аналогично. Как видно из временной диаграммы (фиг.2), минимальная длительность паузы входных импульсов для предлагаемого устройства, построенного на логических элементах И-НЕ и работающего в режиме управления, определяется временем переключения только трех логических элементов (1, 3, 4 или 5, 7, 8) вместо четырех для прототипа. Переключеьшя элементов 4 и 8 проходят через промежуточное состояние, при котором на выходах обоих элементов 4 и 8 действуют сигналы логического нуля, вместо логических единиц для выходных сигналов прототипа. Это свойство позволяет использовать предлагаемый триггер в асинхронных распределительных схемах, построенных на тех же логических элементах, что и сам триггер. Выходы элементов 4 и 8 предлагаемого устройства имеют только по одной внутренней нагрузке вместо двух у прототипа. Это позволит нагрузить выходы предлагаемого триггера на одан дополнительный вход по сравнению с прототипом. Таким образом, предлагаемый триггер позволяет повысить быстродействие. Нагрузочную способность и расширить функциональные возможности его. Формула изобретения Триггер, содержащий восемь логических элементов И-НЕ (ИЛИ-НЕ), выход предыдущего элемента соединен с первым входом последующего, выход восьмого элемента соединен с первым входом первого элемента, второй вход которого, подключен к первому входу устройства, а выход соединен со вторым входом третьего элемента, выход второго элемента соединен со вторым входом шестого элемента, выход которого подключен ко второму входу второго элемента, второй вход седьмого элемента подключен к выходу пятого элемента, второй вход которого подключен ко второму входу устройства, выходы четвертого и восьмого элементов соответственно подключены к первому и второму выходам устройства, отличающийся тем, что, с целью повышения быстродействия, увеличения нагрузочной способности и расширения

функциональных возможностей его, выходы .первого и пятого элементов соответственно соединены со вторыми входами восьмого и четвертого элементов,

Источники информации, принятые во внимание при экспертизе

Фиг.1

(Риг.г

Авторы

Даты

1980-12-07—Публикация

1979-01-08—Подача