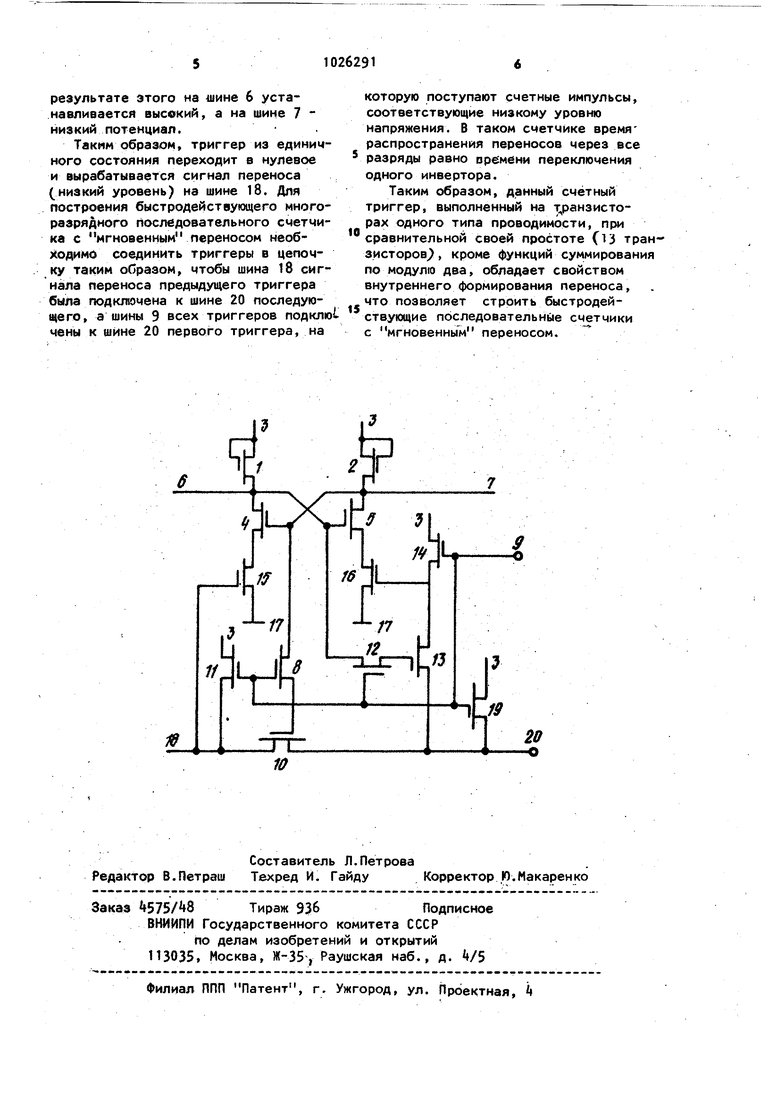

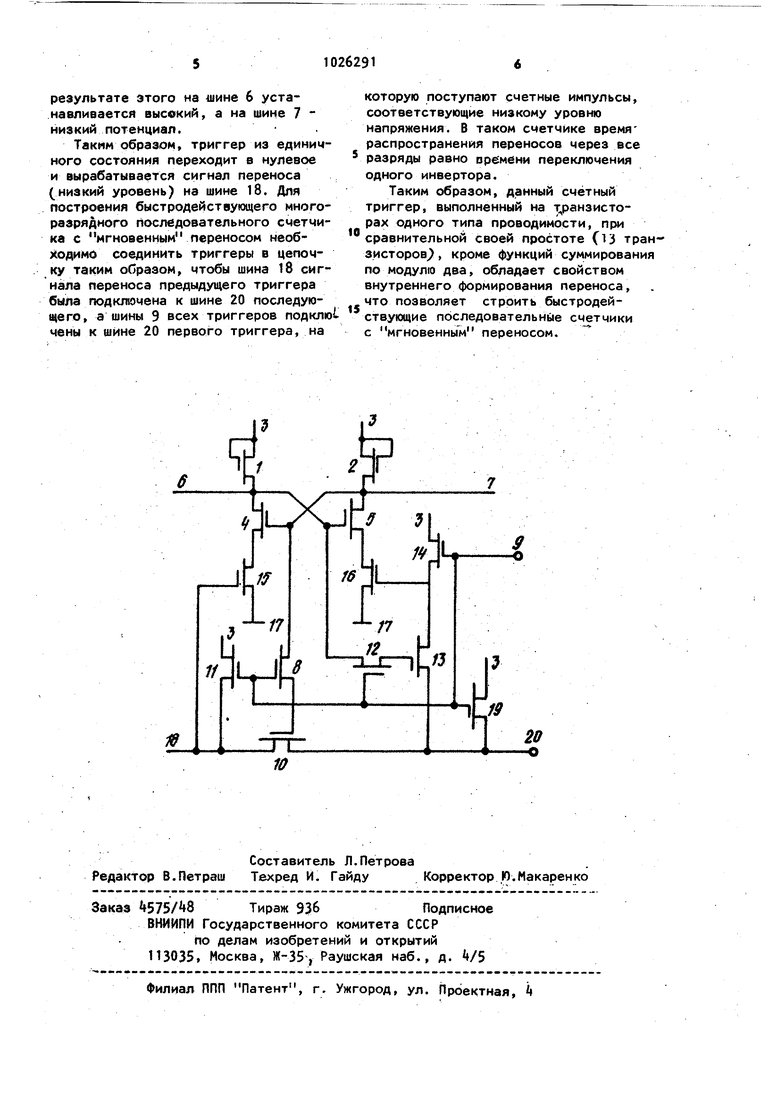

Изобретение относится к импульсной технике и может быть использовано при построении быстродействующих многоразрядных последовательных смет чиков . Известен счетный триггер на МДПтранзисторах, содержащий двухвходовы элементы ИЛИ-НЕ ( либо И-НЕ) с Перекрестными связями, выходные шины которых через линии задержки , выполненные на элементах того же типа подключены к входным шинам j 1 . Недостатком известного устройства является его сложность. Кроме того, на его основе возможно построение многоразрядных последовательных счет чиков только с последовательным пере носом. Наиболее близким по технической сущности к предлагаемому является счетный триггер на МДП-транзисторах, содержащий два нагрузочных транзистора, стоки и затворы которых подключены к шине питания, а исток каждого нагрузочного транзистора под ключен к стоку одного из двух переключающих транзисторов с перекрестными связями и к соответствующей выходной шине, а также первый транзистор, сток которого подключен к выход ной шине, на которой формируется прямой выходной сигнал, затвор - к первой входной шине, а исток - к затвору второго транзистора, сток которого подключен к истоку третьего транзистора, четвертый транзистор, сток которого подключен к выходной шине, на которой формируется инверсный сигнал, завтор - к первой входной шине, а истой - к затвору пятого транзистора, сток которого подклю чён к истоку шестого транзистора, и вторую входную шину, к которой подключены затворы третьего и шестого транзисторов, истоки второго, пятог и переключающих транзисторов подключены к общей шине, сток третьего подкпючен к стоку первбг.о транзистора , а сток шестого транзистора к стоку четвертого транзистора 2. Недостатком известного устройства является отсутствие внутреннего формирования переноса, что требует дополнительного оборудования для построения .многоразрядных последовательных счетчиков. Цель изобретения - расширение функциональных возможностей за счет внутреннего формирования переноса, позволяющего строить последовательные счетчики с мгновенным распространением переноса. Для достижения поставленной цели в счетный триггер на МДП-транзисто- pax, содержащий два нагрузочных тран-зистора, стоки и затворы которых подключены к шине питания, а исток каждого нагрузочного транзистора подключен к стоку одного из двух переключающих транзисторов с перекрестными ;связями и к соотаетструющей выходной шине, а также первый транзистор, сток которого подключен к выходной шине, на которой формируется прямой выходной сигнал, затвор - к первой входной шине, а исток - к затвору второго транзистора, сток которого подключен к истоку третьего транзистора, четвертый транзистор,сток которого подключен к выходной шине, на которой формируетЬя инверсный сигнал, затворк первой входной шине, а исток - к затвору пятого транзистора сток которого подключен к истоку шестого транзистора, и вторую входную шину,дополнительно введены три транзистора и шина сигнала переноса, причем стоки fiepBorp и второго дополнительных транзисторов подключены соответ-t; ственно к истокам переключающих транзисторов, истоки - к обкцей шине, затвор первого дополнитель . ного транзистора подключен к шине сигнала переноса, азатвор второго - к истоку шестого транзистора, сток третьего дополнительного транзистора подключен к шине питания, затвор - к первой входной шине, а исток - к второй входной шине, стоки третьего и шестого транзисторов подключены к шине питания, затворы к первой входной шине, сток второго ранзистора подключен к шине сигнаа переноса, а истоки второго и пято о транзисторов - к второй входной ине. На чертеже представлена электриеская принципиальная схема счетного |5иггёра на МДП-транзисторах. В предлагаемом устройстве стоки затворы первого нагрузочного транистора 1 и второго нагрузочного транистора 2 подключены к шине 3 питания , истоки транзисторов 1 и 2 подкТТючекы соответственно к стокам переключающих транзисторов А и 5 с перекрестными связями и к соответ ствующим выходным шинам 6 и 7. Сток первого транзистора 8 подключен .к выходной шине 7, на которой формируется прямой выходной сигнал затвор - к первой входной шине 9, а исток - к затвору второго транзис тора 10, сток которого подключен к истоку третьего транзистора 11. Сто четвертого транзистора 12 подключен к выходной шине 6, на которой форми руется инверсный сигнал, затвор к шине 9, а исток - к затвору пятог транзистора 13, сток которого подкл чен к истоку шестого транзистора 1к Стоки первого и второго дополни тельных транзисторов 15 и 16 подклю чены соответственно к истокам переключающих транзисторов k и 5, их истоки - к общей шине 17- Затвор транзистора 15 подключен к шине 18 сигнала переноса, а затвор транзистора 16 - к истоку транзистора 14. Сток третьего дополнительного транзистора 19 подключен к шине 3 питания, затвор - к шине 9, а исток - к второй входной шине 20. Стоки транзисторов 11 и 1А подключены к шине 3 питания, затворы -. к шине 9, сто второго транзистора 10 подключен к шине 18 а истоки транзисторов 10 и 13 - шине. 20. Устройство работает следующим об .разом. . Напряжение логической единицы соответствует высокому потенциалу шины 3 питания, а напряжение логиче кого нуля - потенциалу общей шины. В отсутствие счетного импульса на шинах 20 и 9 устанавливается высокий потенциал. Вследствие 3toro открываются транзисторы 8,11,12, Т и 19. Через открытый транзистор 19 шина 20 дополнительно подключается к шине 3 питания. Через открытые транзисторы 11 и 14 до потенциала шины 3 питания заряжаются емкос затворов транзисторов 15 и 16, что обеспечивает сохранение информации триггере в промежутках между счетны ми импульсами. Открытые транзисторы 8 и 12 подключают к выходным шинам 7 и соответственно емкости затворов транзисторов 10 и 13- Вели триггер находится в состоянии О на шине 7), емкость затвора транзистора 10 разряжается до напрйжения логического нуля, а емкость затвора транзистора 13 заряжается до напряжения логической единицы. При поступлении О на шину 9 закрываются транзисторы 8,11, 12,1 и 19. Закрытие транзисторов 8 и 12 приводит к тому, что на затворных емкостях транзисторов 10 и 13 фиксируется на время , определяемое разрядом через сопротивление переходов затвор - общая шина этих транзисторов, состояние триггера. На емкостях затворов транзисторов 15 и 16 сохраняется высокий потенциал,так как при 1 на шине 20 нет цепи для разряда этих емкосг тей. Если в этом состоянии на шину 20 поступает счетный импульс (напряжение логического нуля), то разряжается емкость затвора транзистора 16, так как открывается транзистор 13 вследствие того, что у него хранится на затворной емкости напряжение логической единицы. Емкость..; затвора транзистора 15 остается неразряженной, так как остается закрытым транзистор 10. Наличие напряжения логического нуля на затворе транзистора 16 приводит к закрытию последнего и установке на шине 7 триггера высокого потенциала, что в свою очередь приводит к установке йизкого потенциала на шине 6. На шине 18 сигнала переноса остается высокий потенциал, так как закрыт транзистор 10, что соответствует отсутствию переноса из данного разряда. Таким образом, триггер из нулевого состояния с приходом импульсов низкого потенциала на шины 20 и 9 переходит в единичное состояние и сигнал переноса не вырабатывается. Рассмотрим случай, когда триггер находится в единичном состоянии. При поступлении напряжения логического, нуля на шину 9, как и в предыдущем состоянии, закрываются транзисторы 8,11,12,14 и 19. На емкостях затворов .10 и 13 фиксируется соответственно высокий и низкий потенциалы. При поступлении О на шину 20 открывается транзистор 10, в результате чего разряжается емкость транзистора 15 и на шине 18 сигнала переноса устанавливается низкий потенциал, затворная емкость транзистора 16 остается неразряженной. В :

результате этого на шине 6 устанавливается высокий, а на шине 7 низкий потенциал.

Таким образом, триггер из единичного состояния переходит в нулевое и вырабатывается сигнал переноса (низкий уровень) на шине 18. Для построения быстродействующего многоразрядного Последовательного счетчика с мгновенным переносом необходимо соединить триггеры в цепочку таким образом, чтобы шина 18 сигнала переноса предыдущего триггера была подключена к шине 20 последующего, а шины 9 всех триггеров подключены к шине 20 первого триггера, на

которую поступают счетные импульсы, соответствующие низкому уровню напряжения. В таком счетчике время распространения переносов через все

разряды равно орбмени переключения одного инвертора.

Таким образом, данный счётный триггер, выполненный на т ранзисторах одного типа проводимости, при

сравнительной своей простоте (13 транзисторов , кроме функций суммирования по модулю два, обладает свойством внутреннего формирования переноса, что позволяет строить быстродействующие последовательные счетчики с мгновенным переносом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер с раздельными входами | 1978 |

|

SU746874A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Элемент памяти для динамического регистра сдвига | 1977 |

|

SU684617A1 |

| Четырехфазный МДП-триггер | 1989 |

|

SU1628186A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Адресный формирователь | 1981 |

|

SU991504A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Блок формирования сквозного переноса в сумматоре | 1979 |

|

SU1042012A1 |

СЧЕТНЫЙ ТРИГГЕР НА МДП-ТРАНЗИСТОРАХ, содержащий два нагрузочных т| анзистора, стоки и затворы которых подкжочены к шине Xпитания, а исток каждого нагрузочного транзистора подключен к стоку одного из двух переключающих транзисторов перекрестными связями и к соответствующей выходной шине, а также первый транзистор, сток которого подключи к выходной шине, на которой формируется прямей выходной сигнал, затвор - к первой входной шине, а исток - к затвору второго транзистора, сток которого подключен к истоку треть1рго транзистора, четвертый транзистор, сток которого подключен к выходной шине, на которой формируется инверсный сигнал, затвор - к первой входной шине, а исток - к затвору пятого транзистора , сток которого подключен к истоку шестого транзистора, и вторую входную шину, отличающийс я тем, что, с целью расширения ;функциональных возможностей за счет внутреннего формирования переноса позволяющего строить последовательные счетчики с мгновенным распространением переносов, в него дополнительно введены три транзистора Ишина сигнала переноса, причем стоки первого и второго дополнительных транзисторов подключены соответственно к истокам переключающих транзисторов, истоки к общей шине, затвор первого (Л дополнительного транзистора под.ключен к шине сигнала переноса, а затвор второго - к истоку шестого транзистора, сток третьего дополнительного транзистора подключен к шине питания, затвор - к первой входной шине, а исток - к второй о входной шине, стоки третьего и N9 шестого транзисторов подключены к шине а ю со питания, затворы - к первой входной шине, сток второго транзистора подключен к шине сигнала переноса, а истоки второго и пятого транзисто- ров - к второй входной шине.

Авторы

Даты

1983-06-30—Публикация

1982-01-05—Подача