(54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ СЛУЧАЙНОГО

1

Изобретение относится к средствам специализированной вычислительной техники и предназначено для статистических анализаторов, измеряющих вероятностные характеристики многомерных сигналов с изменяющимися параметрами (квазистационарные) и использующих групповые мини-ЭВМ.

Известно устройство, в котором адаптация диапазона кодирования, центрирование сигнала до кодирования выполняется введением автономных приборов для измерения вероятностных характеристик (дисперсии, функции распределения, математического ожидания) 1.

Недостатками этого устройства являются низкое быстродействие и сложность организации адаптивного кодирования многомерных сигналов из-за необходимости введения многих автономных приборов для измерения в.ероятностных характеристик, сложной системы управления ими, сложности перехода от одного метода кодирования к другим.

Наиболее близким к изобретению по техническому решению является устройство для кодирования случайного процесса, содержащее крммутаПРОЦЕССА

тор, выход которого подключен ко входу группового усилителя, выход которого соединен со входом аналого-цифрового преобразователя, блок управления, первые вход и выход которого подключены к первым входу и выходу первого управляющего регистра, второй управляющий регистр, первые вход и выход которого соединены с

to первыми входами и выходами цифроаналогового преобразователя, аналогоцифровой преобразователь, первые вход и выход которого соединены с первыми входами и выходом третьего

S управляющего регистра, четвертый управляющий регистр, первые вход и выход которого подключены к первым входу и выходу первого блока коммутации, вторые входы и выходы всех

20 управляющих регистров и первые вход и выход пятого управляющего регистра соединены с соответствующими входом и выходом второго блока коммутации 21 Недостатком данного устройства является низкое быстродействие при решении задачи адаптивного кодирования .многомерных сигналов..

Цель изобретения - повышение быстродействия адаптивного масштабирова-.

Зи ния многомерных случайных сигналов.

Цель достигается тем, что в устроПство введены L-усилителей, коммутатор, групповой усилитель и два дополнительных управляющих регистра, при этом первые входы и выходы L-усилителей соединены с первыми входом и выходом neiJBoro управляющего дополнительного регистра, первые вход и выход второго управляющего дополнительного регистра подключены к первым входу и вьоходу коммутатора, другие входы которого соединены со вторыми выходами усилителей, вторые входы которых являются соответствующими входеи и устройства, вторые вход и выход первого и. второго дополнительных управляющих регистров Аодключены к соответствующим входам и выходам второго блока коммутации.

Кроме-того, первый, второй дополнительные управляющие регистры и второй управляющий регистр содержат блок адресации, распределитель и блок преобразования входных кодов, состоящий из селекторов, дешифраторов , регистров и переключателя, при этом первые информационные выходы блока адресации подключены к информационним входам селектора, распределителя и регистров, первый и тре, тий вьаходы которого объединены с выходами переключателя, со вторБП 1 информационным выходом блока адресации и является перАзм выходом управляющего регистра, выходы селекторов соединены соответствующими информационньлми входами дешифраторов, выходы которых подключены к соответствую-пим первым управляющим входам регистров, вторые управляющие входы которого объединены с управляющими входами селекторов, дешифраторов и переключателя и подключены к первому выходу распределителя, .второй выход которого соединен с первым входом блока адресации, второй вход которого являете первым входом управляющего регистра,третьи входы и выходы блока адресации являются вторыми входамии выходами управляющего реги;ра,второй выход регистров подключен информационному входу переключателя. Первый, третий и пятый управляющие регистры содержат блок адресации, блок преобразования входных кодов, .распределителя, первый переключатель и блок преобразования выходных кодов, состоящий из второго переключателя генератора «одов символов, генератора дополнительных кодов ,.блока переключателей, преобразователей позиционного кода в двоичный и регистров, входы которых являются перрыми входами управляющего регистра, управляющие входы регистров,преобразователей позиционных кодов в двоичный, блока переключателей, генераторов кодов символов и дополнительных кодов и первый управляющий вход второго переключателя объединены и

Подключены к первому выходу первого распределителя, второй выход которого соединен с первым входом блока

адресации, информационные выходы которого соединены с информационными входами блока преобразования входных кодов, первого распределителя, второго переключателя и второго распределителя, первый выход которого соединен со вторым управляющим входом блока адресации, третий управляющий вход которого подключен к выходу второго переключателя, второй управляющий вход которого соединен с выходом генератора кодов символов, третий управляющий вход переключателя подключен ко второму выходу генератора дополнительных кодов, информационные входы которого соединены с соответствующими выходами блока переключателей, информационные входы которого подключены к выходам преобразователей позиционных кодов в двоичный, информационные входы которых соединены с выходами регистров, первый выход первого переключателя объединен с первым выходом блока преобразования входных кодов и является первым выходом управляющего регистра, второй выход второго распределителя

подключен к управляющему входу блока преобразования входных кодов, второй выход которого соединен со входом первого переключателя, четвертые и первые входы и выходы блока адресации являются соответственно вторыми входами и выходами управляющего регистра.

Четвертый управляющий регистр содержит два распределителя, два блока адресации, преобразователь входных кодов и преобразователь выходных кодов, причем выход преобразователя входных кодо,в подключен к певому информационному входу первого блотса адресации, второй информационный вход которого соединен с выходо преобразователя входных кодов, информационный вход которого объединен с информационными входами первого распределителя, преобразователя выходных кодов и второго распределителя и подключен к первому информационному выходу второго блока адресации, первый управляющий вход второго блока адресации соединен с первым выходом второго распределителя, второй выход которого подключен к управляющему входу преобразователя выходных кодов, второй управляющий вход второго блока адресации соединен с первым выходом первого распределителя, второй выход которого подключен к управляющему .входу преобразователя входных кодов .второй информационный выход второго блока адресации объединен. , с первым выходом первого блока адресации и

является первым выходом управляющего регистра, второй вход первого блока ; щресации является первьм входом управлякяцего регистра, второй выход первого блока адресации подключен к информационному входу вторюго блока адресации, первые и вторые входы и выходы которого являются ..соответственно вторыми входами и выходами управляющего регистра,

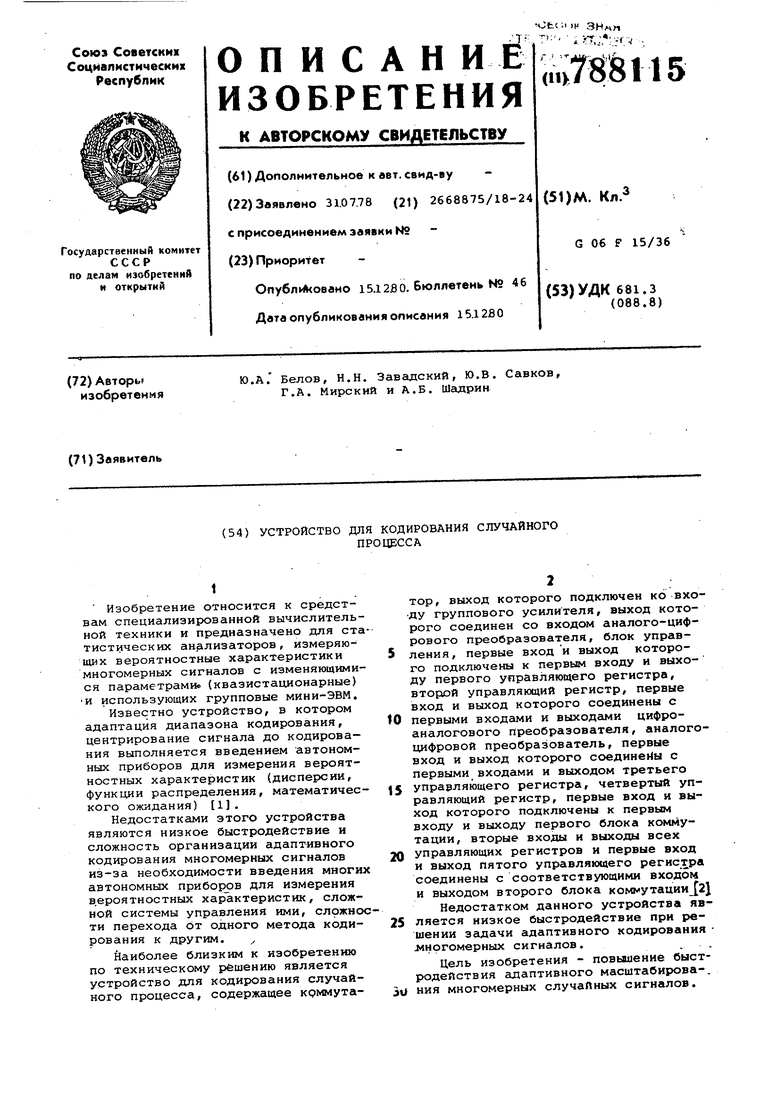

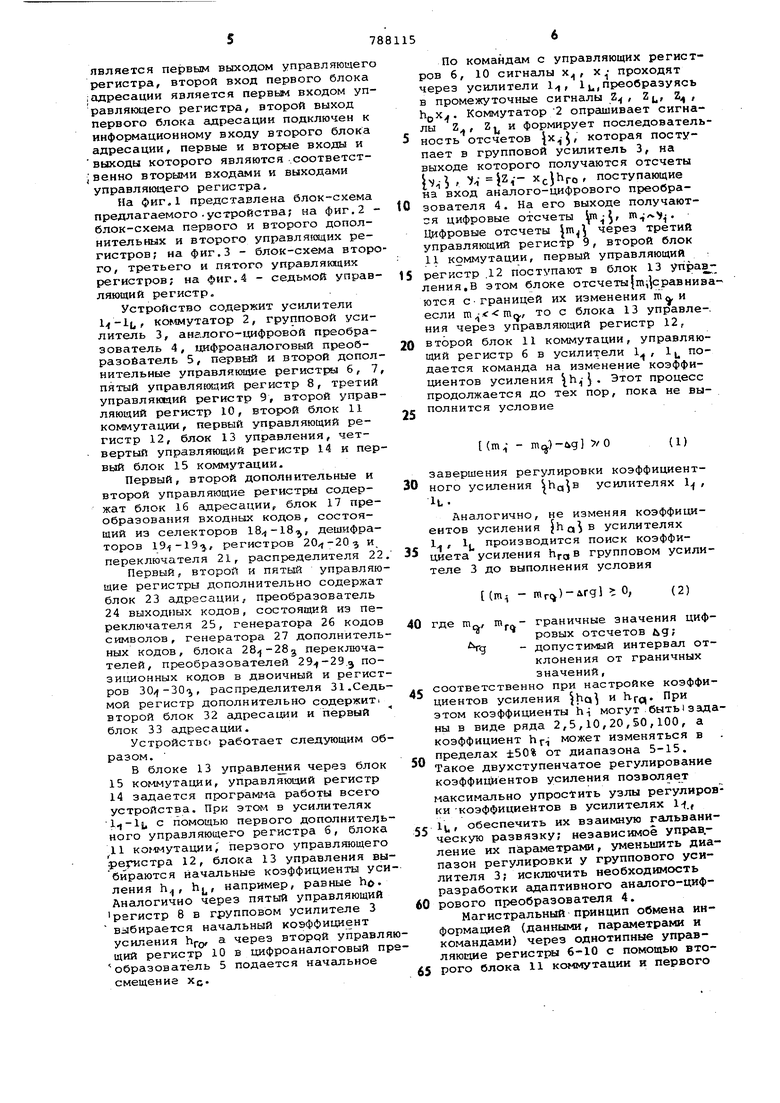

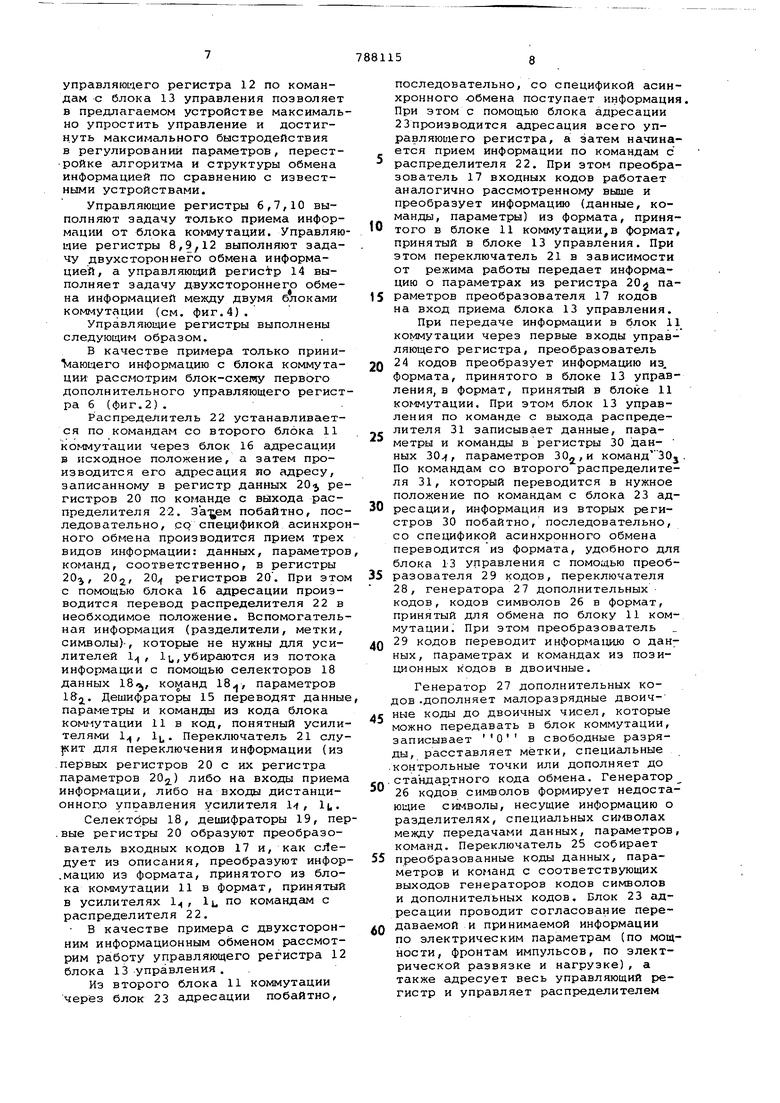

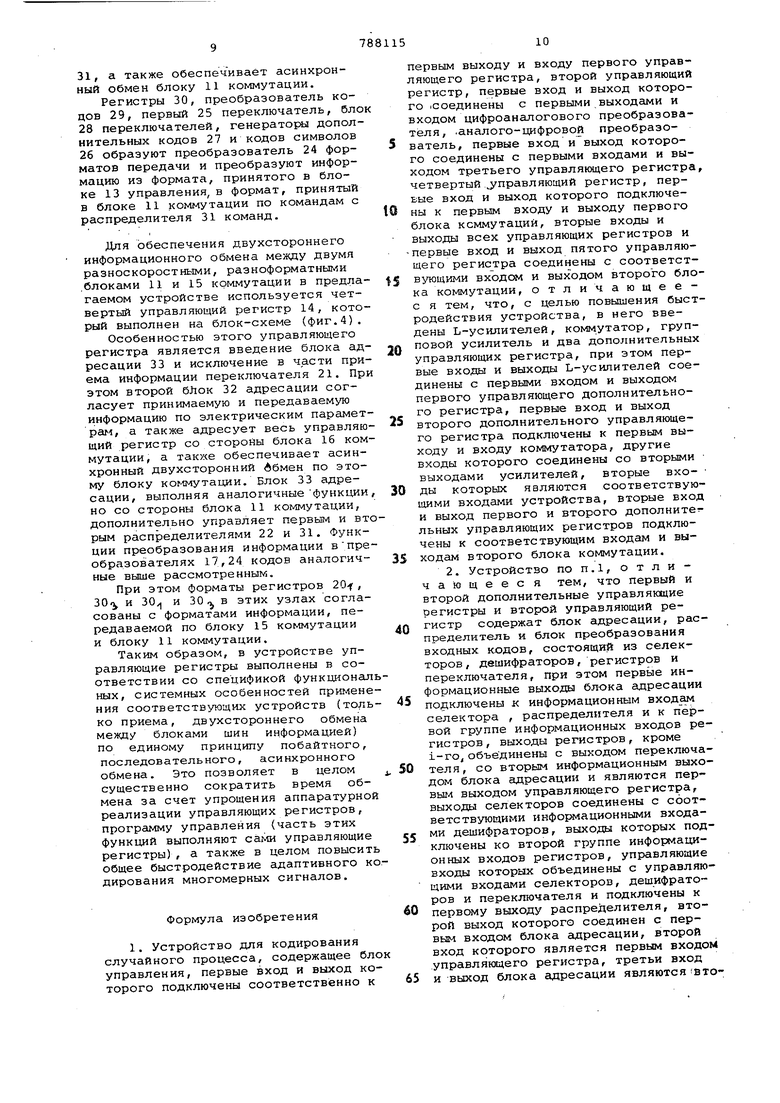

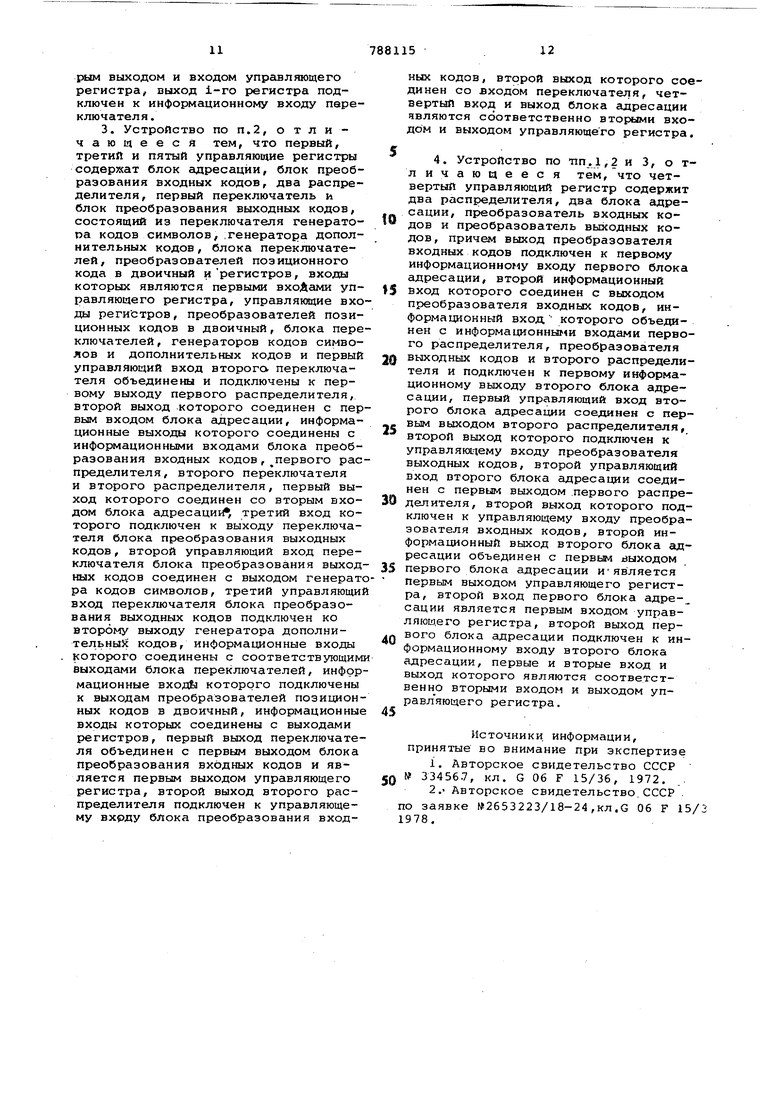

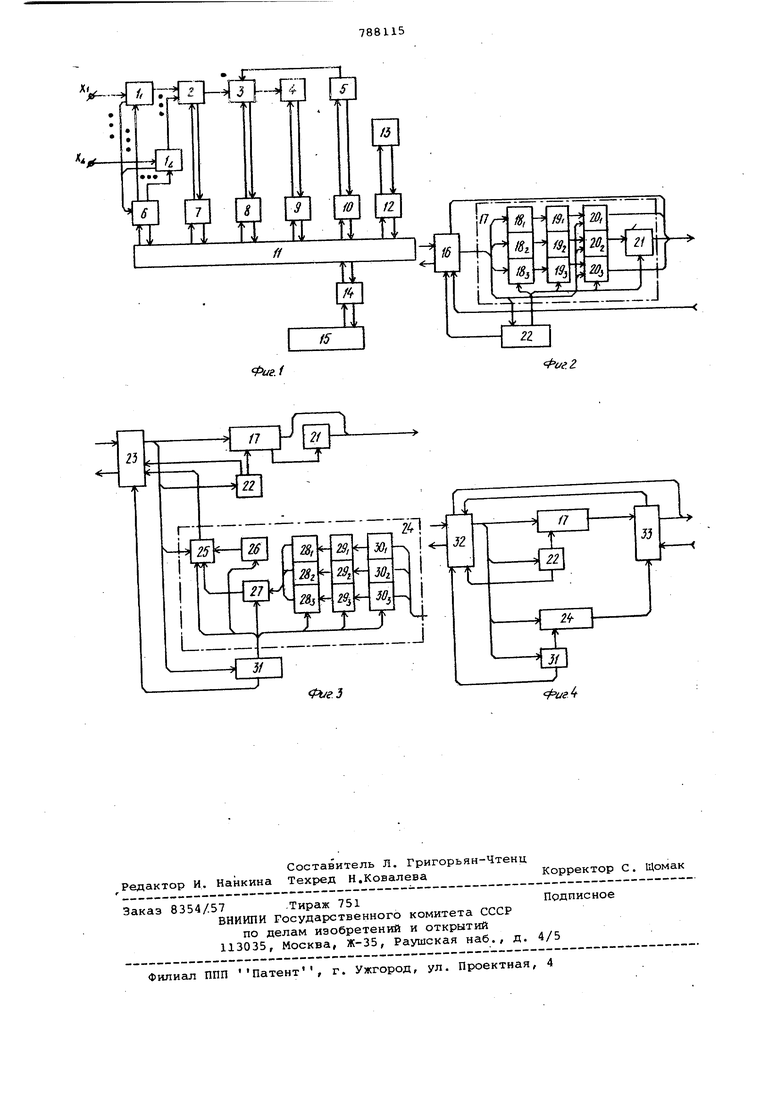

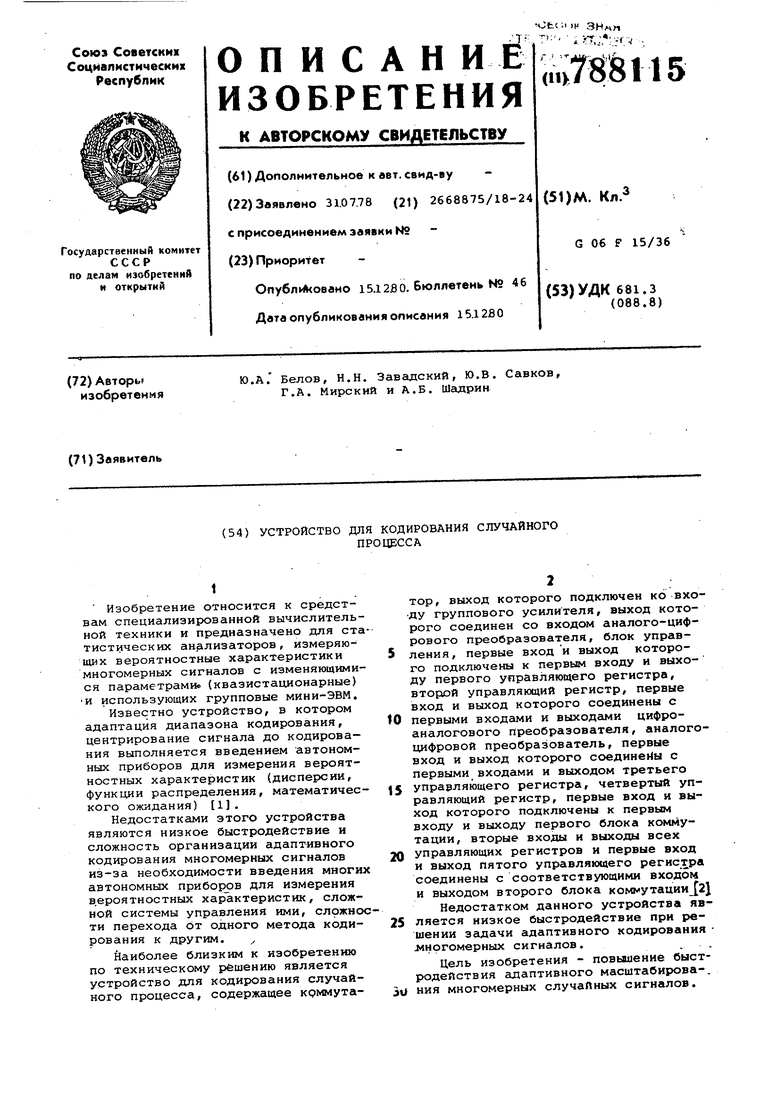

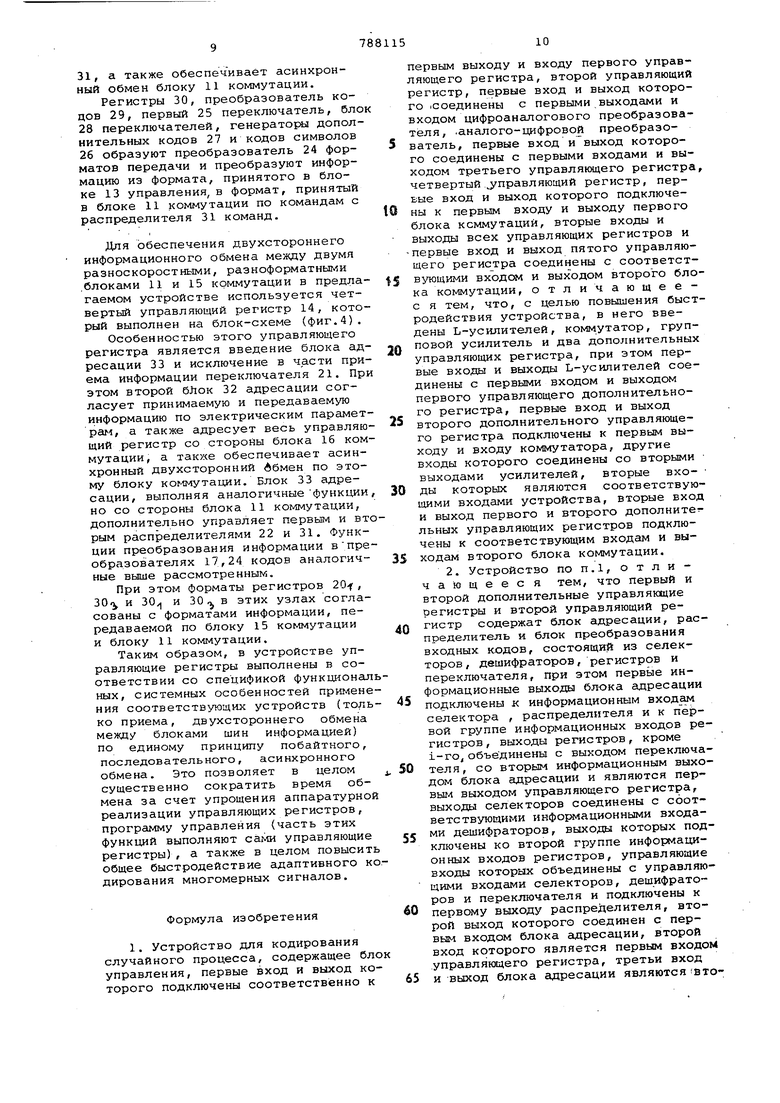

На фиг,1 представлена блок-схема предлагаемого.устройства; на фиг,2 блок-схема первого и второго дополнительных и второго управля ощих регистров; на фиг.З - блок-схема второго, третьего и пятого управляквдих регистров; на фиг.4 - седьмой управляющий регистр.

Устройство содержит усилители ,, коммутатор 2, групповой усилитель 3, аналого-цифровой преобразователь 4, Щ1фроаналоговый преобразобатель 5, первый и второй дополнительные управляющие регистры 6, 7, пятый управляющий регистр 8, третий управлямщий регистр 9, второй управляющий регистр 10, второй блок 11 коммутации, первый управляющий регистр 12, блок 13 управления, четвертый управляющий регистр 14 и первый блок 15 коммутации.

Первый, второй дополнительные и второй управляющие регистры содержат блок 16 адресации, блок 17 преобразования входных кодов, состоящий из селекторов , дешифраторов , регистров 20у,-20-з и переключателя 21, распределителя 22.

Первый, второй и пятый управляющие регистры дополнительно содержат блок 23 адресации, преобразователь 24 выходных кодов, состоящий из переключателя 25, генератора 26 кодов символов, генератора 27 дополнительных кодов, блока переключателей, преобразователей .з позиционных кодов в двоичный и регистров 30,}-30-, распределителя 31.Седьмой регистр дополнительно содержит второй блок 32 адреса1&1и и первый блок 33 адресации.

Устройство работает следующим образом.

В блоке 13 управления через блок 15 коммутации, управляющий регистр 14 задается пpoгpaм 1a работы всего устройства. При этом в усилителях , с помощью первого дoпoлнитe lьного управляющего регистра б, блока 11 коммутации, первого управляющего регистра 12, блока 13 управления выбйраются начальные коэффициенты усиления h, hj, например, равные ho. Аналогично через пятый управляющий регистр В в групповом усилителе 3 выбирается начальный коэффициент усиления hf-g, а через второй управляющий регистр 10 в цифроаналоговый nps образоватёль 5 подается начешьное смещение Хд.

По командам с управляющих регистров 6, 10 сигналы х , X , проходят через усилители 1,|, 1,, преобразуясь в промежуточные сигналы Z , 2ц, Z , hpX. Коммутатор 2 опрашивает сигналы Z., 2| и формирует последовательность отсчетов X;,-J, которая поступает в групповой усилитель 3, на выходе которого получаются отсчеты } , л iZ,- Xcjhro , поступающие на вход аналого-цифрового преобразователя 4. На его выходе получаются цифровые отсчеты . Цифровые отсчеты через третий управляющий регистр 9, второй блок

11 коммутации, первый управляющий :

5 регистр .12 поступают в блок 13 Ленин,В этом блоке отсчеты{т сравниваются с-границей их изменения гол, и если (j., то с блока 13 управле-. ния через управляющий регистр 12,

0 второй блок 11 коммутации, управляющий регистр б в усилители 1., 1 подается команда на изменение коэффициентов усиления h,- J . Этот процесс продолжается до тех пор, пока не выг полнится условие

( - m()-ug / О

(1)

завершения регулировки коэффициентного усиления усилителях 1, ItАналогично, не изменяя коэффициентов усиления усилителях 1 , Ij производится поиск коэффициета усиления групповом усилителе 3 до выполнения условия (т.; - mr() О,

(2)

где luf,, Гор - граничные значения цифровых отсчетов лд; д - допустимый интервал отклонения от граничных значений,

соответственно при настройке коэффициентов усиления ha и h-j-q. При этом коэффициенты hi могут быть(заданы в виде ряда 2,5,10,20,50,100, а коэффициент hj-j может изменяться в

пределах ±50% от диапазона 5-15.

Такое двухступенчатое регулирование коэффициентов усиления позволяет максимально упростить узлы регулировки коэффициентов в усилителях l-f.,

luf обеспечить их взаимную гальваническую развязку; независимое управление их параметрами, уменьишть диапазон регулировки у группового усилителя 3; исключить необходимость разработки адаптивного аналого-цифрового преобразователя 4.

Магистральный принцип обмена информацией (данными, параметрами и командами) через однотипные управляющие регист1ял 6-10 с помощью второго блока 11 коммутации и первого

управляющего регистра 12 по командам с блока 13 управления позволяет в предлагаемом устройстве максимально упростить управление и достигнуть максимального быстродействия в регулировании параметров, перестройке алгоритма и структуры обмена информацией по сравнению с известными устройствами.

Управляющие регистры 6,7,10 выполняют задачу только приема информации от блока коммутации. Управляющие регистры 8,9,12 выполняют задачу двухстороннего обмена информацией, а управляющий регистр 14 выполняет задачу двухстороннего обмена информацией между двумя блоками коммутации (см. фиг.4).

Управляющие регистры выполнены следующим образом.

В качестве примера только прини1у1ающего информацию с блока коммутации рассмотрим блок-схему первого дополнительного управляющего регистра 6 (фиг.2) .

Распределитель 22 устанавливается по командам со второго блока 11 коммутации через блок 16 адресации в исходное положение, а затем производится его сщресация ио адресу, записанному в регистр данных 20 регистров 20 по команде с выхода распределителя 22. побайтно, последовательно, со спецификой асинхронного обмена производится прием трех видов информации: данных, параметров команд, соответственно, в регистры 20, 20, 20 регистров 20. При этом с помощью блока 16 адресации производится перевод распределителя 22 в необходимое положение. Вспомогательная информация (разделители, метки, символы)-, которые не нужны для усилителей 1 , 1;, убираются из потока информации с помощью селекторов 18 данных 18/, команд 18, параметров ISj.- Дешифраторы 15 переводят данные параметры и команды из кода блока коммутации 11 в код, понятный усилителями 1, 1. Переключатель 21 для переключения информации (из первых регистров 20 с их регистра параметров 202) либо на входы приема информации, либо на входы дистанционного управления усилителя l-f , li,.

Селекторы 18, дешифраторы 19, пер.вые регистры 20 образуют преобразователь входных кодов 17 и, как сЛедует из описания, преобразуют инфор.мацию из формата, принятого из блока коммутации 11 в формат, принятый в усилителях 1 , 1 по командам с распределителя 22. В качестве примера с двухсторонним информационным обменом рассмотрим работу управляющего регистра 12 блока 13 управления .

Из второго блока 11 коммутации через блок 23 адресации побайтно.

последовательно, со спецификой асинхронного обмена поступает информаци При этом с помощью блока адресации 23производится адресация всего управляющего регистра, а затем начинается прием информации по командам с распределителя 22. При зтом преобразователь 17 входных кодов работает аналогично рассмотренному выше и преобразует информацию (данные, команды, параметры) из формата, принятого в блоке 11 коммутации,в формат принятый в блоке 13 управления. При этом переключатель 21 в зависимости от режима работы передает информацию о параметрах из регистра 20 параметров преобразователя 17 кодов на вход приема блока 13 управления.

При передаче информации в блок 1 коммутации через первые входы управляющего регистра, преобразователь 24 кодов преобразует информацию из формата, принятого в блоке 13 управления, в формат, принятый в блоке 11 коммутации. При этом блок 13 управления по команде с выхода распределителя 31 записывает данные, параметры и команды в регистры 30 данных 30-f, параметров 30, и команд 30 По командам со второго распределителя 31, который переводится в нужное положение по командам с блока 23 адресации, информация из вторых регистров 30 побайтно, последовательно, со спецификой асинхронного обмена переводится из формата, удобного для блока 13 управления с помощью преобразователя 29 кодов, переключателя 28, генератора 27 дополнительных кодов, кодов символов 26 в формат, принятый для обмена по блоку 11 коммутации. При зтом преобразователь 29 кодов переводит информа1№1ю о данных, параметрах и командах из позиционных кодов в двоичные.

Генератор 27 дополнительных кодов .дополняет малоразрядные двоичные коды до двоичных чисел, которые можно передавать в блок коммутации, записывает О в свободные разряды, расставляет метки, специальные .контрольные точки или дополняет до .стандартного кода обмена. Генератор 26 кддов символов формирует недостающие символы, несущие информацию о разделителях, специальных символах между передачами данных, параметров команд. Переключатель 25 собирает преобразованные коды данных, параметров и команд с соответствующих выходов генераторов кодов символов и дополнительных кодов. Блок 23 адресации проводит согласование передаваемой и принимаемой информации по электрическим параметрам (по мощности, фронтам импульсов, по электрической развязке и нагрузке), а также адресует весь управляющий регистр и управляет распределителем 31, а также обеспечивает асинхронный обмен блоку 11 коммутации. Регистры 30, преобразователь коцов 29, первый 25 переключатель, бл 28 переключателей, генераторял допол нительных кодов 27 и кодов символов 26 образуют преобразователь 24 форматов передачи и преобразуют информацию из формата, принятого в блоке 13 управления, в формат, принятый в блоке 11 коммутации по командам с распределителя 31 команд. Для обеспечения двухстороннего информационного обмена между двумя разноскоростными, разноформатными .блоками 11 и 15 коммутации в предла гаемом устройстве используется четвертый управляющий регистр 14, кото рый выполнен на блок-схеме (фиг.4). Особенностью этого управляющего регистра является введение блока ад ресации 33 и исключение в части при ема информации переключателя 21. Пр этом второй бЛок 32 адресации согласует принимаемую и передаваемую информацию по электрическим парамет PCIM, а также адресует весь управляю щий регистр со сторойы блока 16 ком мутации, а также обеспечивает асинхронный двухсторонний ббмен по этому блоку кo 1мyтaции. БЛОК 33 адресации, выполняя аналогичныефункции но со стороны блока 11 коммутации, дополнительно угфавляет первым и вт рым распределителями 22 и 31. Функции преобразования информации впре образователях 17,24 кодов аналогичные выше рассмотренным. При этом форматы регистров 20-f , 30. и 30 и 30 в этих узлах согласованы с форматами информации, передаваемой по блоку 15 коммутации и блоку 11 коммутации. Таким образом, в устройстве управляющие регистры выполнены в соответствии со спецификой функционал ных, системных особенностей примене ния соответствующих устройств {толь ко приема, двухстороннего обмена между блоками шин информацией) по единому принципу побайтного, последовательного, асинхронного обмена. Это позволяет в целом существенно сократить время обмена за счет упрощения аппаратурной реализации управляющих регистров, программу управления (часть этих функций выполняют сами управляющие регистры), а также в целом повысить общее быстродействие адаптивного ко дирования многомерных сигналов. Формула изобретения 1. Устройство для кодирования случайного процесса, содержащее бло управления, первые вход и выход которого подключены соответственно к первым выходу и входу первого управляющего регистра, второй управляющий регистр, первые вход и выход которого .соединены с первыми выходами и входом цифроаналогового преобразователя, .аналого-цифровой преобразователь, первые вход и выход которого соединены с первыми входами и выходом третьего управляющего регистра, четвертый j/правляющий регистр, первые вход и выход которого подключены к первым входу и выходу первого блока коммутаций, вторые входы и выходы всех управляющих регистров и первые вход и выход пятого управляющего регистра соединены с соответствующими входсм и выходом второго блока коммутации, отличающеес я тем, что, с целью повышения быстродействия устройства, в него введены Ь-усилителей, коммутатор, групповой усилитель и два дополнительных управляющих регистра, при этом первые входы и выходы L-усипителей соединены с первьами входом и выходом первого управляющего дополнительного регистра, первые вход и выход второго дополнительного управляющего регистра подключены к первым выходу и входу коммутатора, другие входы которого соединены со вторыми выходами усилителей, вторые вхо- ды которых являются соответствующими входсми устройства, вторые вход и выход первого и второго дополнитетльных управляющих регистров подключены к соответствующим входам и выходам второго блока коммутации. 2. Устройство ПОП.1, отличающеес я тем, что первый и второй дополнительные управляющие регистры и второй управляющий регистр содержат блок адресации, распределитель и блок преобразования входных кодов, состоящий из селекторов, дешифраторов, регистров и переключателя, при этом первые информационные выходы блока адресации по{;ключены к информационным входам селектора , распределителя и к первой группе информационных входов регистров, выходы регистров, кроме i-ro, объединены с выходом переключателя, со вторым информационным выходом блока адресации и являются перВЫ1Л выходом управляющего регистра, выходы селекторов соединены с соответствующими информационными входами дешифраторов, выходы которых подключены ко второй группе информационных входов регистров, управляющие входы которых объединены с управляющи ш входс1ми селекторов, дешифраторов и переключателя и подключены к первому выходу распределителя, второй выход которого соединен с первым входом блока адресации, второй вход которого является первым входом управлякмцего регистра, третьи вход и выход блока адресации являютсяisxofoJM выходом и входом упрёшляющего регистра, i-ro регистра подключен к информационному входу переключателя.

3. Устройство по п.2, о т л и чающееся тем, что первый, третий и пятый управляющие регистры содержат блок адресации, блок преобразования входных кодов, два распределителя, первый переключатель и блок преобразования выходных кодов, состоящий из переключателя генератооа кодов символов, генератора дополнительных кодов, блока переключателей, преобразователей позиционного кода в двоичный ирегистров, входы которых являются первыми вхоАами управляющего регистра, управлянлдие входы регистров, преобразователей позиционных кодов в двоичный, блока переключателей , генераторов кодов символов и дополнительных кодов и первый управляющий вход второго, переключателя объединены и подключены к первому выходу первого распределителя, второй выход которого соединен с первым входом блока адресации, информационные выходы которого соединены с информационными входами блока преобразования входных кодов,первого распределителя, второго переключателя и второго распределителя, первый выход которого соединен со вторым входом блока адресаци, третий вход которого подключен к выходу переключателя блока преобразования выходных кодов, второй управляющий вход переключателя блока преобразования выходных кодов соединен с выходом генератра кодов символов, третий управляющи вход переключателя блока преобразования выходных кодов подключен ко второму выходу генератора дополнительный кодов, информационные входы которого соединены с соответствующим выходами блока переключателей, информационные входЬ которого подключены к выходам преобразователей пози1 1онных кодов в двоичный, информационные входы которых соединены с выходами регистров, первый выход переключателя объединен с первым выходом блока преобразования входных кодов и является первым выходом управляющего регистра, второй выход второго распределителя подключен к управляющему вхрду блока преобразования входных кодов, второй выход которого соединен со входом переключателя, четвертый вхрд и выход блока адресации являются соответственно вторыми входом и выходом управляющего регистра,

4. Устройство по Tin. 1,2 и 3, отличающееся тем, что четвертый управляющий регистр содержит два распределителя, два блока адресации, пр еобразователь входных кодов и преобразователь выходных кодов, причем выход преобразователя входных кодов подключен к первому информационному входу первого блока адресации, второй информационный вход которого соединен с выходом преобразователя входных кодов, информационный вход которого объединен с информационными входами первого распределителя, преобразователя выходных кодов и второго распределителя и подключен к первому информационному выходу второго блока адресации, первый управляющий вход второго блока адресации соединен с первым выходом второго распределителя, второй выход которого подключен к управлякядему входу преобразователя выходных кодов, второй управляющий вход второго блока адресации соединен с первым выходом .первого распределителя, второй выход которого подключен к управляющему входу преобразователя входных кодов, второй информационный выход второго блока адресации объединен с первым выходом первого блока адресации иявляется Первым выходом управляющего регистра, второй вход первого блока адре- сации является первым входом управляющего регистра, второй выход первого блока адресации подключен к информационному входу второго блока адресации, первые и вторые вход и выход которого являются соответствен нр вторыми входом и выходом управляющего регистра. 5

Источники, информации, принятые во внимание при зкспертизе

1. Авторское свидетельство СССР Q № 33456.7, кл. G 06 F 15/36, 1972. .. 2. Авторское свидетельство. СССР , по заявке №2653223/18-24,кл.G 06 F 15/3 1978,

Фuг.i

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Векторно-потоковое операционное устройство | 1989 |

|

SU1734100A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| СИСТЕМА ИНДИКАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2001 |

|

RU2206872C2 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

ftt/еЗ

Фиг

Авторы

Даты

1980-12-15—Публикация

1978-07-31—Подача