Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных комплексах, например, в терминальных системах управления (ТСУ) гибких производственных систем (ГПС) либо в системах числового программного управления станками и роботами.

Цель изобретения - повышение производительности за счет аппаратно-табличного выполнения операций и динамического микропрограммирования.

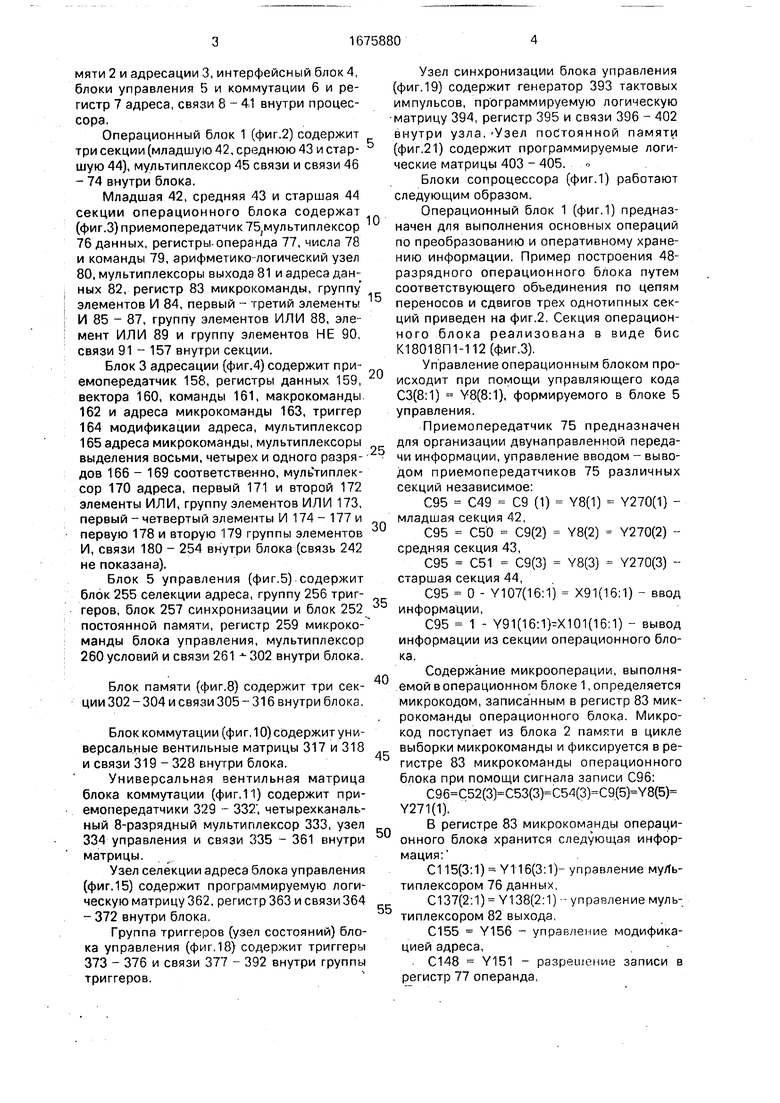

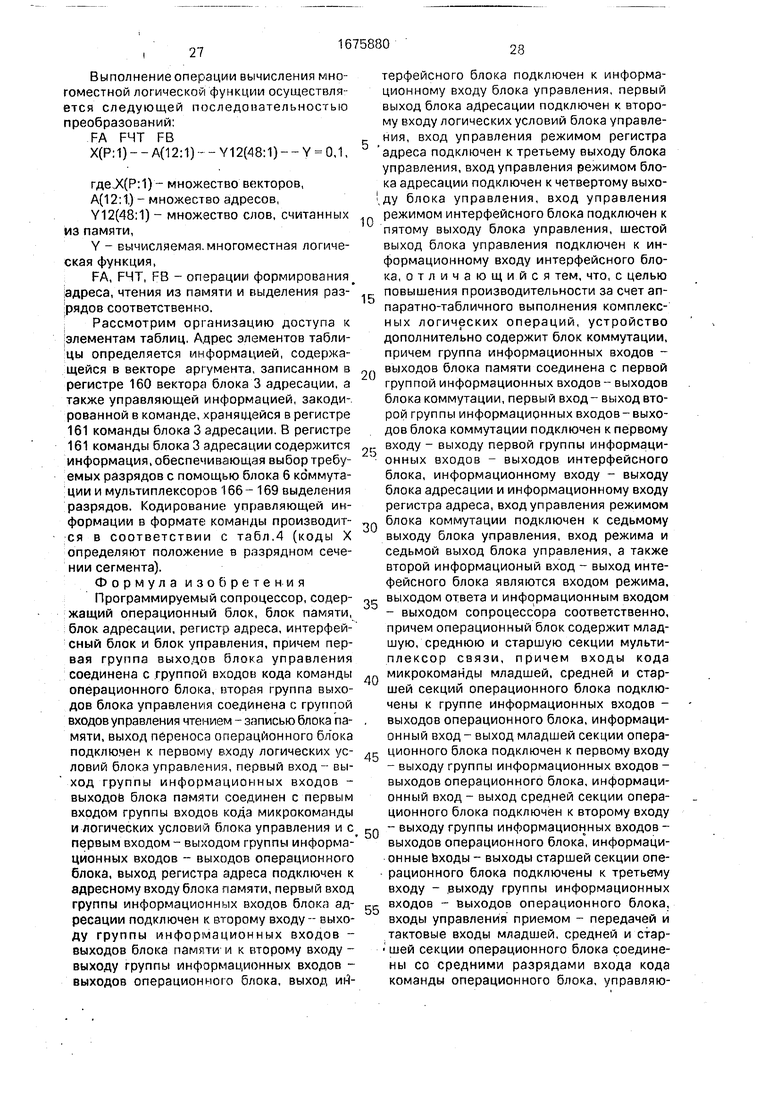

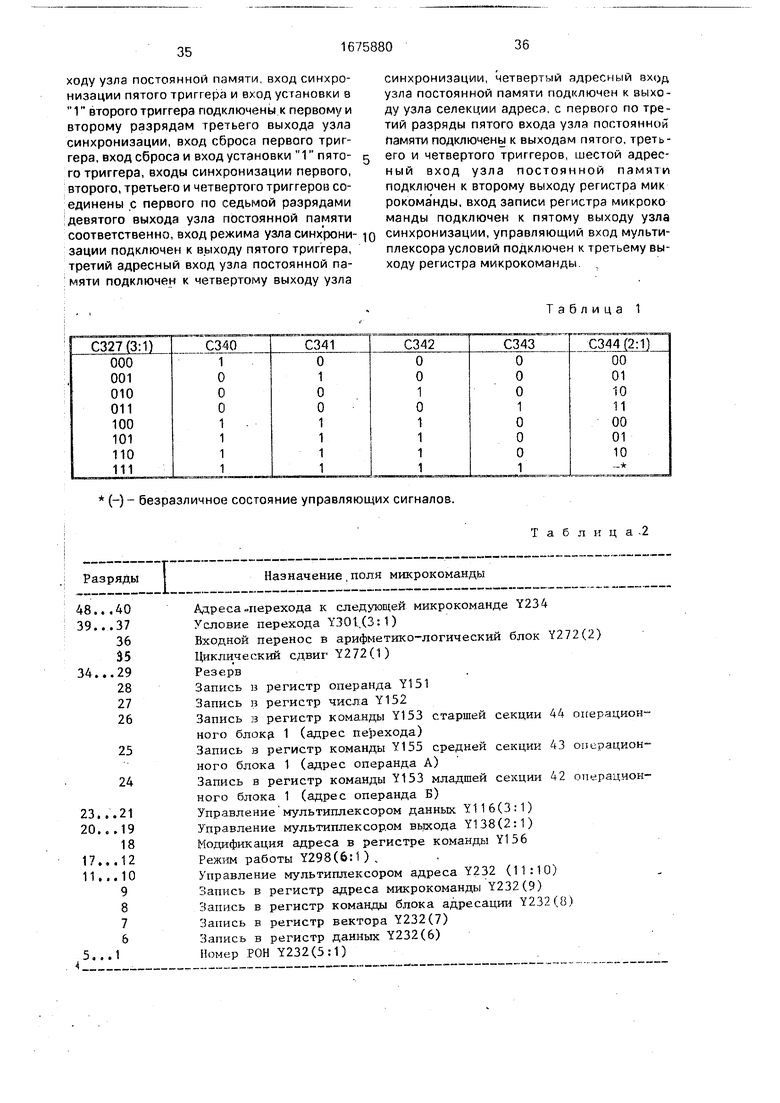

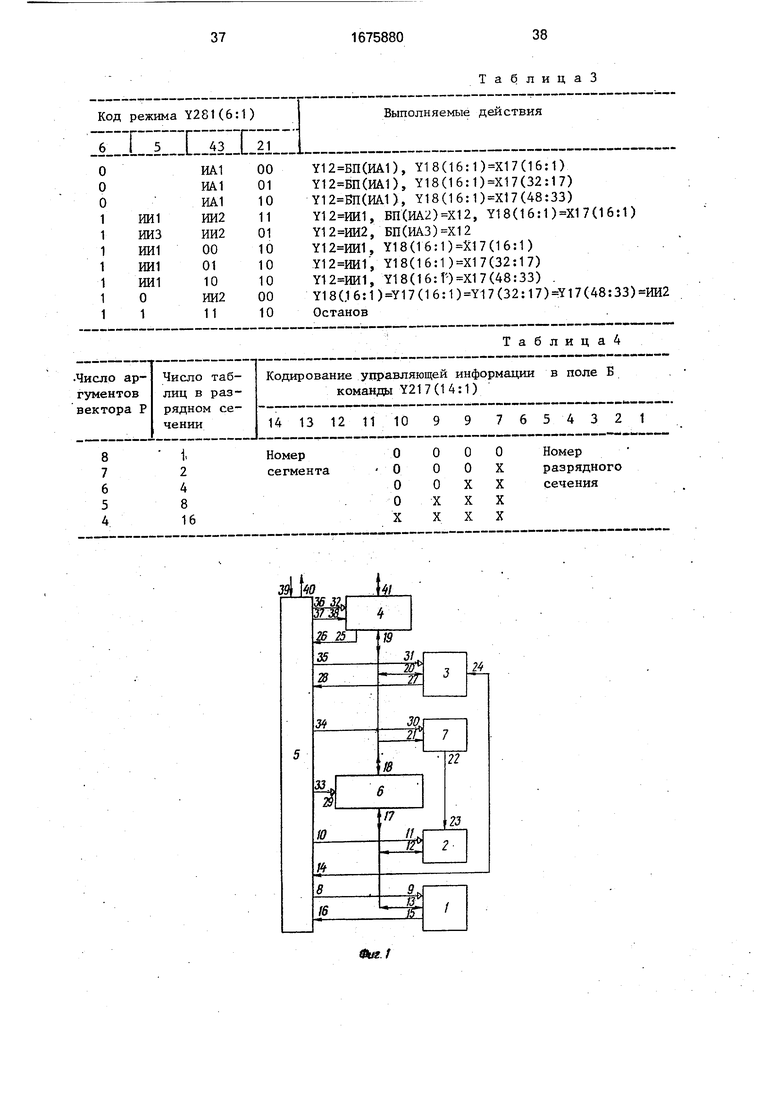

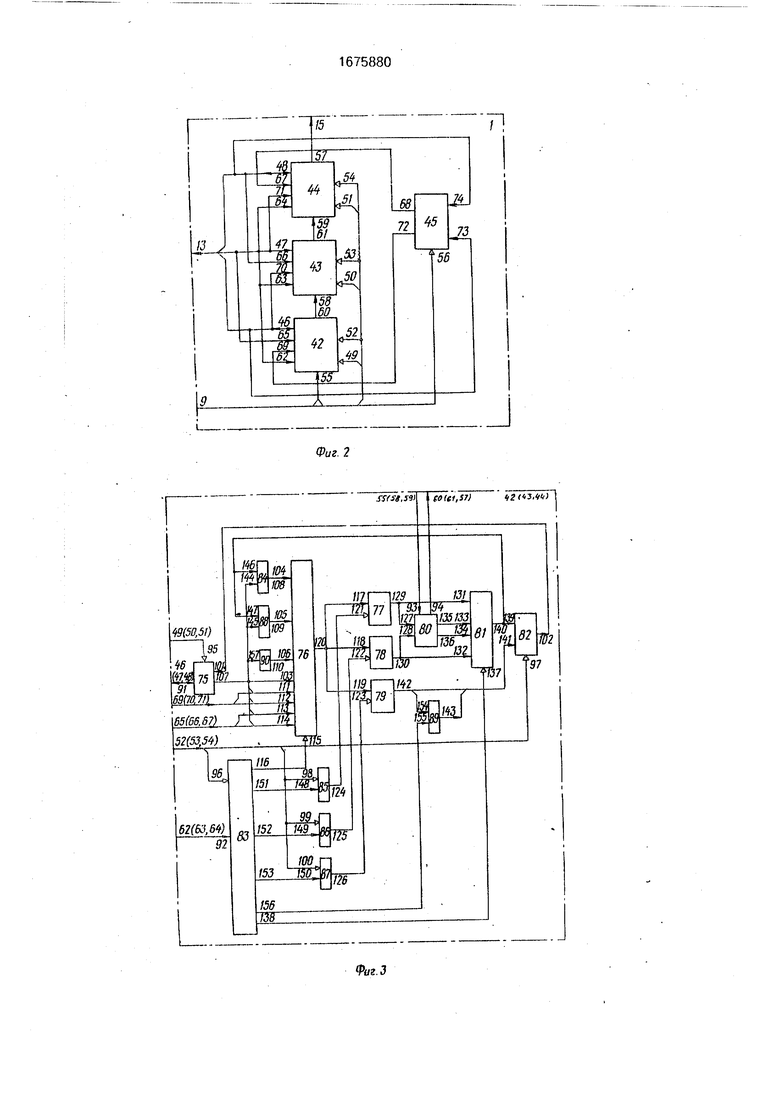

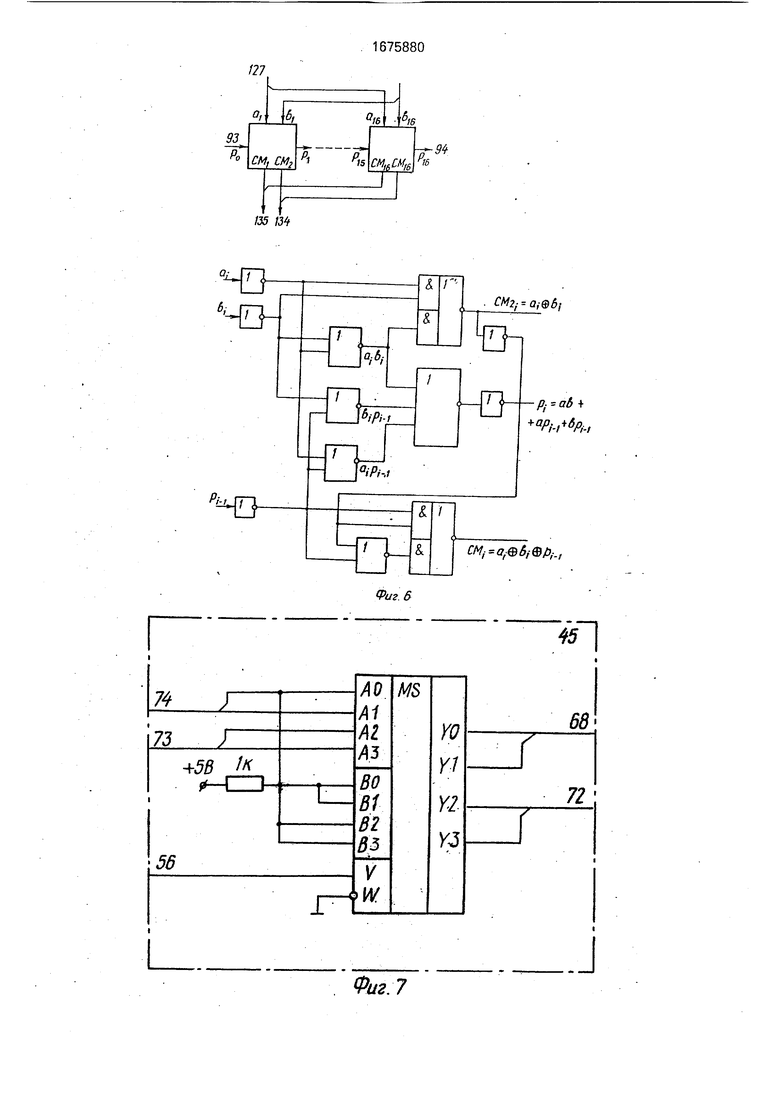

На фиг. 1 изображена структурная схема гибкого сопроцессора с аппаратно-таблич- ным выполнением операций; на фиг.2 - структурная схема операционного блока; на фиг.З - структурная схема 16-разрядной секции операционного блока; на фиг.4 - структурная схема блока адресации; на фиг.5 - структурная схема блока управления; на фиг.6 - функциональная схема сумматора секции операционного блока; на фиг.7 - пример реализации мультиплексора

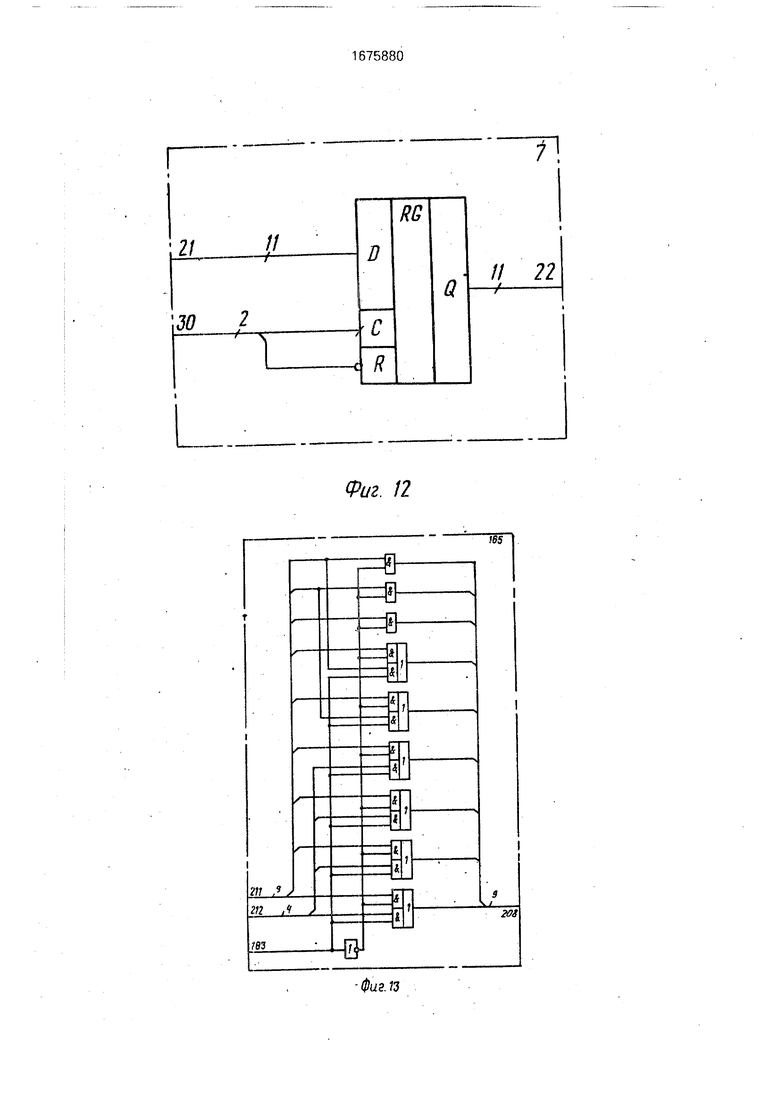

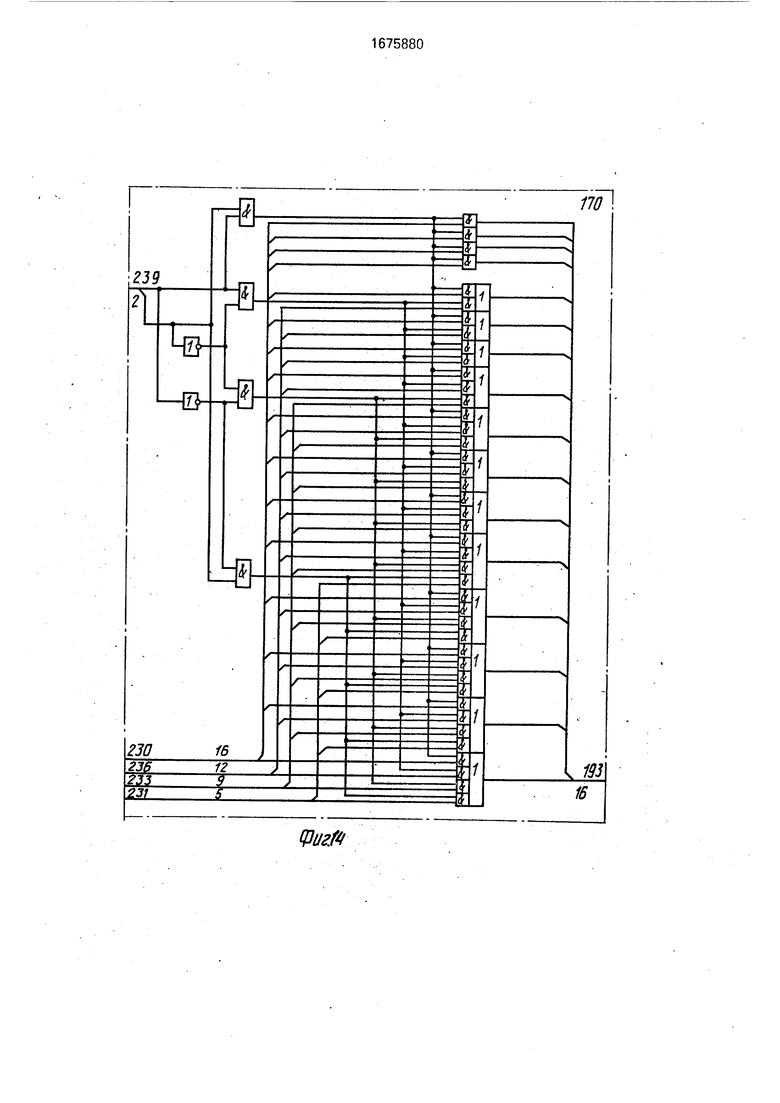

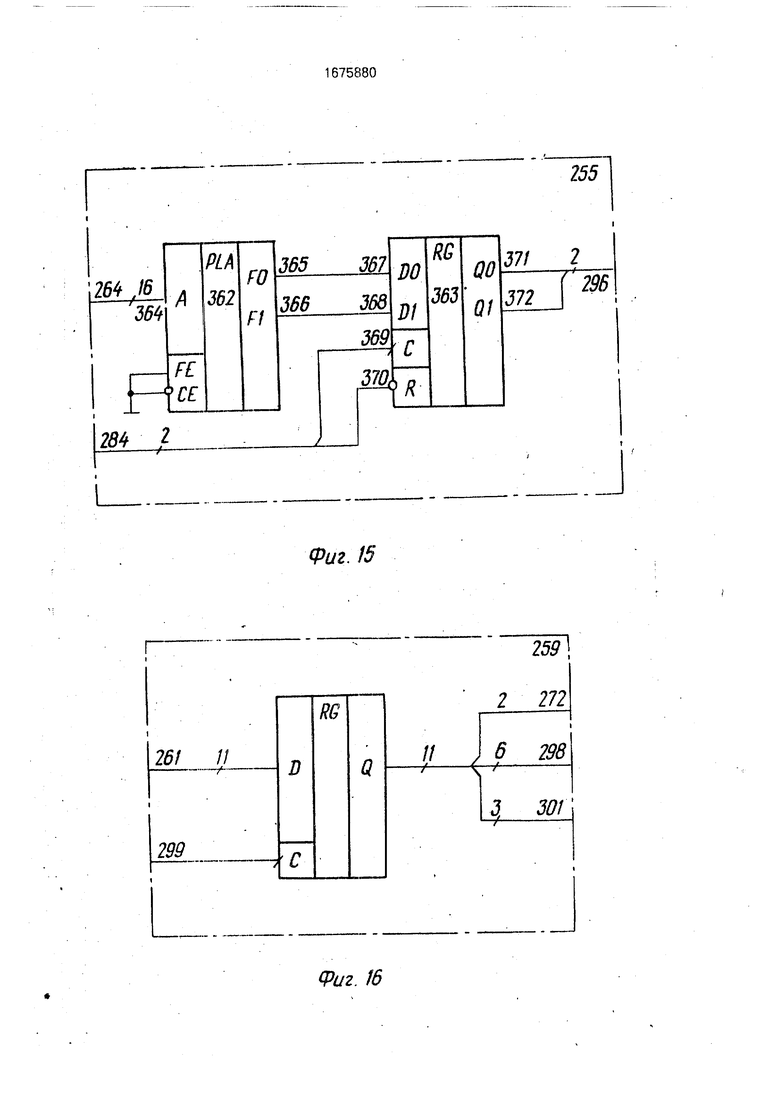

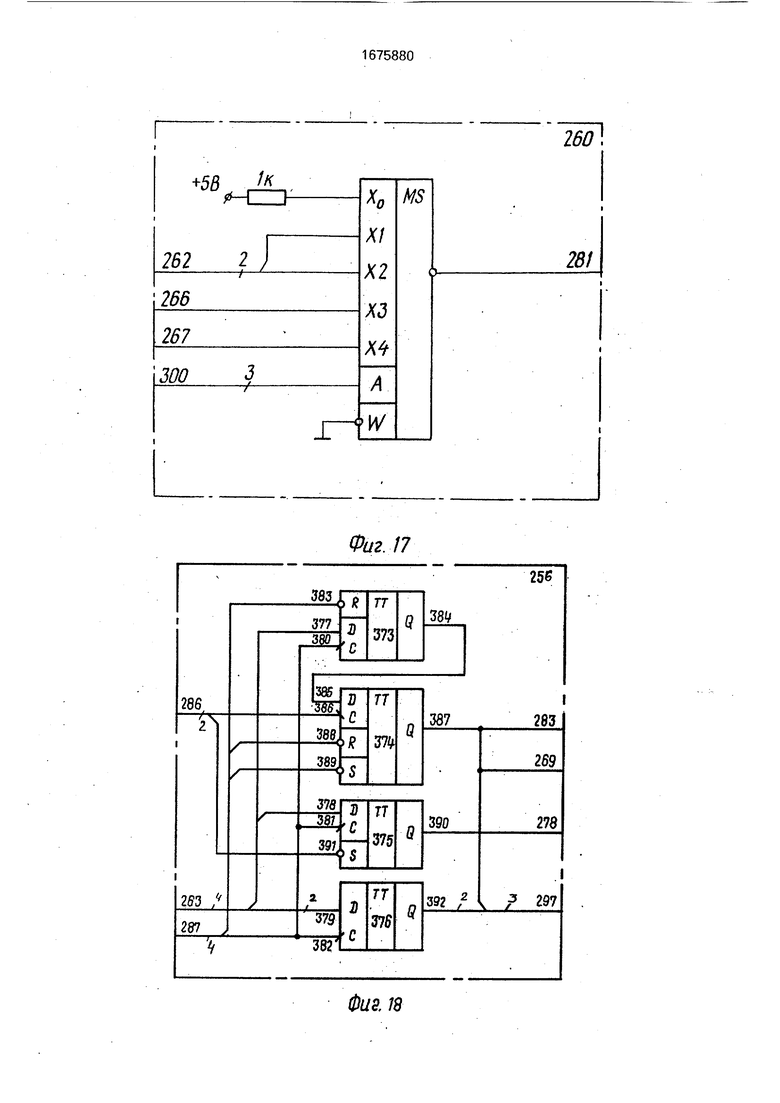

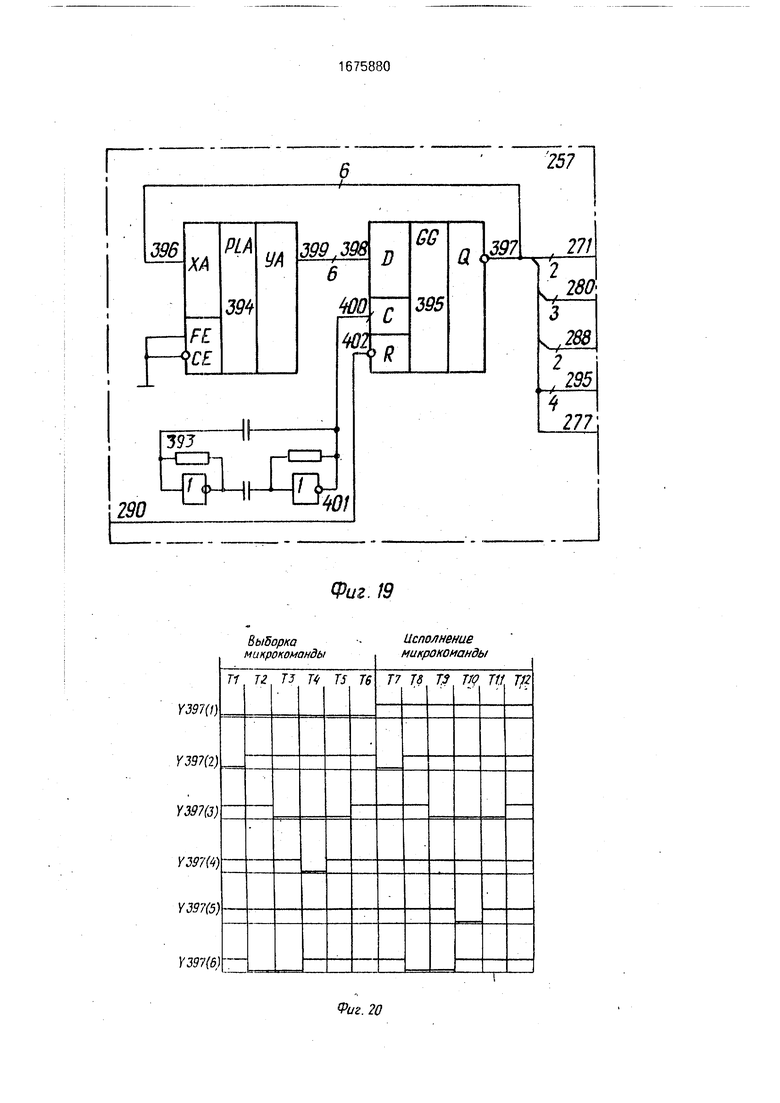

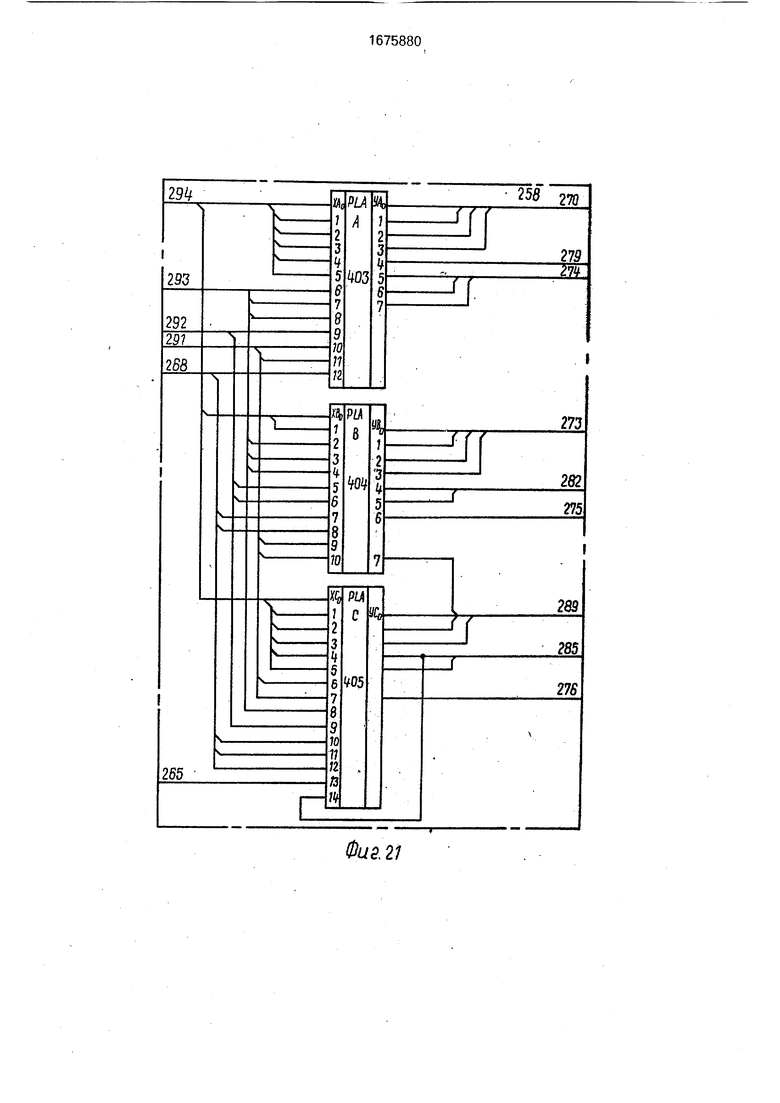

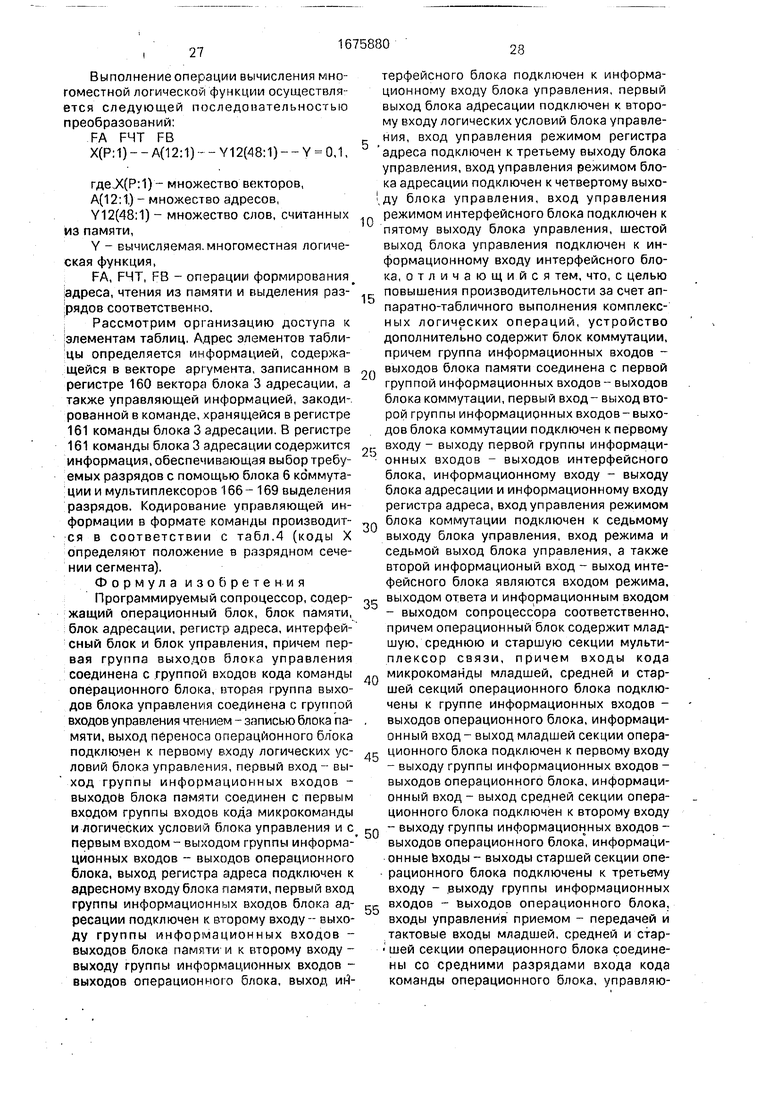

связи; на фиг.8 - структурная схема блока памяти; на фиг.9 - функциональная схема 16-разрядной секции блока памяти; на фиг. 10 - структурная схзма блока коммутации; на фиг. 11 - функциональная схема блока коммутации; на фиг.12 - функциональная схема регистра адреса; на фиг.13 - пример реализации мультиплексора адреса микро-, команды; на фиг. 14 - функциональная схема мультиплексора адреса; на фиг.15 -функциональная схема блока селекции адреса; на фиг. 16 - функциональная схема регистра микрокоманд блока управления; на фиг.17 - пример реализации мультиплексора условий; на фиг, 18 - функциональная схема группы триггеров; на фиг.19 - функциональная схема узла синхронизации; на фиг.20 - временная диаграмма работы блока синхронизации; на фиг.21 - пример реализации блока постоянной памяти; на фиг.22 - функциональная схема интерфейсного блока.

Программируемый сопроцессор (фиг.1) содержит операционный блок 1, блоки паО Ч

ел

00 00

о

мяти 2 и адресации 3, интерфейсный блок 4, блоки управления 5 и коммутации 6 и регистр 7 адреса, связи 8-41 внутри процессора.

Операционный блок 1 (фиг.2) содержит три секции (младшую 42, среднюю 43 и стар- шую 44), мультиплексор 45 связи и связи 46 - 74 внутри блока.

Младшая 42, средняя 43 и старшая 44 секции операционного блока содержат (фиг.З) приемопередатчик 75(мультиплексор 76 данных, регистры-операнда 77, числа 78 и команды 79, арифметико-логический узел 80, мультиплексоры выхода 81 и адреса данных 82, регистр 83 микрокоманды, группу элементов И 84, первый - третий элементы И 85 - 87, группу элементов ИЛИ 88, элемент ИЛИ 89 и группу элементов НЕ 90, связи 91 - 157 внутри секции.

Блок 3 адресации (фиг.4) содержит приемопередатчик 158, регистры данных 159, вектора 160, команды 161, макрокоманды 162 и адреса микрокоманды 163, триггер

164модификации адреса, мультиплексор

165адреса микрокоманды, мультиплексоры выделения восьми, четырех и одного разрядов 166 - 169 соответственно, мультиплексор 170 адреса, первый 171 и второй 172 элементы ИЛИ, группу элементов ИЛИ 173, первый - четвертый элементы И 174 - 177 и первую 178 и вторую 179 группы элементов И, связи 180 - 254 внутри блока (связь 242 не показана).

Блок 5 управления (фиг.5) содержит блок 255 селекции адреса, группу 256 триггеров, блок 257 синхронизации и блок 252 постоянной памяти, регистр 259 микрокоманды блока управления, мультиплексор 260 условий и связи 261 -302 внутри блока.

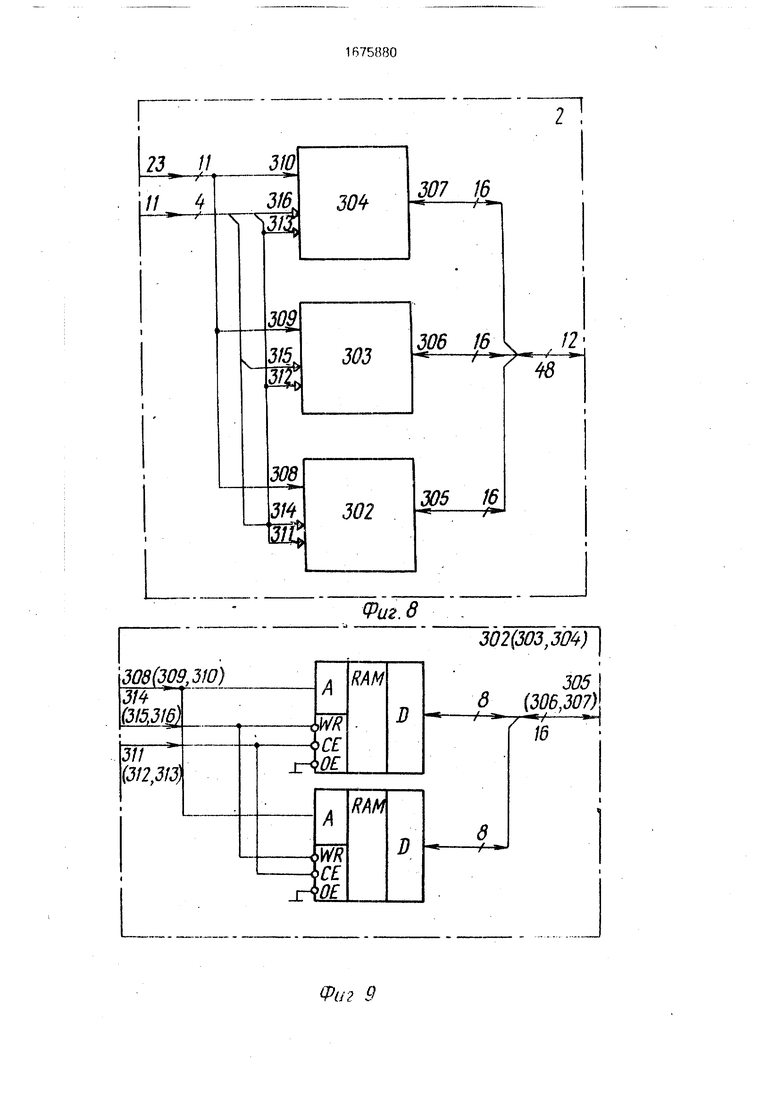

Блок памяти (фиг.8) содержит три секции 302 - 304 и связи 305 - 316 внутри блока.

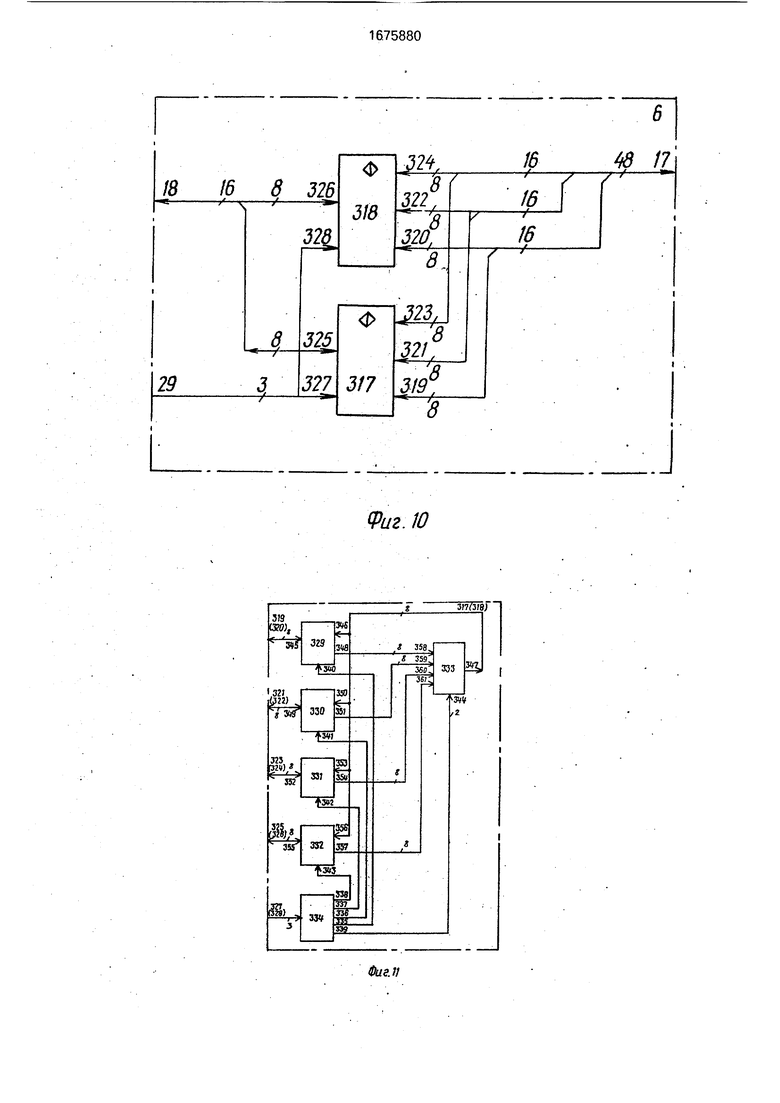

Блок коммутации (фиг. 10) содержит универсальные вентильные матрицы 317 и 318 и связи 319 - 328 внутри блока.

Универсальная вентильная матрица блока коммутации (фиг.11) содержит приемопередатчики 329 - 332, четырехканаль- ный 8-разрядный мультиплексор 333, узел 334 управления и связи 335 - 361 внутри матрицы.

Узел селекции адреса блока управления (фиг.15) содержит программируемую логическую матрицу 362, регистр 363 и связи 364 - 372 внутри блока.

Группа триггеров (узел состояний) блока управления (фиг. 18) содержит триггеры 373 - 376 и связи 377 - 392 внутри группы триггеров.

0

0

55

0

Узел синхронизации блока управления (фиг. 19) содержит генератор 393 тактовых импульсов, программируемую логическую матрицу 394, регистр 395 и связи 396 - 402 внутри узла. -Узел постоянной памяти (фиг.21) содержит программируемые логические матрицы 403 - 405.

Блоки сопроцессора (фиг.1) работают следующим образом.

Операционный блок 1 (фиг.1) предназначен для выполнения основных операций по преобразованию и оперативному хранению информации. Пример построения 48- разрядного операционного блока путем соответствующего объединения по цепям переносов и сдвигов трех однотипных секций приведен на фиг.2. Секция операционного блока реализована в виде бис К18018П1-112 (фиг.З).

Управление операционным блоком происходит при помощи управляющего кода С3(8:1) Y8(8:1), формируемого в блоке 5 управления.

Приемопередатчик 75 предназначен для организации двунаправленной передачи информации, управление вводом - выводом приемопередатчиков 75 различных секций независимое:

С95 С49 С9 (1) Y8(1) Y270(1) - младшая секция 42,

С95 С50 С9(2) Y8(2) Y270(2) - средняя секция 43,

С95 - С51 С9(3) Y8(3) Y270(3) - старшая секция 44,

С95 0 - Y107(16:1) Х91(16:1) - ввод информации,

С95 1 - Y91(16:1)-X101(16:1) - вывод информации из секции операционного блока.

Содержание микрооперации, выполняемой в операционном блоке 1, определяется микрокодом, записанным в регистр 83 микрокоманды операционного блока. Микрокод поступает из блока 2 памяти в цикле выборки микрокоманды и фиксируется в регистре 83 микрокоманды операционного блока при помощи сигнала записи С96:

(3)C53(3)C54(3)C9(5)Y8(5) Y271(1).

В регистре 83 микрокоманды операционного блока хранится следующая информация:

С115(3:1) - Y116(3:1)- управление мультиплексором 76 данных,

C137(2:1) Y138(2:1) -управление мультиплексором 82 выхода,

С155 Y156 - управление модификацией адреса,

С148 Y151 - разрешение записи в регистр 77 операнда,

С149 Y152 - разрешение записи в регистр 78 числа

С150 Y153 - разрешение записи в регистр 79 команды операционного блока.

Между полями кода микрокоманды, считываемой из блока 2 памяти (Y12), и информацией, записываемой в регистр 83 микрокоманды операционного блока, выполняется следующее соответствие:

(28),

Y152 Y12(27),

Y153 Х92(8) Х62(8) Y 12(26) - старшая секция 44,

Y163 Х92(8) Х63(8) Y 12(25) - средняя секция 43,

Y153 Х92(8) Х64(8) Y 12(24) - младшая секция 42,

Y116(3:1) Y12(23:21),

Y138(2:1) Y12(20:19),

Y156 Y12(18).

Мультиплексор 76 данных предназначен для передачи информации в регистр 77 операнда, регистр 78 числа или регистр 79 команды операционного блока по одному из восьми каналов, код номера которого за- дается в формате микрокоманды:

С115(3:1) 000 - Y120(16:1) Х103(16:1)

-прямая передача,

С115(3:1) 001 -Y12(16:1) X111(16:1)- сдвиг влево на 1Р,

С115(3:1) 010-Y12() X112(16:1)- сдвиг влево на 2Р,

С115(3:1) 011 -Y120(16:1) X113(16:1)

-сдвиг вправо на 1Р,

С115(3:1) 100-Y120(16:1) X114(16:1)

-сдвиг вправо на 2Р,

С115(3:1) 101 - Y120(16:1) X106(16:1)

-инверсная передача,

С115(3:1) 110-Y120(16:1) X105(16:1)

-дизъюнкция,.

С .15(3:1) 111 - Y120(16;1) Х104(16:1)

-конъюнкция.

Для формирования функций инверсии, дизъюнкции и конъюнкции служат группы логических элементов НЕ 90, ИЛИ 88 и И 84. Для реализации функции сдвигов в секции операционного блока поступают следующие сигналы:

Х65 (2:1) Х47(2:1), Х69(2:1) Х72(2:1)

-на младшую секцию 42,

Х66 (2:1) Х48(2:1), Х70(2:1) - Х46(16:15)- среднюю секцию 43,

X67 (2:1) Y68(2:1),X71(2:1)X47(16:15)

-на старшую секцию 44.

Регистр 77 операнда и регистр 78 числа предназначены для временного хранения операндов и построены на сдвоенных D- триггерах, управляемых перепадом потенциала.

Регистр 79 команды операционного блока предназначен для хранения адресных полей кода команды: адреса первого операнда - младшая секция 42 операционного блока, адреса второго операнда - средняя секция 43 операционного блока, адреса перехода к следующей команде - старшая секция 44 операционного блока, независимое управление разрешением записи в регистр 79 команды операционного блока осуществляется при помощи кода Y12(26:24), задаваемого в формате микрокоманды. Имеется возможность модификации кода на выходе регистра 79 команды операционного блока. Модифицируется младший разряд кода при помощи логического элемента ИЛИ 89 и сиг- нала разрешения модификации адреса Y155, поступающего из регистра 83 микрокоманды операционного блока: Y143 Y142( l) + Y155.

Арифметико-логический узел 80 представляет собой комбинационную схему, формирующую в зависимости от поступающего на его входы содержимого .регистров операнда 77 и числа 78 и сигнала входного переноса Х55(58,59) коды суммы Y135, суммы по модулю 2 Y136, а также сигналы выходного переноса Y60(61,57):

Y135(16:1) X127(16:1) + X12(16:1) + X55,

Y136(16:1) X127(16:1) + X128(16:1).

Функциональная схема арифметико-логического узла приведена на фиг.7. В качестве сигналов входного переноса Х55 в младшую секцию 42 операционного блока поступает сигнал Y272(2) с выхода регистра 259 микрокоманды блока 5 управления Х55 С9(8) Y8(8) Y 272(2), в среднюю секцию 43 - сигнал выходного переноса Y60 младшей секции 42 операць онного блока Х58 Y60, в старшую секцию 44 - сигнал выходного переноса Y61 средней секции 43 опе- реционного блока Х59 Y61.

Сигнал выходного переноса Y57 стар- шей секции 44 операционного блока является одним из условий перехода в микропрограммах и поступает на вход Х266 мультиплексора 260 условий перехода блока 5 управления.

Мультиплексор 81 выхода предназначен для коммутации на выход Y140 информации по одному из четырех направлений в зависимости от кода С137(2:1) Y.138(2:1), записанного в регистре 83 микрокоманды операционного блока:

С137(2:1) 00 - Y140(16:1) Х132(16:1) - регистр 78 числа,

C137(2:1)01-Y140(16:1) X131(16:1)- регистр 77 операнда,

С137(2:1) 10-Y140(16:1) X134(16:1)- сумма по модулю 2,

С137(2:1) 11 - Y140(16:1) X135(16:1)- сумма.

Информация с выхода Y140 мультиплексора 81 выхода поступает на вход мультиплексора 82 адресных данных, а также на группы логических элементов И 84 и ИЛИ 88.

Мультиплексор 82 адреса данных коммутирует на выход 102 информацию по одному из двух каналов в зависимости от кода С97 С52(1) С53(1) С54(1):

. С97 0 - Y102(16:1) Х139(16:1) - мультиплексор 81 выхода,

С97 1 - Y102(16:2) Х141(1б:1) - регистр 79 команды.

Информация с выхода 102 мультиплексора 82 адреса данных поступает на вход 101 приемопередатчика 85.

Мультиплексор 45 связи (фиг.2) предназначен для организации сдвиговых операций совместно с секциями 42 - 44 операционного блока, с его помощью реализуются следующие типа сдвигов: «логический сдвиг влево на 1 разряд, логический сдвиг влево на 2 разряда, арифметический сдвиг вправо на 1 разряд, арифметический сдвиг вправо на 2 разряда, циклический сдвиг влево на 1 разряд, циклический сдвиг влево на 2 разряда, циклический сдвиг вправо на 1 разряд и циклический сдвиг вправо на 2 разряда. Мультиплексор 45 связи представляет собой двухканальный четырехразрядный мультиплексор, на управляющий вход 56 которого поступает сигнал С56 С9(7) Y8(7) Y8(7) Y272(1) с выхода 272 регистра 259 микрокоманды блока 5 управления:

С56 0 - логические и арифметические сдвиги;

С56 1 - циклические сдвиги.

На информационные входы 73 и 74 поступают соответственно по два старших и младших разряда информационного входа - выхода 13:

Х73(2:1) Х46(2:1) Х13(2:1),

Х74(2:1) Х48(16:15) Х13(48:47).

Выходные коды Y68, Y72 поступают на входы Х67 старшей 44 и Х69 младшей 42 секций операционного блока 1 соответственно. Мультиплексор 45 связи может быть реализован, например, на микросхеме мультиплексора К555КП11 (фиг.8).

Блок 2 памяти (фиг.9) содержит младшую 302, среднюю 303 и старшую 304 16- разрядные секции блока памяти, соединенные соответствующим образом по

информационным входам - выходам с младшей 42, средней 43 и старшей 44 секциями операционного блока 1:

Х305(16:1) Y12(16:1) Y13(16:1) Х46(16:1),

Х306(16:1) Y12(31:17) Ґ13(31:17) Х47(16:1),

Х307(16:1) Y12(48:33) Y13(48:33) Х48(16:1).

Адрес А поступает параллельно на все секции блока памяти: Х308(11:1) Х309(11:1 X310(11:1) X23(11;1) Y22(11;1) A.

Управляющий код С11(4:1) формируется в блоке 258 постоянной памяти блока 5 уп- равления. Сигнал выбора кристалла С11(1) поступает параллельно на все секции памяти:

С311 C312 C313 C11(1) Y273(1).

Сигналы разрешения записи С11(4:2) поступают индивидуально на каждую секцию блока памяти, это позволяет производить запись в любую секцию блока памяти:

С314 С11(2) Y273(2) - в младшую секцию 302,

С315 С 12(3) Y273(3) - в среднюю секцию 303,

С316 С11(4) Y273(4) - в старшую секцию 304.

Секции памяти могут быть реализованы, например, на БИС ОЗУ КР537РУ10 (фиг. 10).

Секция памяти (например, младшая

302) может работать в зависимости от управляющих кодов (например, для младшей

секции 302 - С314 и С311) в следующих

режимах:

00 - Y305(16:1) R - режим хранения информации, 10-Y305(16:1) БП(А) - режим чтения,

11 - БП(А) Х305(16:1)- режим записи,

где БП(А) - содержимое ячейки памяти с адресом А.

Переменные на выходе Y305 могут при- нимать три значения: 10,1, R1, где R - состо- яние большого выходного сопротивления.

Блок 6 коммутации (фиг.11) предназначен для реализации необходимых связей между шинами внутреннего интерфейса, блок 6 коммутации представляет собой комбинационную схему, реализованную на двух БИС К18018ПМ11 (блоки 317 и 318), изготовленных на базе универсальных вентильных матриц. Функциональная схема блока З17.(318) приведена на фиг.11.

Первый 48-разрядный информационный вход - выход 17 блока 6 коммутации образуется объединением шести восьмиразрядных входов - выходов блоков 317 и 318:

Y17(48:1) Y324(8:1) Ф Х323(8:1)Ф -Х322(8:1) X321(8:1)X320(8:1)X319(8:1).

Второй 16-разрядный информационный вход - выход 18 блока б коммутации образуется объединением двухв-разрядных 5 входов - выходов блоков 317 и 318:

Х18(16:1) Х32б(8:1) + Х325(8:1).

В зависимости от управляющего кода

С327(3:1) С328(3:1) С29(3:1) Y33(3:1)

осуществляются следующие режимы 10 работы:

000-Y18(16:01) Y17(48:33) Y17(32:17)- -(16:01),

001-Y18(16:01) Y17(48:33) Y17(16:01)r Х17(32:17),15

010-Y18(16:01) Y17(32:17) Y17(16:01)- X17(4§:33),

011-Y17(48:33) Y17(32:17) Y17(16:01)-- X18(16:01).

100-Y18(16:01) X17(16:01),20

101 -Y18(16:01) X17(32:17),

110-Y18(16:01) X17(43:33),

111 - Y18(16:01) R, Y17(48:01) R - нет передачи,

где R - состояние большого выходного 25 сопротивления; X - входной код; Y - выходной код.

БИС К18018П1-111 является многофункциональной. На структурной схеме фиг. 12 приведена лишь часть полной структурной 30 схемы БИС, реализующая необходимые режимы коммутации. На ней изображены че- тыре приемопередатчика 329 - 332, четырехканальный 8-разрядный мультиплексор 333, блок 334 управления. Приеме- 35 передатчики 329 - 332 могут работать либо в режиме ввода, либо в режиме вывода, в режиме ввода состояние входов - выходов аналогично третьему состоянию.

Выбор данного из четырех каналов 40 мультиплексора 333 осуществляется с помощью 2-разрядного управляющего кода. Формирование внутренних управляющих сигналов на входах 335 - 339, поступающих соответственно на управляющие входы 340 45 - 343 приемопередатчиков 329 - 332 и управляющий вход 344 мультиплексора 333, происходит в блоке 334 управления. Алгоритм формирования управляющих сигналов соответствует логическим функциям, пред- 50 ставленным в табл.1.

Рассмотрим работу приемопередатчиков 329 - 332:

С340 0 - Y319(8:1) Y345(8:1) X346(8:1) Y347(8:1), 55

С340 1 - Y348(8:1) X345(8:1) Y319(8:1),

C341 0 - Y321(8:1) Y349(8:1) X350(8:1) Y347(8:1),

C341 1 - Y351{8.1) X349(8.1) - X321(8:1),

C342 0 - Y323(8:1) Y352(8:1) - X353(8:1) Y347(8.1).

C342 1 - Y354(8:1) X352(8:1) X323(8:1).

C343 0 - Y325(8:1) Y355(8:1) - X356(8:1) Y347(8:1),

C343 t - Y357(8:1) X355(8:1) X325(8:1).

Код у правления С344(2:1) мультиплексором 333 определяет следующие режимы коммутации:

€344(2:1) 00 - Y347(8:1) Х358(8М) Y348(8:1),

С344(2:1) 01 - Y347(8:1) Х359(8:1) Y351(8:1),

С344(2:1)10-Y347(8:1)X360(8:1)Y35f(8:1) . С344(2:1) 11 - Y347(8:1) 361(8:1) Y357(8:1).

Схема сравнения управления синтезирована на элементах из библиотеки элементов базовых ячеек БМК К1801ВП1-111 (ШИО.010.045) по известной методике синтеза комбинационных схем.

Регистр 7 адреса предназначен для формирования адреса в различных оежимах работы: пассивном и активном. В активном режиме работы сопроцессора адресная информация от различных источников адреса, находящихся в блоке 3 адресации или секциях 42 - 44 операционного блока, поступает через блок 6 коммутации на вход 21 регистра 7 адреса (фиг.1). В пассивном режиме адресная информация от системной магистрали поступает через инфтерфейс- ный блок 4 на вход 21 регистра 7 адреса, фиксация адресной информации осуществляется при помощи сигнала записи С30(1) Y34(1) Y276. Адрес с выхода 22 регистра 7 адреса поступает на адресный вход 23 блока 2 памяти: Х23(11:1) Y22(11:1).

Регистр 7 адреса может быть реализован на микросхемах К555ТМ9 (фиг.13).

Блок 3 адресации (фиг.4) предназначен- для формирования адреса микрокоманды: адреса фиксированных ячеек памяти (регистров общего назначения - РОН), обращение к которым возможно на микрокомандном уровне адресов обращений к таблицам сложных логических преобразований, а также для выделения разрядов при выполнении логических преобразований. Блок 3 адресации реализован на БИС БМК К18018П-113. Функциональная схема приведена на фиг.5.

Приемопередатчик 158 блока 3 адресации предназначен для организации двунап- равленной передачи информации по 16-разрядной магистрали. Управление направлением передачи осуществляется при помощи сигнала С181 С31(1) Y35(1) Y279:

О-Y195(16:1)X180(1.6:1)-ввод информации в блок 3 адресации,

1 - Y180(16:1) Х192(16:1) - вывод информации.

Содержание микрооперации, выполняемой в блоке 3 адресации, определяется микрокодом, записанным в регистр 162 микрокоманд блока адресации. Микрокод поступает из блока 2 памяти (фиг.1) в цикле выборки микрокоманд и фиксируется в регистре 162 микрокоманды блока адресации при помощи сигнала записи С182 С31(3) Y35(3), поступающего с выхода 35 блока 5 управления. Микрокод, хранящийся в регистре 162 микрокоманды блока адресации весь цикл исполнения микрокоманды, предназначен для управления записью в регистры данных 159, адреса микрокоманды 163, команды 161, вектора 160, а также для задания адресов РОН, информация на вход 206 регистра 162 микрокоманды блока адресации поступает через приемопередатчик 158 с информационного входа - выхода 20: X206(11:1) Y195(11:1) X20(11:1) Y18(11:1) Y12(11:1).

В фазе выборки микрокоманды блок 6 коммутации настроен на передачу кода микрокоманды из младшей секции 302 блока 2 памяти: X20(16:1) Y18(16:1) Y12(16:1).

Принято следующее распределение полей в формате микрокоманды, поступающей в блок 3 адресации:

Y12(11:10) - управление мультиплексором 170 адреса,

Y12(9) - разрешение записи в регистр 163 адреса микрокоманды,

Y12(8) - разрешение записи в регистр 161 команды,

Y12(7) - разрешение записи в регистр 160 вектора,

Y12(6) - разрешение записи в регистр 159 данных,

Y12(5:1)- номер РОН. Мультиплексор 165 адреса микрокоманды, регистр 163 адреса микрокоманды, триггер 164 модификации адреса следующей микрокоманды, логический элемент ИЛИ 172 предназначены для формирования адреса следующей микрокоманды. Мультиплексор 165 адреса микрокоманды представляет собой двухканальный мультиплексор, управляемый при помощи сигнала С183 C31(2)OY35(2)0280(1), поступающего с выхода 35 блока 5 управления: О - Y208(9:1) (6:1), где Х211(6:1) Х24(13:12) Х24(4:1) -Y12(48:47) 4-Y12(32:31) -Ф- Y12(16:15) - код

операции команды, поступающий при исполнении микрокоманды Выборка команды ;

1 - Y208(9:1) Х24(13:5) Y8(48:40) адрес перехода к следующей микрокоманде, поступающий при выборке любой микрокоманды.

Выход 208 мультиплексора 165 адреса микрокоманды подключен к информацион0 ному входу 207 регистра 163 адреса микрокоманды. Функциональная схема мультиплексора 165 адреса микрокоманды приведена на фиг.14,

Регистр 163 адреса микрокоманды

5 представляет собой 9-разрядный регистр, на информационный вход 207 которого поступает информация с выхода 208 мультиплексора 165 адреса микрокоманды и фиксируется в нем при помощи управляю0 щего сигнала .

Выход 234 регистра 163 адреса микрокоманды подключен к входу 233 соответствующего канала мультиплексора 170 адреса, возможна модификация адреса мик5 рокоманды с целью реализации условных переходов в микропрограммах, модифицируется младший разряд адреса с использованием триггера 164 модификации адреса и логического элемента ИЛИ 172, запись в

0 триггер 164 модификации адреса происходит в фазе исполнения микрокоманды при помощи управляющего сигнала С190 С31(4) Y35(4) Y280(3), на информационный вход 191 триггера 164 модификации

5 адреса поступает сигнал с выхода 281 мультиплексора 260 условий перехода блока 5 управления (фиг.5): Х191 С31(5) Y35 Y281,

Y235 Y234(1) + Y245.

0 Регистры данных 159, вектора 160 и команды 161, мультиплексоры 166 - 169 выде- ления разрядов, группа логических элементов И 179 и группа логических элементов ИЛИ 173 предназначены для реали5 зации функций обращения к элементам таблиц сложных логических преобразований и выделения разрядов.

Регистр 159 данных предназначен для фиксации 16-разрядного кода, поступающе0 го с выхода 18 блока 6 коммутации (фиг.1) через вход - выход 20 и приемопередатчик 158, мультиплексоры 166 - 169 выделения восьми, четырёх, двух и одного бита служат для каскадного выделения разрядов из ин5 формации в регистре 158 данных. На выходе- мультиплексора 169 выделения бита формируется выделенный бит, поступающий на выход 27 и далее на вход 267 мультиплексора 260 условий перехода блока 5 управления. Данный сигнал является одним из

условий перехода в микропрограммах. Восьми- или четырехразрядный вектор может быть записан в регистр 160 вектора, Вторая группа логических элементов И 179 управляет записью в регистр 160 вектора 5 старших четырех разрядов вектора, поступающего с выхода 223 мультиплексора 166 выделения 8 бит. Работа перечисленных блоков осуществляется следующим образом:10

С213 Y217(4), C214 Y217(3), C215 С254 Y217(2), C216 Y217(1), C213 0 - Y223(8:1) Y220(8:1), C213 1 -Y223(8:1) Y220(16:9), C214 0-Y200(4:1) Y223(4:1),15

C214 1 - Y200(4:1) Y223(8:5), C215 0 - Y228(2:1) Y200(2:1), C215 1 - Y228(2:1) Y200(4:2), C216 0- Y229 Y228(1), C216 1 - Y229 Y228(2),20

C254 0-Y199(4:1) 0000, C254 1 - Y 199(4:1) Y223(8:5), X198(8:1) Y199(4:1) + Y200(4:1). Регистр 160 вектора предназначен для хранения 8- или 4-разрядного вектора при 25 выделении разрядов, а также для формирования адреса при обращении к таблицам сложных логических преобразований от вектора двоичных переменных, информация о месте расположения таблиц преобра- 30 зований кодируется в поле Б команды, записанном в регистре 161 команды. Сформированный адрес поступает на вход 236 мультиплексора 170 адреса. Он образуется следующим образом:35

Х236(12:1) Y217(14:11) 4- Y237(8:5)4- (4:1),

Y238(4:1) X247(4:1) + X246(4:1), X246(4:1) Y217(10:7).

Мультиплексор 170 адреса предназна- 40 чен для организации вывода информации, записанной в различные регистры блока 3 адресации. Мультиплексор 170 адреса представляет собой 4-канальный 16-разрядный мультиплексор, на выходе 193 которого 45 коммутируется информация в зависимости . от управления кода С239(2:1), формируемого следующим образом:

С188 0 - С239(2:1) Х252(2:1)

С выхода 193 мультиплексора 170 адреса информация поступает на вход 192 приемопередатчика 158. Функциональная схема мультиплексора 170 адреса приведена на фиг.15.

Блок 5 управления (фиг.5) работает следующим образом.

Блок 255 селекции адреса предназначен для опознавания адреса угла 256 состояния и области адресов окна памяти сопроцессора в адресном пространстве. микроЭВМ. Блок 255 селекции адреса состоит из селектора адреса и регистра 363 выбора устройства (фиг. 16). Селектор адреса может быть построен, например, на БИС ПЛМ КР556Р12, а регистр 363 выбора устройства - на микросхеме К555ТМВ. На вход 264 блока 255 селекции адреса, связанный с входом 364 селектора адреса, поступает адресная информация с выхода 25 интерфейсного блока 4. С выходов 365 и 366 селектора адреса сигналы поступают соответственно на выходы 367 и 368 регистра 363 выбора устройства, в котором они фиксируются при помощи сигнала записи С369 С284(2) Y285(2), поступающего с выхода 285 блока 258 постоянной памяти (фиг.5).

После окончания цикла обмена информацией микроЭВМ с сопроцессором регистр 363 выбора устройства переходит в начальное состояние по сигналу сброса С370 С284(1) В285(1). поступающему с выхода 285 блока 253 постоянной памяти.

При настройке узла 255 селекции адреса на выбор адреса узла 256 состояния (174762) и диапазона адресов окна памяти сопроцессора (164000....167777), причем значения адресов приведены в восьмеричной системе счисления, его работа может быть описана следующей системой логических уравнений (при передаче кода адреса активным является низкий уровень сигнала): -

Y365 Y264(16) 4- Х264(15) 4- Х264(14)- 4X264(13) 4- Х2 64(12)4-Х2 64(11 )-Ф-Х2 64(10}Ј

Ф-Х2 64(9) ФХ264(8)Х2 64(7)-

(6) 4 Х264(5) -Ф- Х264(4) -Ф- Х264(3) Х264(2)4Х264(1).

Y232(11:10),50

С188 1 -С239(2:1) 11,Y366 Х264(16) 4- Х264(15) Х264(14)4С239 00 - Y193(16:1) Y220(16:1),(13)X264(12).

С239 01 - Y193(16:1) OOOCrt Реализация данной системы логических

4 -Х236(12:1).функций на одной БИС ПЛМ К556РТ2 - триС239 10 - Y193(16:1) 000000100Ф-55 виальная. Регистр 259 микрокоманды блока 4V232(5:1),управления (фиг.5) предназначен для хранеС239 11 - Y193(16:1) 00000004- ния части кода микрокоманды, поступающе- фХ233(9:1),го в цикле выборки микрокоманды из блока

Х233(9:1) Y234(9:2) + Y235.2 памяти. Регистр 259 микрокоманды блока

управления может быть реализован, наприС выхода 193 мультиплексора 170 адреса информация поступает на вход 192 приемопередатчика 158. Функциональная схема мультиплексора 170 адреса приведена на фиг.15.

Блок 5 управления (фиг.5) работает следующим образом.

Блок 255 селекции адреса предназначен для опознавания адреса угла 256 состояния и области адресов окна памяти сопроцессора в адресном пространстве. микроЭВМ. Блок 255 селекции адреса состоит из селектора адреса и регистра 363 выбора устройства (фиг. 16). Селектор адреса может быть построен, например, на БИС ПЛМ КР556Р12, а регистр 363 выбора устройства - на микросхеме К555ТМВ. На вход 264 блока 255 селекции адреса, связанный с входом 364 селектора адреса, поступает адресная информация с выхода 25 интерфейсного блока 4. С выходов 365 и 366 селектора адреса сигналы поступают соответственно на выходы 367 и 368 регистра 363 выбора устройства, в котором они фиксируются при помощи сигнала записи С369 С284(2) Y285(2), поступающего с выхода 285 блока 258 постоянной памяти (фиг.5).

После окончания цикла обмена информацией микроЭВМ с сопроцессором регистр 363 выбора устройства переходит в начальное состояние по сигналу сброса С370 С284(1) В285(1). поступающему с выхода 285 блока 253 постоянной памяти.

При настройке узла 255 селекции адреса на выбор адреса узла 256 состояния (174762) и диапазона адресов окна памяти сопроцессора (164000....167777), причем значения адресов приведены в восьмеричной системе счисления, его работа может быть описана следующей системой логических уравнений (при передаче кода адреса активным является низкий уровень сигнала): -

Y365 Y264(16) 4- Х264(15) 4- Х264(14)- X264(13) 4- Х2 64(12)4-Х2 64(11 )-Ф-Х2 64(10}Ј

-Х2 64(9) ФХ264(8)Х2 64(7)-

(6) 4 Х264(5) -Ф- Х264(4) -Ф- Х264(3) Х264(2)4Х264(1).

мер, на микросхемах К555ТМ9 (фиг. 17). Информация фиксируется в регистре 259 микрокоманды блока управления при помощи сигнала записи С299, поступающего из блока 257 синхронизации: С299 Y277.

Выполняется следующее соответствие между полями кода микрокоманды, считываемой из блока 2 памяти, и информацией, записываемой в регистр 259 микрокоманды блока управления:

Y298(6:1) Х261(6:1) Y12(17:12) - код режима сопроцессора, поступает в блок 22 формирования управляющих сигналов,

Y272(2) Х261(7) Y12(36) - входной. перенос, поступает в младшую секцию 42 операционного блока,

Y272(1) Х261(8) Y12(35) - признак циклических сигналов, поступает в мультиплексор 45 связи,

Y301(3:1) Х261(11:9) Y12(39:37) - код управления мультиплексором условий, поступает в мультиплексор 260 условий.

Мультиплексор 260 условий (фиг..5) предназначен для реализации безусловных и условных переходов в микропрограммах и может быть реализован, например,на микросхеме К555КП7 (фиг. 18). Мультиплексор 260 условий выполняет функции коммутации на выход, 281 одной из двоичных пере- менных, подаваемых на его входы в зависимости от управляющего кода:

C300 Y301(3:1),

000- безусловный переход,

001- Х262(2) Х14(10) Y12(48) - старший разряд,

010-X262(1) X14(1) Y12(1)-младший, разряд,

011 -X266 X16 Y15- выходной перенос,

100 - Х267 Х28 Y27 - выделенный бит.

Выход 281 мультиплексора 260 условий через вход 31 блока 3 адресации соединен с информационным входом 191 (фиг.4) триггера 164 модификации адреса микрокоман- . ДЫ.

Группа 256 триггеров (фиг. 18) служит для задания режима работы сопроцессора из микроЭВМ и хранения осведомительных сигналов о состоянии сопроцессора, опрашиваемых микроЭВМ. Узел 256 состояния (фиг. 18) содержит пять триггеров 373 - 375 и 376-1, 376-2. Информация из микроЭВМ поступает из интерфейсного блока 4 на D- входы триггеров 373, 375, 376-1, 376-2:

Х377 Х263(2) Х26(3) Y25(3) Y41(3),

Х378 Х263(1) Х26(2) Y25(2) Y41(2),

Х379(2:1) Х263(4:3) Х26(5:4) Y25(5:4 Y41(5:4).

Запись в триггеры 373 - 276 синхронизирована сигналом записи, поступающим из узла 258 постоянной памяти на С-входы 380, 381, 382: С380 С381 - С382 С287(1)

Y289(1).

Первый триггер 373 служит для перевода сопроцессора в пассивный режим работы, такой перевод возможен со стороны микроЭВМ и со стороны сопроцессора. Для

перевода сопроцессора в пассивный режим со стороны микроЭВМ на D-вход 377 поступает сигнал низкого уровня требования останова по концу микрокоманды. Для перехода сопроцессора в пассивный режим

по своему требованию в узле формирования управляющих сигналов выдается сигнал требования останова со стороны сопроцессора, поступающий на R-вход 383 первого триггера 373: С383 С287(3) Y289(3).

На выходе 384 первого триггера 373

формируется общее требование останова (низкий уровень), поступающее на D-вход 385 второго триггера 374. Запись в триггер 374 синхронизирована сигналом конца исполнения микрокоманды, формируемым инвертированием сигнала С286(1):

С386 С286(1); С286(1) С288(1). При записи сигнала требования остано- ва Х385 сопроцессор переходит в пассивный режим работы, о чем свидетельствует сигнал на выходе Х387 1 триггера 374 (низкий уровень). Информация о режиме работы с выхода 387 поступает на выходы 269, 283 и 297 группы 256 триггеров: Y387 Y269 Y383 Y297(3).

Переход в пассивный режим возможен и по сигналу начальной установки, поступающему из системной магистрали 38 через узел 258 постоянной памяти на R-вход 388 триггера 374: С388 С287(4) Y289(4).

Переход в активный режим Х387 О (высокий уровень) возможен по сигналу установки в активный режим, поступающему из узла 258 постоянной памяти на S-вход 389 триггера 374: С389 С287(2) Y289(2). Третий триггер 375 предназначен для формирования сигнала Пуск, по которому формируется начальный адрес в регистре 7 адреса, начинается сигнал н,а выходе 390 при записи по D-входу 378 сигнала из микроЭВМ, заканчивается - в такте выборки микрокоманды по сигналу записи в регистр микрокоманды, формируемому в блоке 257 синхронизации: С391 C28G(2) - Y288(2). . Сигнал Пуск с выхода 390 поступает на выход 278 узла 256 состояний и далее на вход 30 регистра 7 адреса: Y278 Y390.

Четвертый 376-1 и пятый 3 6-2 триггеры предназначены для указания номера секции блока 2 памяти, к которой происходит обращение от микроЭВМ в пассивном режиме работы. С выхода 392 данная информация поступает на выход 297 группы 256 триггеров.

На выходе 297 формируется 3-разрядный код Y297(3:1), поступающий в узел 258 постоянной памяти: Х293(3:1) Y297(3:1) У387ФУ392(2:1).

Группа 256 триггеров может быть реализована, например, на микросхемах триггеров К555ТМ2 или К555Т81.

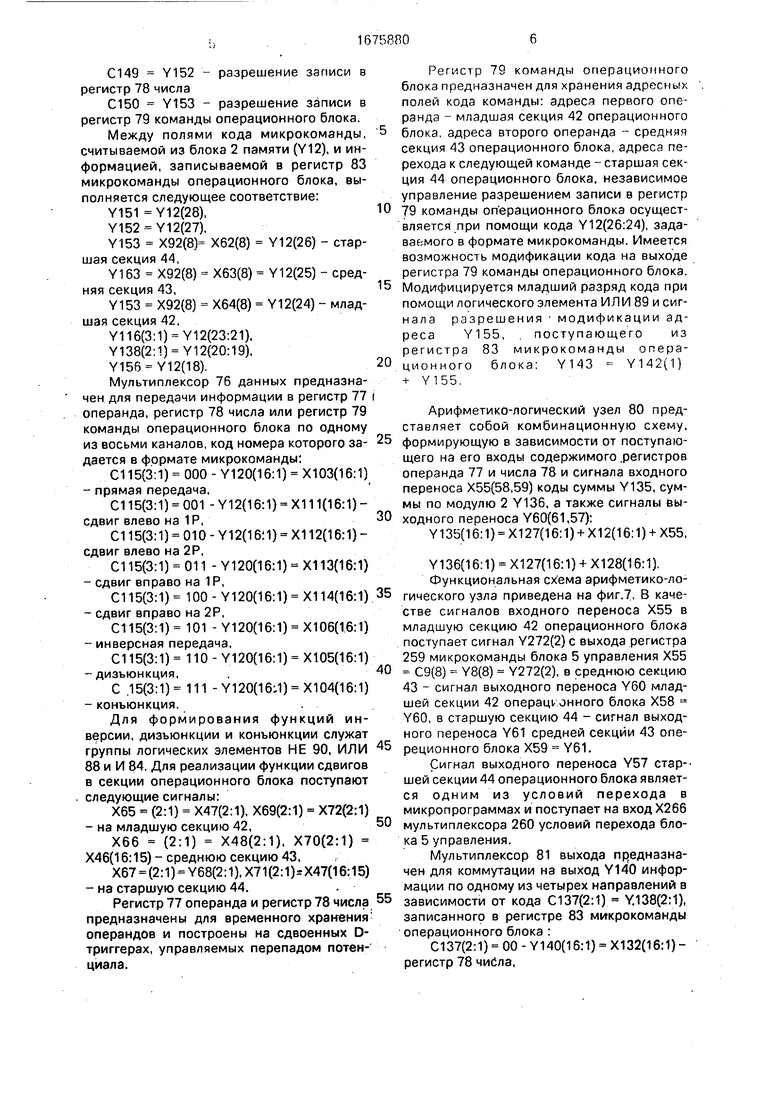

Узел 257 синхронизации (фиг.5) предназначен для формирования сигналов синх- ронизации работы всех узлов сопроцессора. Функциональная схема узла 257 синхронизации приведена на фиг.19. Узел 257 синхронизации выполнен по схеме конечного автомата, включающего генератор 393 тактовых импульсов, логическую матрицу 394 и регистр 395.

Генератор 393 тактовых импульсов может быть реализован по любой известной схеме, обеспечивающей формирование последовательности прямоугольных импульсов, например, по схеме, представленной на фиг.19.

Узел синхронизации циклически формирует на выходах 397 шесть тактовых им- пульсов в соответствии с временной диаграммой на фиг.20. Цикл содержит 12 микротактов Т1...Т12 (соответственно 12 состояний автомата) и разделен на 2 подцикла выборки и исполнения микрокоманд. Тактовые импульсы имеют следующее назначение:

Y397(1) - такт выборки микрокоманды,

Y397(2) - такт передачи адреса,

Y397(3) - такт обращения к памяти сопроцессора,

Y397(4) - такт записи кода микрокоманды в регистр микрокоманды,

Y397(5) - такт в регистры сопроцессора в цикле исполнения микрокоманды,

Y397(6)- имеет вспомогательное назначение для обеспечения переходов автомата: .... VT12 .Tl. его необходимость обусловлена тем, что коды выходов Y397(5) имеют повторы в цикле, например в Т2иТ6, Т8иТ12.

Сформированные на выходе 397 регистра 395 тактовые импульсы Y397(5:1) далее сгруппированы на пяти выходах в соответствии с потребностями синхронизации различных блоков:

Y271(2:1) Y397(5:4),

Y280(3:1) Y397(5:4)Y397(1),

Y288(2:1) Y394(4) Y397(1),

Y295(4:1) Y397(5)Y397{3:1),

Y277 Y397(4).

Логический преобразователь 394 узла синхронизации может быть реализован на ПЛМ К556Р12 в соответствии со следующей системой логических уравнений: 5XA(6:1) Y397(6:1),

термы ПЛМ:

А1 ХА&Ф А5- ХА44ХАЗ ХА2+-ХА1

10А2 ХА6 РХА5- -ХА4 ХАЗФХА24ХА1

A3 ХА6Ф А5Ф-ХА4 ХАЗФХА2- ХА1

А4 ХА6 ХА5 ХА4 ХАЗ« ХА2ФХА1 А5 ХА6 ХА5 ХА4Ф-ХАЗ ХА2-Ф-ХА1

А6 XA6 XA5 XA4tXA3 HKA2 H A1 А7 Ф-ХА4 фХАЗ ХА24чКА1

А8 ХА64ХА54-ХА4 4ХАЗ ХА34ХА2ФХА1 Х9 ХА6Ф-ХА5 ХА4 ХАЗФХА2ФХА

А10 ХА6ФХА5ФХА4-Ф-ХАЗФ-ХА2ФХА1

А11 ХА6ФХА5 ХА4ФХАЗФХА2ФХА1

А12 ХА6ФХА5ФХА4ФХАЗФХАФХА1

выходы ПЛМ: YA1 А124А1 + А2 + АЗ + А4 + А5

YA2 A12 + A6

YA3 А2 + A3 + А4 + А8 + А9 + А10

YA4 A3

YA5 А9 + А2 + А7 + А8

На информационный вход 398 регистра 395 поступает шестиразрядный сигнал с выхода 399 логического преобразователя (матрицы) 394. На вход 400 синхронизации записи регистра 395 поступает сигнал с выхода 401 генератора тактовых импульсов. На вход 402 сброса регистра 395 поступает сигнал с входа 290 узла 257 синхронизации, формируемый блоком 256 состо- яния: С402 С290 Y283.

В качестве выходов 397 используются инверсные выходы регистра 395. так как соответствующие сигналы имеют активный низкий уровень. Регистр 395 может быть реализован на двух микросхемах регистров К555ТМ8.

Узел 258 постоянной памяти (фиг.5} предназначен для формирования сигналов управления работой блоков сопроцессора и синхронизации работы с системной магистралью 39 и 40.

Узел 258 постоянной памяти представляет собой комбинационную схему, реализованную, например, на трех ПЛМ

А13 ХА5ФХА4 ХАЗ ХА2Ф-ХА10 ХА11Ф ХА6

А14 Ф А15 ХА5 Н А4ФХАЗФХА2 ФХА10Ф-ХА11-ф

ХА6

А16 ХА5Ф-ХАЗ- ХА2 -ХА1 ХАО ХА10

КР556Р12 (фиг.21) и описываемую следующей системой логических уравнений:

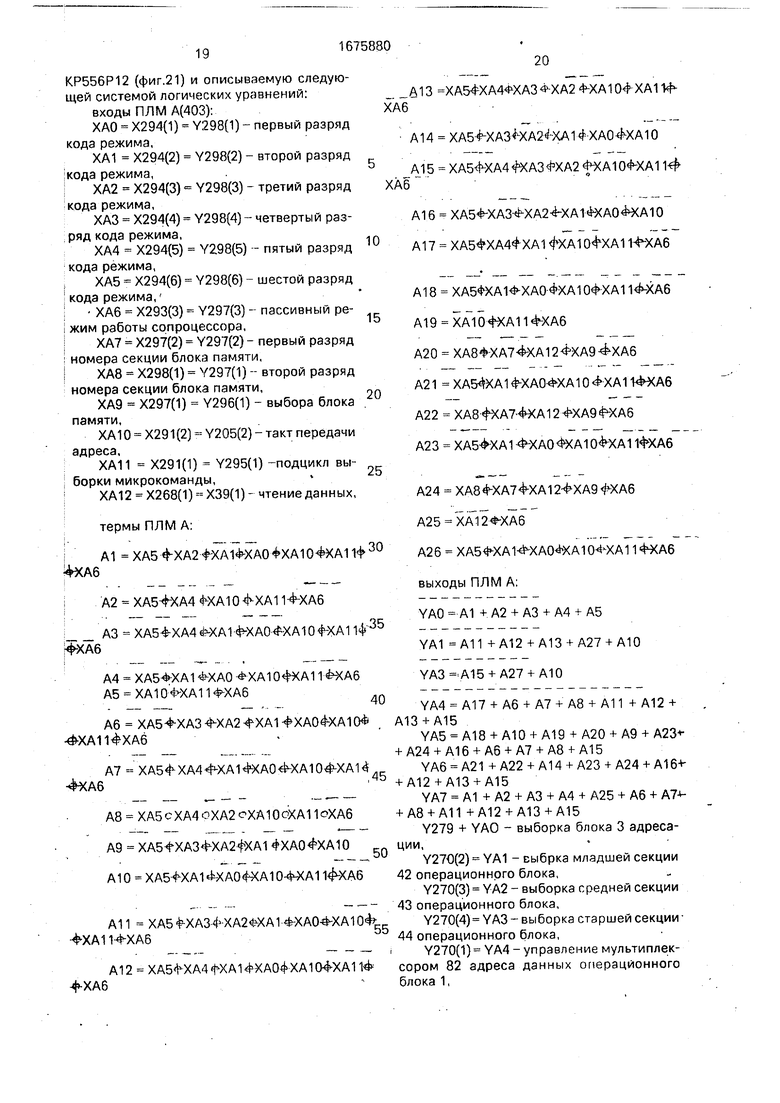

входы ПЛМ А(403):

ХАО Х294(1) Y298(1) - первый разряд кода режима,

ХА1 Х294(2) Y298(2) - второй разряд кода режима,

ХА2 Х294(3) Y298(3) - третий разряд кода режима,

ХАЗ Х294(4) Y298(4) - четвертый разряд кода режима,

ХА4 Х294(5) Y298(5) - пятый разряд 10 А17 ХА5ФХА4ФХА1ФХА10ФХА11- ХА6 кода режима,

ХА5 Х294(6) Y298(6) - шестой разряд кода режима,

ХА6 Х293(3) Y297(3) - пассивный режим работы сопроцессора,

ХА7 Х297(2) Y297(2) - первый разряд номера секции блока памяти,

ХА8 Х298(1) Y297(1) - второй разряд номера секции блока памяти,„

ХА9 Х297(1) Y296(1) - выбора блока 2(} памяти,

ХАЮ Х291(2) Y205(2) - такт передачи адреса,

ХА11 Х291(1) Y295(1) -подцикл выборки микрокоманды,

ХА12 Х268(1) Х39(1) - чтение данных,

15

25

А18 ХА5ФХА1-Ф-ХАОФХА10ФХА11 -ХАб

А19 ХА10 ХА11ФХА6

А20 ХА8Ф-ХА7-ФХА12-ФХА94ХА6

А21 X А54Х А1ФХ А10 X А11ФХ Аб

А22 ХА8ФХА7-ФХА12ФХА9 И А6

А23 ОЪ А11ФХА6

А24 ХА8Ф-ХА7Ф-ХА12-ЈХА9 Н А6 A25 XA V2VXA6

термы ПЛМ А:

А13 ХА5ФХА4 ХАЗ ХА2Ф-ХА10 ХА11Ф- ХА6

А14 Ф А15 ХА5 Н А4ФХАЗФХА2 ФХА10Ф-ХА11-ф

ХА6

А16 ХА5Ф-ХАЗ- ХА2 -ХА1 ХАО ХА10

А18 ХА5ФХА1-Ф-ХАОФХА10ФХА11 -ХАб

А19 ХА10 ХА11ФХА6

А20 ХА8Ф-ХА7-ФХА12-ФХА94ХА6

А21 X А54Х А1ФХ А10 X А11ФХ Аб

А22 ХА8ФХА7-ФХА12ФХА9 И А6

А23 ОЪ А11ФХА6

А24 ХА8Ф-ХА7Ф-ХА12-ЈХА9 Н А6 A25 XA V2VXA6

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Устройство адресации памяти | 1988 |

|

SU1520528A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Программируемый контроллер | 1988 |

|

SU1624404A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропроцессор | 1981 |

|

SU1012266A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных комплексах, например в терминальных системах управления гибких производственных систем либо в системах числового программного управления станками и роботами. Цель изобретения - повышение производительности за счет аппаратно-табличного выполнения операций и динамического микропрограммирования. Программируемый сопроцессор содержит операционный блок, блок памяти, блок адресации, интерфейсный блок, блок управления, блок коммутации, регистр адреса. 22 ил , 4 табл.

4ХА6

А1 ХА5Ф-ХА2Ф-ХА1 ХАОФХА10-ФХА11Ф3°А26 ХА5Ф-ХА1- -ХАО ХА10 ХА11ФХА6

4ХА6

А2 ХА54ХА4 ФХА10 Ф-ХА11-Ф-ХА6

A3 А4 Ф-ХА1 ф-ХАО ХА 10 фХА 11ф 35

А4 XA5- -XA14-ХАО ХА10ФХА11 ХА6 А5 ХА10ФХА11ФХА6

А6 ХА54-ХА34-ХА2-ФХА1-ФХА04ХА10 А13 + А15 ХАПФХАб YA5 A18 + A10 + A19 + А20 + А9 + А23+

- -- -+А24 + А16 + А6 + А7 + А8 + А15

А7 ХА5ФХА4 ФХА14ХАО & А104-ХА14YA6 А21 + А22 + А14 + А23 + А24 + А16+

-ФХА6 45 +А12 + А13 + А15

- -YA7 А1 + А2 + A3 + А4 + А25 + А6 + А7+А8 ХА5СХА4 ОХА2 оХА10оХА1 ЮХА6+ А8 + А11 + А12 + А13 + А15

- - -.-.у279 + YAO - выборка блока 3 адресаА9 XA5-tXA3 H A2tXA1 4ХАОФХА10 Q ции,

- - Y270(2) YA1 - выбрка младшей секции

А10 ХА5 ХА1« ХАОФХА10-ФХА114НКА6 42 операционного блока,

Y270(3) YA2- выборка средней секции

- -----43 операционного блока,

А11 « ХА5Ф-ХАЗФ-ХА2ФХА1Ф-ХАО-Ф-ХА104Э1Y270(4) YA3-выборка старшей секцииФХА11 ХА644 операционного блока,

Y270(1) YA4-управление мультиплекА12 ХА5ФХА4 ХА141ХА04ХА104-ХА114 : сором 82 адреса данных операционного 4-ХА6 блока 1,

выходы ПЛМ А:

YAO А1 + А2 + A3 + А4 + А5

YA1 А11 +А12 +А13 +А27 +А10

YA3 A15 + A27 +A10

YA4 А17 + А6 + А7 + А8 + А11 + А12 +

Y274(1) YA5 - первый разряд кода уп-YB5 В5

равления блоком 6 коммутации,YB6 В4 + В5 + Вб + В7

Y274(2) YA6 - второй разряд кода уп-

равления блоком 6 коммутации,, YB7 В6

Y274(3) YA7 - третий разряд кода уп-5 Y273(1) YBO - управление выборки

равления блоком 6 коммутации,блока 2 памяти,

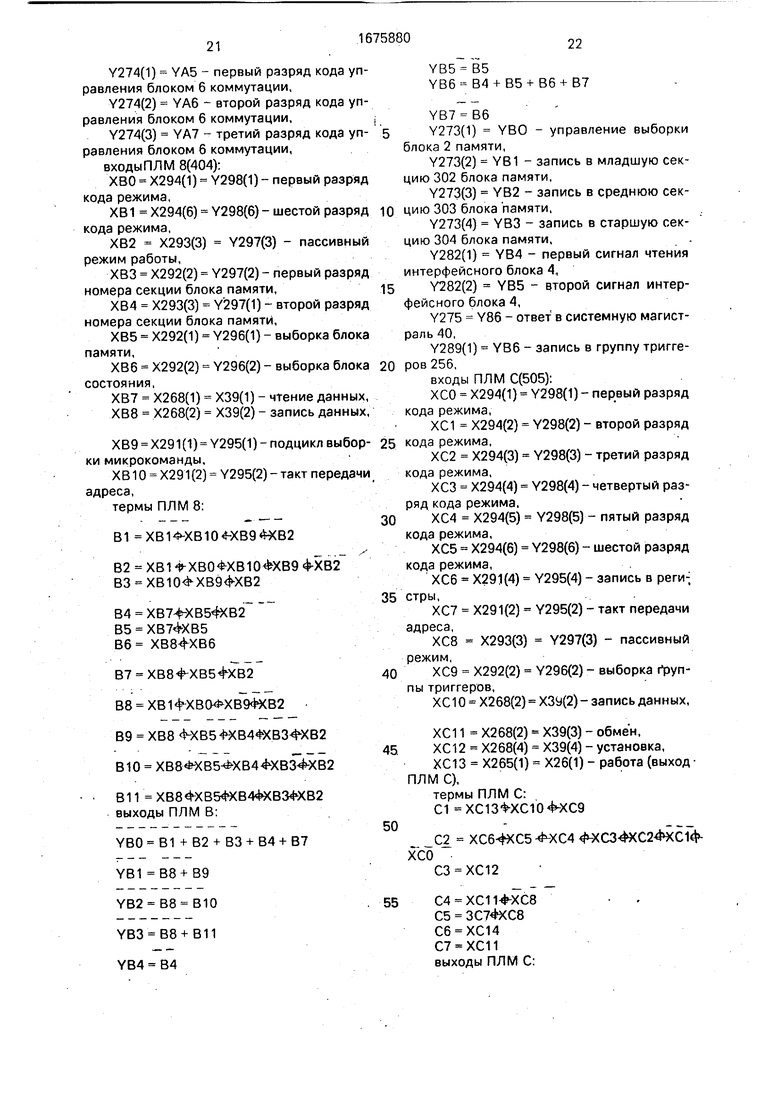

входыПЛМ 8(404):Y273(2) YB1 - запись в младшую секХВО Х294(1) Y298(1) - первый разрядцию 302 блока памяти,

кода режима,Y273(3) YB2 - запись в среднюю секХВ1 Х294(б) Y298(6)-шестой разрядю цию 303 блока памяти,

кода режима,Y273(4) YB3 - запись в старшую секХВ2 Х293(3) Y297(3) - пассивныйцию 304 блока памяти,

режим работы,Y282(1) YB4 - первый сигнал чтения

ХВЗ Х292(2) Y297(2) - первый разрядинтерфейсного блока 4,

номера секции блока памяти,15 Y282(2) YB5 - второй сигнал интерХВ4 Х293(3) Y297(1) - второй разрядфейсного блока 4,

номера секции блока памяти,Y275 Y86 - ответ в системную магистХВ5 Х292(1) Y296(1) - выборка блокараль 40,

памяти,Y289(1) YB6 - запись в группу триггеХВ6 Х292(2) Y296(2) - выборка блока20 ров 256,

состояния,входы ПЛМ С(505):

ХВ7 Х268(1) Х39(1) - чтение данных,ХСО Х294(1) Y298(1) - первый разряд

ХВ8 Х268(2) Х39(2)-запись данных,кода режима,

ХС1 Х294(2) Y298(2) - второй разряд

ХВ9 Х291(1) У295(1)-подцикл выбор-25 кода режима,

ки микрокоманды,ХС2 Х294(3) Y298(3) - третий разряд

ХВ10 Х291(2) У295(2)-тактпередачикода режима,

XCS Х294(4) Y298(4) - четвертый разряд кода режима,

дреса,

термы ПЛМ 8:

81 ХВ1 -ХВ10 ХВ94КВ2

82 ХВ1 Ч -ХВ04-ХВ10ЈХВ9 Ф-ХВ2

83 ХВ104-ХВ9ФХВ2

84 ХВ74-ХВ54ХВ2

85 ХВ7-ФХВ5 В6 ХВ84ХВ6

87 ХВ8 И В54ХВ2

88 ХВ1ФХВ04 ХВ9ФХВ2

89 ХВ8 Ф-ХВ5ФХВ4ФХВЗ ХВ2

810

811 ХВ84ХВ54ХВ44 ХВЗФХВ2 выходы ПЛМ fiYBO B1 +B2 + B3 + B4 + B7 YB1 В8 + В9 YB2 B8 B10 YB3 B8 + B11 YB4 В4

кода режима,

XCS Х294(4) Y298(4) - четвертый разряд кода режима,

ХС4 Х294(5) Y298(5) - пятый разряд кода режима,

ХС5 Х294(6) Y298(6) - шестой разряд кода режима,

ХС6 Х291(4) Y295(4) - запись в реги- стры,

ХС7 Х291(2) Y295(2) - такт передачи адреса,

ХС8 Х293(3) Y297(3) - пассивный режим.

ХС9 Х292(2) Y296(2) - выборка фуп- пы триггеров,

ХС10 Х268(2) ХЗУ(2) - запись данных.

ХС11 Х268(2) Х39(3) - обмен, ХС12 Х268(4) Х39(4) - установка, ХС13 Х265(1) Х26(1) - работа (выход ПЛМ С),

термы ПЛМ С:

С1 ХС Ф-ХС9

ХСО

С1 ХС64ХС5 ХС4 ф-ХС34ХС24 ХС1ф- ) СЗ ХС12

С4 ХС11-Ф-ХС8 С5 ЗС74ХС8 С6 ХС14 С7 ХС11 выходы ПЛМ С:

YCO C1 YC2 C3

YC3 C7

YC4 C5

YC5 C4 + C5

Y289(2) YCO - перевод в активный режим работы,

Y289(3) YC1 - перевод в пассивный режим работы,

Y289(4) YC2 - установка,

Y285(1) YC3 - сброс регистра выбора

Y285(2) YC4 - запись в регистр выбора,

Y276 YC5 - запись в регистр адреса.

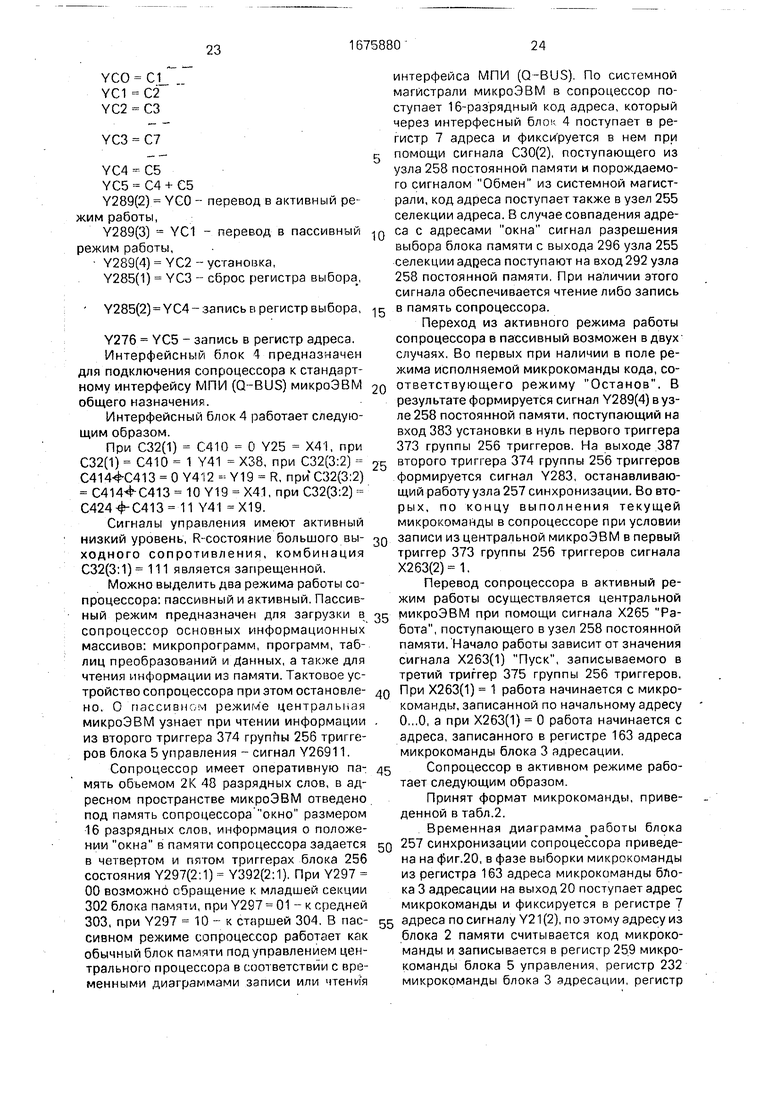

Интерфейсный блок 4 предназначен для подключения сопроцессора к стандартному интерфейсу МПИ (Q-BUS) микроЭВМ общего назначения.

Интерфейсный блок 4 работает следующим образом.

При С32(1) С410 О Y25 Х41, при С32(1) С410 1 Y41 Х38, при С32(3:2) С414-Ф-С413 О Y412 Y19 R, при С32(3:2) С4144-С413 10 Y19 Х41, при С32(3:2) С424Ф-С413 11 Y41 Х19.

Сигналы управления имеют активный низкий уровень, R-состояние большого выходного сопротивления, комбинация С32(3:1} 111 является запрещенной.

Можно выделить два режима работы сопроцессора: пассивный и активный. Пассивный режим предназначен для загрузки в сопроцессор основных информационных массивов: микропрограмм, программ, таблиц преобразований и Данных, а также для чтения информации из памяти. Тактовое устройство сопроцессора при этом остановлено. О пассивном режим е центральная микроЭВМ узнает при чтении информации из второго триггера 374 группы 256 триггеров блока 5 управления - сигнал Y26911.

Сопроцессор имеет оперативную память объемом 2К 48 разрядных слов, в адресном пространстве микроЭВМ отведено под память сопроцессора окно размером 16 разрядных слов, информация о положении окна в памяти сопроцессора задается в четвертом и пятом триггерах блока 256 состояния Y297(2:1) Y392(2:1). При Y297 00 возможнб обращение к младшей секции 302 блока памяти, при Y297 01 - к средней 303, при Y297 10 - к старшей 304. В пассивном режиме сопроцессор работает как обычный блок памяти под управлением центрального процессора в соответствии с временными диаграммами записи или чтения

интерфейса МПИ (Q-BUS). По системной магистрали микроЭВМ в сопроцессор поступает 16-разрядный код адреса, который через интерфесный блок 4 поступает в регистр 7 адреса и фиксируется в нем при

помощи сигнала С30(2), поступающего из узла 258 постоянной памяти м порождаемого сигналом Обмен из системной магистрали, код адреса поступает также в узел 255 селекции адреса. В случае совпадения адре0 са с адресами окна сигнал разрешения выбора блока памяти с выхода 296 узла 255 селекции адреса поступают на вход 292 узла 258 постоянной памяти. При наличии этого сигнала обеспечивается чтение либо запись

5 в память сопроцессора.

Переход из активного режима работы сопроцессора в пассивный возможен в двух случаях. Во первых при наличии в поле режима исполняемой микрокоманды кода, со0 ответствующего режиму Останов. В результате формируется сигнал Y289(4) в узле 258 постоянной памяти, поступающий на вход 383 установки в нуль первого триггера 373 группы 256 триггеров. На выходе 387

5 второго триггера 374 группы 256 триггеров формируется сигнал Y283, останавливающий работу узла 257 синхронизации. Во вторых, по концу выполнения текущей микрокоманды в сопроцессоре при условии

0 записи из центральной микроЭВМ в первый триггер 373 группы 256 триггеров сигнала Х263(2)1.

Перевод сопроцессора в активный режим работы осуществляется центральной

5 микроЭВМ при помощи сигнала Х265 Работа, поступающего в узел 258 постоянной памяти. Начало работы зависит от значения сигнала Х263(1) Пуск, записываемого в третий триггер 375 группы 256 триггеров.

0 При Х263(1) 1 работа начинается с микрокоманды, записанной по начальному адресу 0...0, а при Х263(1) 0 работа начинается с адреса, записанного в регистре 163 адреса микрокоманды блока 3 адресации.

5 Сопроцессор в активном режиме работает следующим образом.

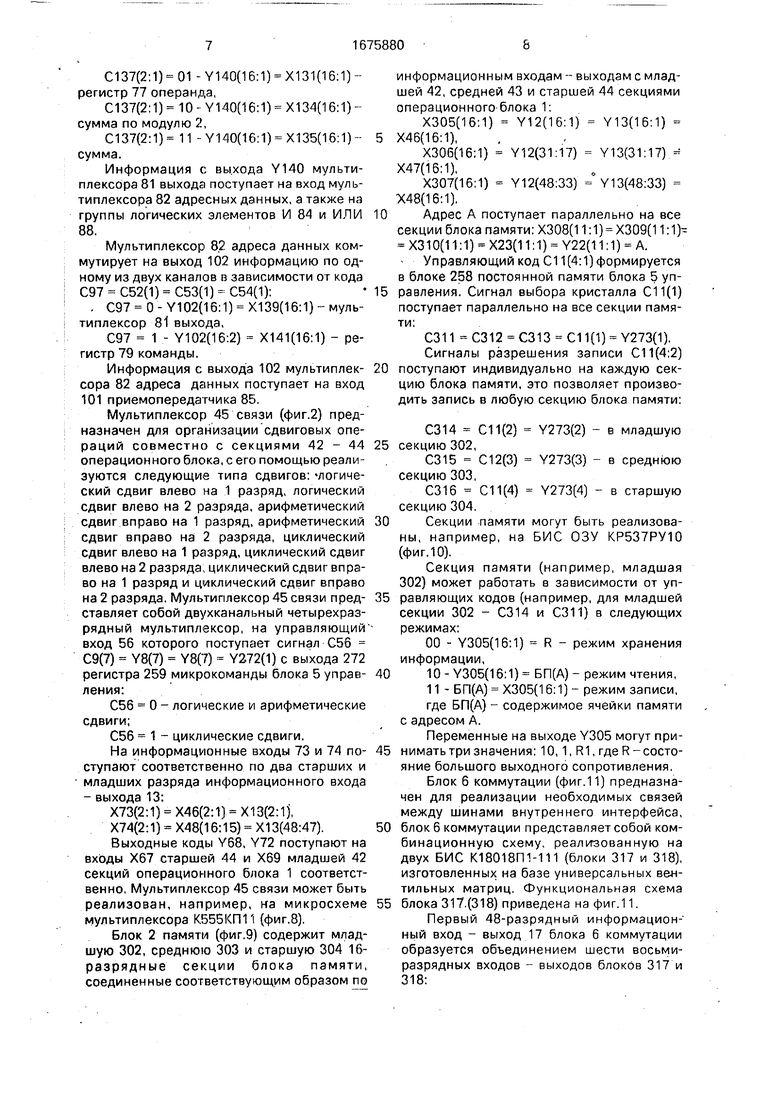

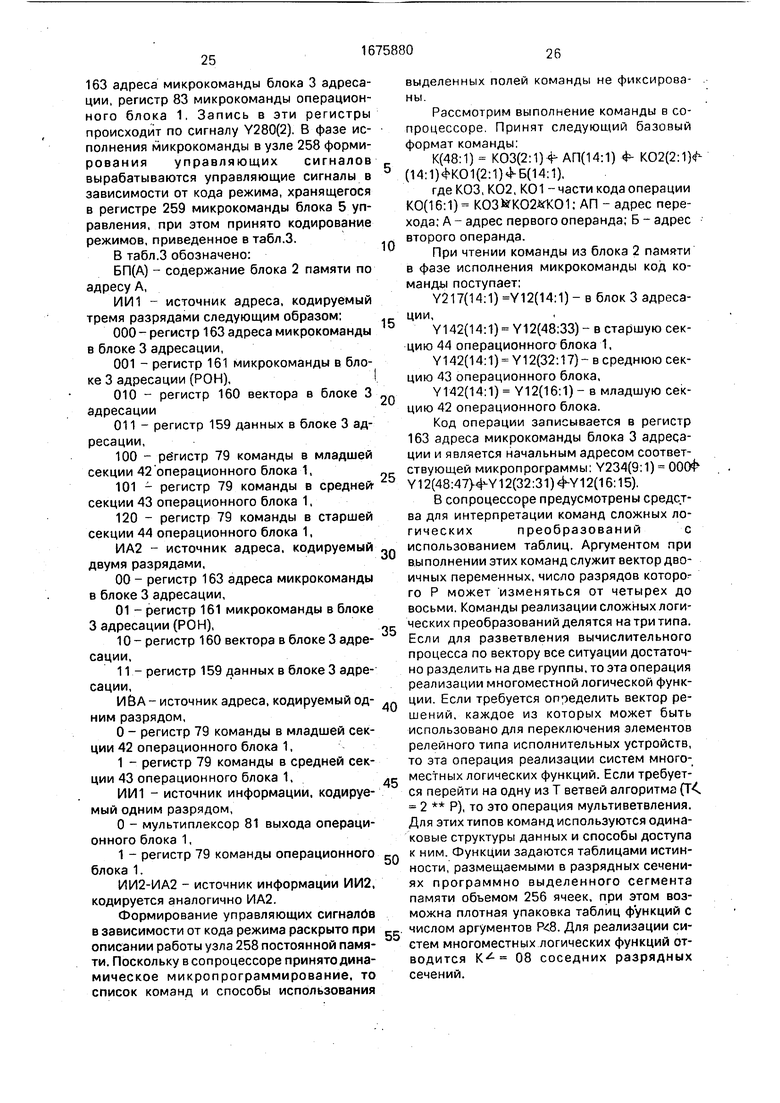

Принят формат микрокоманды, приведенной в табл.2.

Временная диаграмма работы блока

0 257 синхронизации сопроцессора приведена на фиг.20, в фазе выборки микрокоманды из регистра 163 адреса микрокоманды блока 3 адресации на выход 20 поступает адрес микрокоманды и фиксируется в регистре 1

5 адреса по сигналу Y21 (2), по этому адресу из блока 2 памяти считывается код микрокоманды и записывается в регистр 259 микрокоманды блока 5 управления, регистр 232 микрокоманды блока 3 адресации, регистр

163 адреса микрокоманды блока 3 адресации, регистр 83 микрокоманды операционного блока 1. Запись в эти регистры происходит по сигналу Y280(2). В фазе исполнения микрокоманды в узле 258 форми- рования управляющих сигналов вырабатываются управляющие сигналы в зависимости от кода режима, хранящегося в регистре 259 микрокоманды блока 5 управления, при этом принято кодирование режимов, приведенное в табл.3.

В табл.3 обозначено:

БП(А) - содержание блока 2 памяти по адресу А,

ИИ1 - источник адреса, кодируемый тремя разрядами следующим образом:

000- регистр 163 адреса микрокоманды в блоке 3 адресации,

001 - регистр 161 микрокоманды в блоке 3 адресации (РОН),

010- регистр 160 вектора в блоке 3 адресации

011- регистр 159 данных в блоке 3 адресации,

100- ре гистр 79 команды в младшей секции 42 операционного блока 1,

101- регистр 79 команды в средней- секции 43 операционного блока 1,

120 - регистр 79 команды в старшей секции 44 операционного блока 1,

ИА2 - источник адреса, кодируемый двумя разрядами,

00- регистр 163 адреса микрокоманды в блоке 3 адресации,

01- регистр 161 микрокоманды в блоке

3 адресации (РОН),

10- регистр 160 вектора в блоке 3 адресации,

11- регистр 159 данных в блоке 3 адресации,

ИВА- источник адреса, кодируемый од- ним разрядом,

0- регистр 79 команды в младшей секции 42 операционного блока 1,

1- регистр 79 команды в средней секции 43 операционного блока 1,

ИИ1 - источник информации, кодируемый одним разрядом,

0- мультиплексор 81 выхода операционного блока 1,

1- регистр 79 команды операционного блока 1.

ИИ2-ИА2 - источник информации ИИ2, кодируется аналогично ИА2.

Формирование управляющих сигналов в зависимости от кода режима раскрыто при описании работы узла 258 постоянной памяти. Поскольку в сопроцессоре принято динамическое микропрограммирование, то список команд и способы использования

....

20

1П

.

40

45

-.

с

25

30

выделенных полей команды не фиксированы.

Рассмотрим выполнение команды в сопроцессоре. Принят следующий базовый формат команды:

К(48:1) «03(2:1) АП(14:1) Ф- К02(2:1)ф- (14:1)ФК01(2:1)4-Б(14:1),

где КОЗ, К02, К01 -части кода операции К0(16:1) K03fcK02JsK01; АП -адрес перехода; А - адрес первого операнда; Б - адрес второго операнда.

При чтении команды из блока 2 памяти в фазе исполнения микрокоманды код команда поступает:

Y217(14:1) Y12(14:1) - в блок 3 адресации,

Y142(14:1) Ґ12(48:33)-в старшую секцию 44 операционного блока 1,

Y142(14:1) Y12(32:17)-в среднюю секцию 43 операционного блока,

Y142(14:1) Y12(16:1) - в младшую секцию 42 операционного блока.

Код операции записывается в регистр 163 адреса микрокоманды блока 3 адресации и является начальным адресом соответствующей микропрограммы: Y234(9:1) 000Ј Y12(48:47H°/12(32:31)«r-Y12(16:15).

В сопроцессоре предусмотрены средства для интерпретации команд сложных логическихпреобразованийсиспользованием таблиц. Аргументом при выполнении этих команд служит вектор двоичных переменных, число разрядов которого Р может изменяться от четырех до восьми. Команды реализации сложных логических преобразований делятся на три типа. Если для разветвления вычислительного процесса по вектору все ситуации достаточно разделить на две группы, то эта операция реализации многоместной логической функции. Если требуется определить вектор решений, каждое из которых может быть использовано для переключения элементов релейного типа исполнительных устройств, то эта операция реализации систем многоместных логических функций. Если требуется перейти на одну из Т ветвей алгоритма fK. 2 Р), то это операция мультиветвления. Для этих типов команд используются одинаковые структуры данных и способы доступа к ним. Функции задаются таблицами истинности, размещаемыми в разрядных сечениях программно выделенного сегмента памяти объемом 256 ячеек, при этом возможна плотная упаковка таблиц ф ункций с числом аргументов . Для реализации систем многоместных логических функций отводится 08 соседних разрядных сечений.

Выполнение операции вычисления многоместной логической функции осуществляется следующей последовательностью преобразований:

FA F4T FB

X(P:1)--A(12:1)--Y12(48:1)--Y 0,1,

(Р:1) - множество векторов,

А(12:1) - множество адресов,

Y12(48:1) - множество слов, считанных из памяти,

Y - вычисляемая, многоместная логическая функция,

FA, F4T, FB - операции формирования t адреса, чтения из памяти и выделения разрядов соответственно.

Рассмотрим организацию доступа к элементам таблиц. Адрес элементов таблицы определяется информацией, содержащейся в векторе аргумента, записанном в регистре 160 вектора блока 3 адресации, а также управляющей информацией, закодированной в команде, хранящейся в регистре 161 команды блока 3 адресации. В регистре 161 команды блока 3 адресации содержится информация, обеспечивающая выбор требуемых разрядов с помощью блока 6 коммутации и мультиплексоров 166 - 169 выделения разрядов. Кодирование управляющей информации в формате команды производится в соответствии с табл.4 (коды X определяют положение в разрядном сечении сегмента).

Формула изобретения

Программируемый сопроцессор, содержащий операционный блок, блок памяти, блок адресации, регистр адреса, интерфей- сный блок и блок управления, причем первая группа выходов блока управления соединена с группой входов кода команды операционного блока, вторая группа выходов блока управления соединена с группой входов управления чтением - записью блока памяти, выход переноса операционного бл ока подключен к первому входу логических условий блока управления, первый вход - выход группы информационных входов - выходов блока памяти соединен с первым входом группы входов кода микрокоманды и логических условий блока управления и с первым входом - выходом группы информа- ционных входов - выходов операционного блока, выход регистра адреса подключен к адресному входу блока памяти, первый вход группы информационных входов блока адресации подключен к второму входу- выходу группы информационных входов - выходов блока памяти и к второму входу - выходу группы информационных входов - выходов операционного блока, выход ий0

5

0

5

0

5

0

5

0

5

терфейсного блока подключен к информационному входу блока управления, первый выход блока адресации подключен к второму входу логических условий блока управления, вход управления режимом регистра адреса подключен к третьему выходу блока управления, вход управления режимом блока адресации подключен к четвертому выходу блока управления, вход управления режимом интерфейсного блока подключен к пятому выходу блока управления, шестой выход блока управления подключен к информационному входу интерфейсного блока, отличающийся тем,что, с целью повышения производительности за счетап- паратно-табличного выполнения комплексных логических операций, устройство дополнительно содержит блок коммутации, причем группа информационных входов - выходов блока памяти соединена с первой группой информационных входов- выходов блока коммутации, первый вход- выход второй группы информационных входов-выходов блока коммутации подключен к первому входу - выходу первой группы информационных входов - выходов интерфейсного блока, информационному входу - выходу блока адресации и информационному входу регистра адреса, вход управления режимом блока коммутации подключен к седьмому выходу блока управления, вход режима и седьмой выход блока управления, а также второй информационый вход - выход инте- фейсного блока являются входом режима, выходом ответа и информационным входом

-выходом сопроцессора соответственно, причем операционный блок содержит младшую, среднюю и старшую секции мультиплексор связи, причем входы кода микрокоманды младшей, средней и старшей секций операционного блока подключены к группе информационных входов - выходов операционного блока, информационный вход - выход младшей секции операционного блока подключен к первому входу

-выходу группы информационных входов - выходов операционного блока, информационный вход - выход средней секции операционного блока подключен к второму входу

-выходу группы информационных входов - выходов операционного блока, информационные входы - выходы старшей секции операционного блока подключены к третьему входу - выходу группы информационных входов - выходов операционного блока, входы управления приемом - передачей и тактовые входы младшей, средней и стар шей секции операционного блока соединены со средними разрядами входа кода команды операционного блока, управляющий вход мультиплексора связи подключен к младшему разряду входа кода команды операционного блока, вход переноса младшей секции операционного блока подключен к старшему разряду входа кода команды операционного блока, выход переноса старшей секции операционного блока подключен к выходу переноса операционного блока, вход переноса средней секции операционного блока подключен к выходу пере- носа младшей секции операционного блока, вход переноса старшей секции операционного блока подключен к выходу переноса средней секции операционного блока, входы вдвигаемых слева разрядов младшей секции операционного блока подключены к младшим разрядам информационного входа - выхода средней секции операционного блока, входы вдвигаемых слева разрядов средней секции операционного блока под- ключены к младшим разрядам информационного входа - выхода старшей секции операционного блока, входы вдвигаемых слева разрядов старшей секции операционного блока подключены к первым выходам мультиплексора связи, входы вдвигаемых справа разрядов младшей секции операционного блока подключены к вторым выходам мультиплексора связи, входы вдвигаемых справа разрядов средней сек- ции операционного блока подключены к старшим разрядам информационного входа - выхода младшей секции операционного блока, входы вдвигаемых справа разрядов старшей секции операционного блока под- ключены к старшим разрядам информационного входа - выхода средней секции операционного блока, первые информационные входы мультиплексора связи подклю- чены к младшим двум разрядам информационного входа - выхода младшей секции операционного блока, вторые информационные входы мультиплексора связи подключены к старшим двум разрядам информационного входа - выхода старшей секции операционного блока, кроме того, каждая секция операционного блока содержит мультиплексор данных, регистр операнда, регистр числа, регистр команд, приемопередатчик, арифметико-логический узел, выходной мультиплексор, мультиплексор адреса данных, регистр микрокоманды, группу элементов И, с первого по третий элементы И, группу элементов ИЛИ, элемент ИЛИ и группу элементов НЕ, причем информационный вход - выход приемопередатчика является информационным входом - выходом секции операционного блока, информационный вход регистра микрокоманды подключен к информационному

входу секции, вход и выход переноса ариф метико-логического узла являются соответственно входом и выходом переноса секции, управляющий вход приемопередатчика является входом управления приемом -- передачей секции, управляющий вход мультиплексора адреса данных и вход записи регистра микрокоманды подключены к первому и второму разрядам входа кода команды секции соответственно, первые входы с первого по третий элементов И соединен с третьим разрядом входа кода команды секции, информационные входы приемопередатчика подключены к выходам мультиплексора адреса данных, первая группа информационных входов мультиплексора данных подключена к группе информационныхвыходовприемопередатчика, вторая группа информационных входов мультиплексора данных подключена к выходам элементов И группы, третья группа информационных входов мультиплексора данных подключена к выходам элементов ИЛИ группы, четвертая группа информационных входов мультиплексора данных подключена к выходам элементов НЕ группы, с т-го (т-рэзряд- ность информационного входа - выхода секции) по первый входы пятой группы информационных входов мультиплексора данных соединены с т-го по первый информационными выходами приемопередатчика и первым входом группы входов вдвигаемых справа разрядов секции соответственно, с т-го по первый входы шестой группы информационных входов мультиплексора данных подключены к с (т-2)-го по первый информационным входам приемопередатчика и к первому и второму входам группы входов вдвигаемых справа разрядов секции соответственно, с m-rn по первые входы седьмой группы информационных входов мультиплексора данных подключены к с гл- го по второй информационным выходам приемопередатчика и к первому входу труп-, пы входов вдвигаемых слева разрядов секции соответственно, с т-го по первый входы восьмой группы информационных входов мультиплексора данных подключены к с т- го по третий информационным выходам приемопередатчика и к первому и второму входам группы входов вдвигаемых слева разрядов секции операционного блока соответственно, управляющий вход мультиплексора данных соединен с первым выходом регистра микрокоманды, информационные входы регистра операнда, регистра числа и регистра команды подключены к выходу мультиплексора данных, входы записи регистра операнд;) регистра числа и

регистра команды соединены соответственно с выходами первого, второго и третьего элементов И, первый и второй входы операндов .арифметико-логического узла подключены соответственно к выходу регистра операнда и к выходу регистра числа, первый, второй, третий и четвертый информационные входы выходного мультиплексора подключены соответственно к выходу регистра операнда, к выходу регистра числа, к первому и второму информационным выходам арифметико-логического узла, управляющий вход выходного мультиплексора соединен с вторым выходом регистра мик- рокоманды, первый информационный вход Мультиплексора адреса данных подключен к выходу выходного мультиплексора, второй информационный вход мультиплексора адреса данных подключен к выходу регистра команды и выходу элемента ИЛИ, первые входы элементов И группы, элементов ИЛИ группы, входы элементов НЕ группы подключены поразрядно к информационным выходам проемопередатчика, вторые входы элементов И группы и элементов ИЛИ группы подключены к выходам выходного мультиплексора, вторые входы первого, второго и третьего элементов И подключены соответственно к третьему, четвертому и пятому выходам регистра микрокоманды, первый и второй входы элемента ИЛИ подключены соответственно к младшему разряду выхода регистра команды и к шестому выходу регистра микрокоманды, причем блок адресации содержит мультиплексор адреса, мультиплексоры выделения восьми, четырех, двух и одного разрядов, приемопередатчик, регистр данных, регистр вектора, регистр команды, регистр микрокоманды, регистр адреса микрокоманды, триггер модификации адреса, мультиплексор адреса микрокоманды , первый и второй элементы ИЛИ, группу элементов ИЛИ, с первого по четвертый элементы И, первую и вторую группы элементов И, информационный вход - выход приемопередатчика является информационным входом - выходом блока адресации,управляющийвход приемопередатчика подключен к первому разряду входа управления режимом блока адресации, управляющий вход мультиплексора адреса микрокоманды соединен с первыми входами элементов И первой группы и вторым разрядом входа управления режимом блока адресации, первый вход первого элемента ИЛИ подключен к входу записи регистра микрокоманды и третьему разряду управления режимом блока адресаци, первые входы с первого по четвертый элементов И соединен с входом записи триггера

модификации и четвертым разрядом йхода управления режимом блока адресации, информационный вход триггера модификации адреса подключен к пятому разряду входа управления режимом блока адресации, информационный вход приемопередатчика подключен к выходу мультиплексора адреса, информационные входы регистра данных, регистра команды и регистра микрокоманды подключен к информационQ ному выходу приемопередатчика, вход записи регистра данных соединен с выходом первого элемента И, старшие разряды информационного входа регистра век-тора подключены к выходам элементов И второй

5 группы, а младшие разряды информационного входа регистра вектора подключены к выходам мультиплексора выделения четырех разрядов, вход записи регистра вектора соединен с выходом второго элемента И,

Q вход записи регистра команды соединен с выходом третьего элемента И, информационный вход регистра адреса микрокоманды подключен к выходу мультиплексора адреса микрокоманды, вход записи регистра адре5 са микрокоманды соединен с выходом первого элемента ИЛИ, первый и второй информационные- входы мультиплексора адреса микрокоманды подключен к первой и второй группам информационных входов

0 блока адресации, управляющий вход мультиплексора выделения одного разряда подключен к первому разряду выхода регистра команды, первые входы элементов И второй группы подключены к управляющему входу

5 мультиплексора выделения двух разрядов и к второму разряду выхода регистра команды, управляющий вход мультиплексора выделения четырех разрядов подключен к третьему разряду выхода регистра команQ ды, управляющий вход мультиплексора выделения восьми разрядов подключен к четвертому разряду выхода регистра команды, первый информационный вход мультиплексора выделения восьми разрядов

5 подключен к старшим т/2 разрядам выхода регистра данных, второй информационный вход мультиплексора выделения восьми разрядов подключен к младшим т/2 разрядам выхода регистра данных, первый

0 информационный вход мультиплексора выделения четырех разрядов подключен к старшим т/4 разрядам выхода мультиплексора выделения восьми разрядов, второй информационный вход мультиплексора вы5 деления четырех разрядов подключен к младшим т/2 разрядам выхода мульти- плексора выделения восьми разрядов, первый информационный вход мультиплексора выделения двух разрядов подключен к старшим m/8 разрядам выхода мультиплексора выделения четырех разрядов, второй информационный вход мультиплексора выделения двух разрядов подключен к младшим т/8 разрядам выхода мультиплексора выделения четырех разрядов, первый информационный вход мультиплексора выделения одного разряда подключен к старшему разряду выхода мультиплексора выделения двух разрядов, второй информационный вход мультиплексора выделения одного разряда подключен к младшему разряду выхода мультиплексора выделения двух разрядов, выход мультиплексора выделения одного разряда является первым выходом блока адресации, первая группа информационных входов мультиплексора адреса подключена к группе выходов регистра данных, вторая группа информационных входов мультиплексора адреса подключена к младшим пяти разрядам выхода регистра микрокоманды, третья группа информационных входов мультиплексора адреса подключена к старшим разрядам выхода регистра адреса микрокоманды и к выходу второго элемента ИЛИ, четвертая группа информационных входов мульти- плексора адреса подключена к старшим разрядам выхода регистра команды, к выходам элементов ИЛИ группы и к выходу регистра вектора, управляющие входы мультиплексора адреса соединены с выходами элементов И второй группы, второй вход первого элемента ИЛИ подключен к выходу четвертого эемента И, первый и второй входы второго элемента ИЛИ подключены соответственно к младшему разряду выхода регистра адреса микрокоманды и к выходу триггера модификации адреса, первые входы элементов ИЛИ группы подключены к средним разрядам выхода регистра команды, вторые входы элементов ИЛИ группы подключены к старшим разрядам выхода регистра вектора, вторые входы с первого по четвертый элементов И подключены к разрядам с шестого по девятый выхода регистра микрокоманды, вторые входы элементов И первой группы подключены к десятому и одиннадцатому разрядам выхода регистра микрокоманды, входы элементов И второй группы подключены к первой группе выходов мультиплексора выделения восьми бит, причем блок управления содержит узел синхронизации, регистр микрокоманды, мультиплексор условий и узел постоянной памяти, узел селекции адреса и пять триггеров, причем информационные входы регистра микрокоманды соединены с входом кода микрокоманды и логических условий блока управления, первая группа информационных входов мультиплексора условий соединена со старшим и младшим разрядами входа кода микрокоманды и логических условий блока управления, инфор- мационные входы первого, второго, t- третьего и четвертого триггеров соединены с соответствующими входами группы информационных входов блока управления, информационный вход пятого триггера соединен с выходом первого тиггера, информаП ционный вход узла селекции адреса соединен с соответствующими входами группы информационных входов блока управления, первый адресный вход узла постоянной памяти соединен с младшим

,- входом группы информационных входов блока управления, вторая и третья группы информационных входов мультиплексора условий являются соответственно первой и второй группами входов логических условий

Q блока управления, второй адресный вход узла постоянной памяти является входом режима блока управления, выход пятого триггера соединен с шестым выходом блока управления, разряды первого выхода узла

5 постоянной памяти соединены с первого по четвертый разрядами первого выхода блока управления, первый и второй входы первой группы выходов узла синхронизации подключены к пятому и шестому выходам перъ вой группы выходов блока управления соответственно, первый и второй выходы первой группы выходов регистра микрокоманды подключены к седьмому и восьмому выходам первой группы выходов блока упс- равления соответственно, второй выход узла постоянной памяти подключен к второму выходу блока управления, третий выход узла постоянной памяти подключен к седьмому выходу блока управления, четвертый

0 выход узла постоянной памяти подключен к первому выходу третьей группы выходов блока управления, пятый выход узла постоянной памяти подключен к первому выходу четвертой группы выходов блока управле-.

с ния, шестой выход узла постоянной памяти подключен к пятому выходу блока управления, седьмой выход узла постоянной памяти подключен к восьмому выходу блока управления, выход второго триггера подключен к

Q второму выходу третьей группы выходов блока управления, выходы с первого по третий второй группы выходов узла синхронизации подключены к второму, третьему, четвертому выходам четвертой группы выс ходов блока управления соответственно, выход мультиплексора условий подключен к пятому выходу четвертой группы выходов блока управления, управляющий вход узла селекции адреса подключен к восьмому выходу узла постоянной памяти, вход синхронизации пятого триггера и вход установки в 1 второго триггера подключены к первому и второму разрядам третьего выхода узла синхронизации, вход сброса первого триггера, вход сброса и вход установки 1 пятого триггера, входы синхронизации первого, второго, третьего и четвертого триггеров соединены с первого по седьмой разрядами девятого выхода узла постоянной памяти соответственно, вход режима узла синхронизации подключен к выходу пятого триггера, третий адресный вход узла постоянной памяти подключен к четвертому выходу узла

(-) - безразличное состояние управляющих сигналов.

Разряды

I

Назначение поля микрокоманды

36

S5

25 24

18

Адреса-первхода к следующей микрокоманде Y234 Условие перехода Y30l,(3:1)

Входной перенос в арифметико-логический блок Ґ272(2) Циклический сдвиг Y2720) Резерв

Запись в регистр операнда Y151 Запись в регистр числа Y152

Запись в регистр команды Y153 старшей секции 44 операционного блока 1 (адрес перехода)

Запись в регистр команды Y155 средней секции 43 операционного блока 1 (адрес операнда А)

Запись в регистр команды Y153 младшей секции 42 операционного блока 1 (адрес операнда В) Управление мультиплексором данных Y116(3:1) Управление мультиплексором выхода Y138(2:1) Модификация адреса в регистре команды Y156 Режим работы Y298(6:1),

Управление мультиплексором адреса Y232 (11:10) Запись в регистр адреса микрокоманды Y232(9) Запись в регистр команды блока адресации Y232(8) Запись в регистр вектора Y232(7) Запись в регистр данных Y232(6) Номер РОН Y232(5:1)

синхронизации, четвертый адресный вход узла постоянной памяти подключен к выходу узла селекции адреса, с первого по третий разряды пятого входа узла постоянной памяти подключены к выходам пятого, третьего и четвертого триггеров, шестой адресный вход узла постоянной памяти подключен к второму выходу регистра мик рокома нды, вход записи регистра микроко манды подключен к пятому выходу узла синхронизации, управляющий вход мультиплексора условий подключен к третьему выходу регистра микрокоманды

Таблица 1

Таблица-2

Таблица4

eote t,s7) 2г«.П

f

4s

0889Л91

Фиг. 5

г

&

1

Са са Схз (л Кз - Ci

ъ. ь.

Ы IV -1ч j

§

-X S5 5

(L t4i - С

ИЗ

а

J

Я§

SGч

§

.

9 wcb

0889Ш

j

Фиг. 10

soz

Ј9i

V Ш 6 14

0989191

о оо со ю г- со

fca

S

4s

h

S5

i :

C5

O)

J

(Л

со со

S ig

Фиг 17

Фаз. 18

XA

PiA

УА

т

400

FE feЈ

393

Ih

1

Wf

Фиг 19

Выборка

Фиг. 20

GG

395

U V

397

271

2

280

W

R

,288

2 ,2B5

277

исполнение

SLZ

9вг

юг

ш W

ш

JJ7

М2 6LZ

J Г

Ш ш

№

3

га

« 8 г/

и

Of

5

8 L 9 5

е

г

i

fe

езг

т

9

ш

о б

9

L

9 Ј Ј

г

i

ъ

892

Ш 161

262

Ш

0889Л91

Фиг. 22

| Клингман Э | |||

| Проектирование специали- зированных микропроцессорных систем | |||

| - М.: Мир, 1985, с | |||

| Способ получения бензонафтола | 1920 |

|

SU363A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-07—Публикация

1988-11-05—Подача