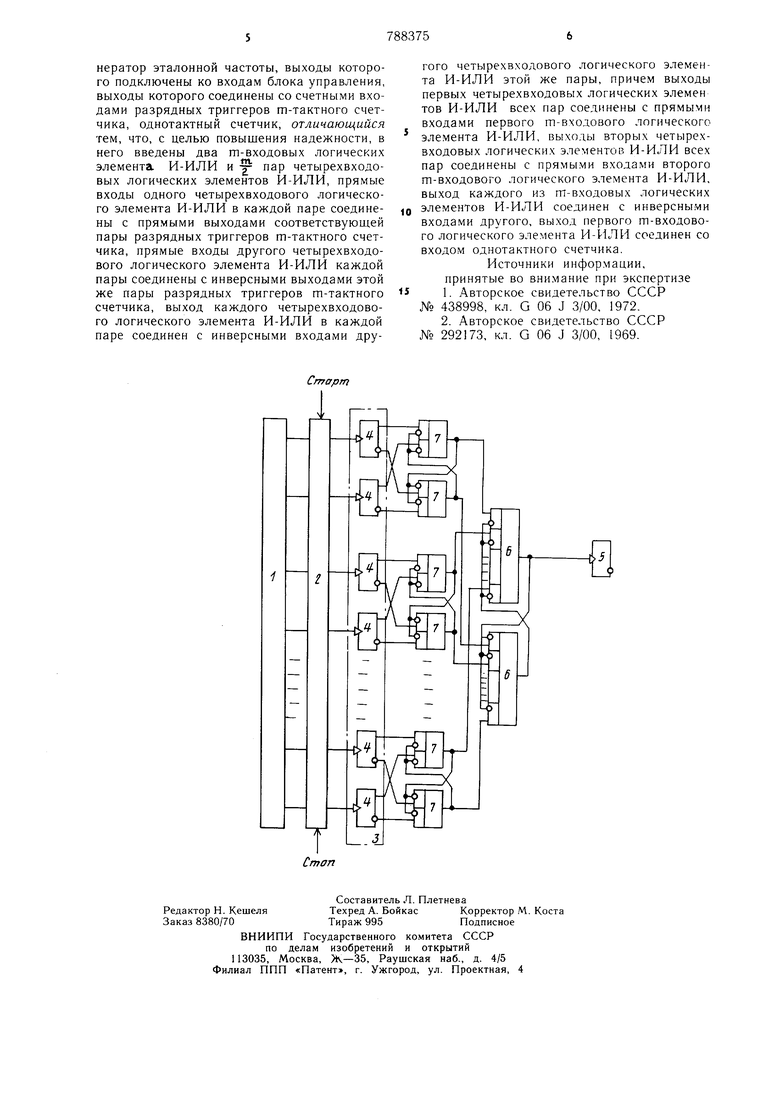

элемента И-ИЛИ в каждой паре соединен с инверсными входами другого четырехвходового ло1-ического элемента И-ИЛИ этой же пары, причем выходы первых четырехвходовых логических элементов И-ИЛИ всех пар соединены с прямыми входами первого ш-входового логического элемента И-ИЛИ, выходы вторых четырехвходовых логических элементов И-ИЛИ всех пар соединены с прямыми входами второго т-входового логического элемента И-ИЛИ, выход каждого из т-входовых логических элементов ИИЛИ соединен с инверсными входами другого, выход первого т-входового логического элемента И-ИЛИ соединен со входом однотактного счетчика. В предлагаемом устройстве независимо от количества тактов m максимальная частота переключения элементов не превысит значения f, а длительность импульса переноса будет равна t. На чертеже представлена схема преобразователя интервала времени в цифровой код. Схема содержит т-тактный генератор эталонной частоты 1, блок управления 2, управляемый старт- и стоп-импульсами, т-тактный счетчик 3, имеющий m разрядных триггеров 4 со счетным входом, однотактный счетчик 5, два т-входовых логических элемента И-ИЛИ 6, - пар четырехвходовых логических элементов И-ИЛИ 7. При поступлении в блок управления 2 старт-импульса на его выходах появляются импульсы т-тактного генератора эталонной частоты 1, которые поступают на счетные входы соответствующих разрядных триггеров 4 т-тактного счетчика. Разрядные триггеры 4 объединены в пары, на счетные входы разрядных триггеров 4 каждой пары с соответствующего выхода блока управления 2 поступают противофазные сигналы. На прямые входы одного четырехвходового логического элемента И-ИЛИ 7 в каждой паре подаются сигналы с прямых выходов соот.тствующей пары разрядных триггеров 4, на входы которых поступают противофазные сигналы с соответствующего выхода блока управления 2, а на прямые входы другого четырехвходового логического элемента И-ИЛИ каждой пары подаются сигналы с инверсных выходов этой же пары разрядных триггеров 4. Изменение сигналов на выходах каждого четырехвходового логического элемента И-ИЛИ 7 в каждой паре происходит в моменты времени, когда соединенные с ними соответствующие разрядные триггеры 4 оказываются или в состоянии логического нуля, или в состоянии логической единицы. За счет цепи обратной связи, связывающей выход каждого четырехвходового логического элемента И-ИЛИ 7 в каждой паре с инверсными входами другого четырехвходового логического элемента И-ИЛИ 7 в той же паре, это состояние сохраняется ДО момента очередного совпадения сигналов на прямых выходах другого tfeTbipexвходового логического элемента И-ИЛИ 7 этой же пары. Выходные сигналы с первых четырехвходовых логических элементов ИИЛИ 7 всех пар поступают на прямые входы первого т-входового логического элемента И ИЛИ 6, а выходные сигналы со вторых четырехвходовых логических элементов ИИЛИ 7 всех пар поступают на прямые входы второго т-входового логического элемента И-ИЛИ 6. При совпадении сигналов на прямых входах первого или второго т-входового логического элемента И-ИЛИ 6, которое происходит в моменты совпадения сигналов на выходах соответственно первых или вторых четырехвходовых логических элементов И-ИЛИ 7 всех пар, изменяется сигнал на противоположный на выходах каждого т-входового логического элемента ИИЛИ 6. Это состояние за счет цепи обратной связи, связывающей выход каждого твходового логического элемента И-ИЛИ 6 с инверсными входами другого т-входового логического элемента И-ИЛИ 6, сохраняется до очередного момента совпадения сигналов на прямых входах другого т-входового логического элемента И-ИЛИ 6. Период сигналов на выходе каждого т-входового логического элемента И-ИЛИ 6, так же, как и на выходе каждого четырехвходового логического элемента И-ИЛИ 7, равен 2Т. Форма сигналов на указанных выходах - меандр, т.е. длительность импульса переноса независимо от. количества тактов будет равнаТ. Сигнал с выхода первого т-входового логического элемента И-ИЛИ 6 поступает на счетный вход однотактного счетчика 5. В момент поступления в блок управления 2 стопимпульса прекращается подача эталонной частоты на входы разрядных триггеров 4. Результат преобразования фиксируется в однотактном счетчике 5, в т-входовых логических элементах И-ИЛИ бив разрядных триггерах 4 с дискретностью. Суммарная максимальная погрещность дискретности такого преобразователя интервала времени в цифровой код равна б + - ш. в предлагаемом преобразователе интервала времени в цифровой код можно получить погрешность элементах с предельной частотой переключения, равной f (для разрядных триггеров 4) и равной (для элементов 6, 7) и однотактного счетчика 5. Отсутствие быстродействующих элементов приводит к уменьщению потребляемой мощности и упрощению устройства, что и обеспечивает повыщение надежности преобразователя интервала времени в цифровой код. Формула изобретения Преобразователь интервала времени в цифровой код, содержащий т-тактный ге

| название | год | авторы | номер документа |

|---|---|---|---|

| М-тактный счетчик | 1979 |

|

SU966916A1 |

| Преобразователь интервала времени в цифровой код | 1981 |

|

SU980279A1 |

| Устройство измерения временных интервалов | 1984 |

|

SU1144062A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Счетчик импульсов в коде Грея (его варианты) | 1981 |

|

SU1026316A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2001 |

|

RU2189047C1 |

Авторы

Даты

1980-12-15—Публикация

1978-12-18—Подача