2. Счетчик имгтульсов в коде Грея, имеющий N разрядов и содержащий N-входовой суммато1э по модулю 2, входы которого соединены с прямыми выходами триггеров всех разрядов в каждом разряде с номером п, где п 2,3....(N-1), первую двухвходовую схему совпадения, выход которой соединен со счетным входом триггера, а первый вход - с прямым выходом триггера (п-1)-го разряда, о т л и ч а ющ и и с я тем, что, с целью повышения надежности, в него введены первый и второй дополнительные триггеры и в каждый разряд с номером п - вторая двух входовая схема совпадения, первый вход которой соединен с инверсным выходом триггера {п-1)-го разряда, второй вход - с вторым входом первой схемы совпадения и с выхо дом второй схемы совпадения (n-l)-ro разряда, а выход - с вторыми входами схем совпадения (п+1) го разряда, счетные входы первого и второго дополнительных триггеров соединены с шиной счетных импульсов, входы сбро.сов - соответственно с инверсным и прямь1м выходами сумматора, а прямые выходы - соответственно со счетным входом триггера первого разряда и с вторыми входами схем совпадения второго разряда, выход второй схемы совпадения (N-l)-ro разряда соединен со счетным входом триггера N-ro разряда,

3. Счетчик импульсов в коде Грея, имеющий N разрядов и содержащий Н-входовой сумматор по модулю 2, вхоДЫ которого соединены с прямыми вы- ходами триггеров всех разрядов, и в каждом разряде с номером п, где п « 1,2,3...(N-1), первую двухвходовую схему совпадения, выход которой соединен со счетным входом триггера, а первый вход - с прямым выходом триггера (n-l)-ro разряда, отличающий с я тем, что, с целью повышения надежности, в него введены первый и второй дополнительные триггеры и в каждый разряд с номером п - вторая двухвходовая схема совпадения,первый вход которой соединен с инверсным выходом триггера Сп-1)-го разряда, второй вход - с вторым входом первой схемы совпадения и с выходом второй схемы совпадения (п-1.)-го разряда, а выход - с вторыми входами схем совпадения (п+1)-го разряда, счетные входы первого и второго дополнительных три гг-еров соединены с шиной счетных импульсов и через ин-. вертор - с вторыми входами схем совпадения первого разряда, входы сброса - соответственно с инверсным и прямым выходами сумматора, а прямые выходы - с первыми входами соответственно первой и второй схем совпадения первого разряд а, при чем выход второйсхемы совпадения (N-l)-ro разряда соединен со счетным входом триггера N-ro разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Генератор функций Уолша | 1982 |

|

SU1043614A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Устройство для управления инвертором | 1980 |

|

SU938355A1 |

| Генератор функций Уолша | 1987 |

|

SU1501019A2 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Многоточечный сигнализатор уровня | 1982 |

|

SU1114889A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ T-КОДОВ | 1991 |

|

RU2026608C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

1. Счетчик импульсов в коде Гре Iимеющий N разрядов и содержащий N-BX довой сумматор по модулю 2,входы кот рого, соединены с прямыми выходами триггеров всех разрядов,и в каждом разряде с номером п,где ,3,4...N, п-входовую схему совпадения, выход которой соединен со сметным входом триггера, первые входы всех схем совпадения соединены между собой, вто,рой вход соединен с прямым выходом триггера (n-l)-ro разряда, остальные (п-2) входа - с инверсными выходами триггеров младших разрядов с номерами от 1 до (п-2), о т л и ч а ю щ и йс я тем, что, с целью повышений надежности , в него введены первый и второй дополнительные триггеры, счетные входы которых соединены с входной шиной, входы сброса - соответственно с инверсным и прямым выходами сумматора, а прямые выходы - соответственно со счетным входом триггера первого разряда и с первыми входами схем совпадения .

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.:

Известен счетчик импульсов в коде 5 Грея, содержащий в каждом разряде триггер, первую и вторую рхемы совпаден я и сумматор по модулю 2, первый вход которого соединен с выходом сумматора последующего разряда, а вы- О ход - с первым входом сумматора предыдущего разряда D }

Этот счетчик не обладает дocтatoчной надежностью.

Известен также счетчик импульсов 15 в коде Грея, содержащий сумматор по модулю 2, входы которого соединены

с прямыми выходами триггеров разрядов, и в каждом разряде схему совпадения , выход которой соединен ссС . счетным входом триггера, первые входы соединены меж/)у собой, второй вход соединен с прямым выходом триггера предыдущего разряда, а остальные входы - с инверсными выходами триггеров младших разрядов Г 21.

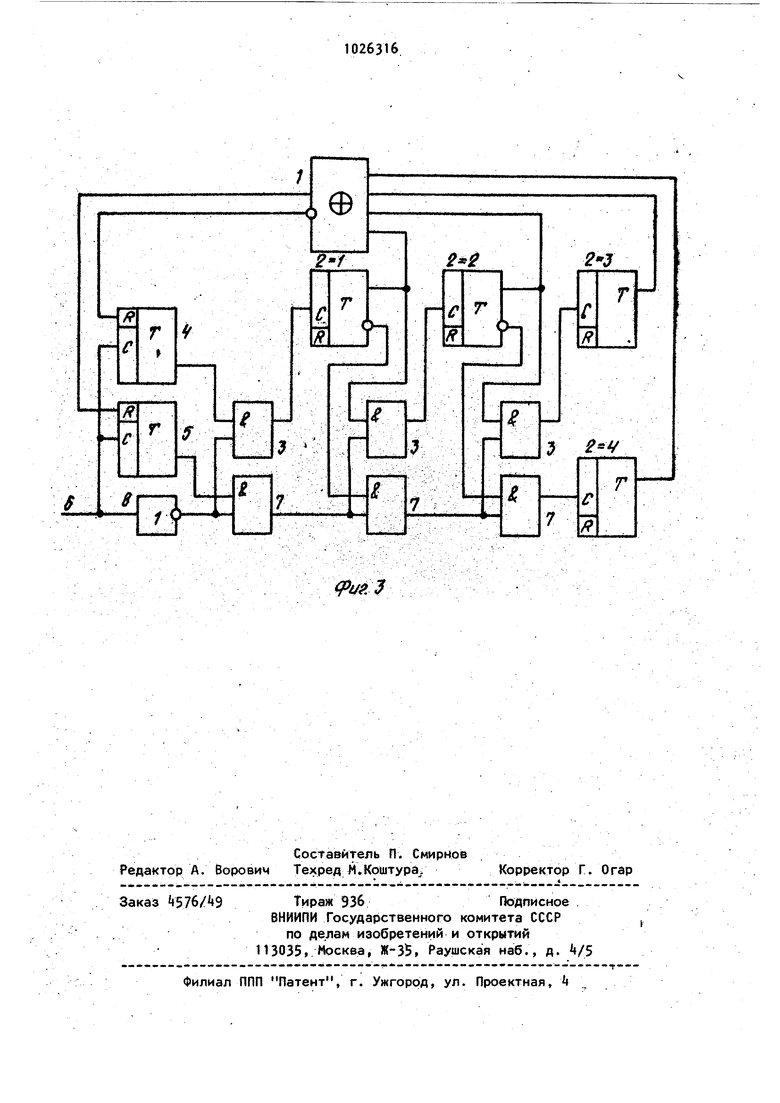

Недостатком указанного рчётчика является низкая надежность, связанная со сложностью схемы, а также с критичностью к длительности счетного импульса поскольку длительность импульса должнё быть достаточной для переключения триггера любого разряда счетчика, но не должна приводить к последовательному переключению триггеров двух разрядов. Цель изобретения - поЁышение надежности. В первом варианте поставленная цель достигается тем, что в счетчик импульсов в коде Грея, имеющий N разрядов и содержащий N-входовой сум матор по модулю 2, входы-которого соединены с прямыми выходами триггеров всех разрядов, и в каждом разряд с номером п, где п«2,3,.. .N, п-входовую схему совпадения, выход которой соединен, со счетным входом триггера, первые входы всех схем совпаде ния соединены между собой, второй вход соединен с прямым выходом триггера (n-l)-ro разряда, остальные (п-2)-входа - с инверсными выходами триггеров младших разрядов с номерами от 1 до (п-2), введены первый и второй дополнительные триггеры, счетные входы которых соединены с входной ШИ ной, входы сброса - соответственно с инверсным и прямым выходами сумма тора, а прямые выходы - соответствен но со счетным входом триггера первог разряда и с первыми входами схем сов падения. Во втором варианте поставленная цель, достигается тем, что в счетчик импульсов в коде Грея, имеющий N раз рядов и содержащий N-входовой сумматор по модулю 2, входы которого соединены с прямыми выходами триггеров всех разрядов, в каждом разряде с но мером п, где ,3...(N-1), первую двухвходовую схему совпадения, выход которойсоединен со счетным входом триггера, а первый вход - с прямым выходом триггера (n-l)-ro разряда, введены первый и второй дополнительные триггеры и в каждый разряд с номером п - вторая двухвходовая схема совпадения, первый вход которой соединен с инверсным выходом триггера {п-1)-го разряда, второй вход - с вtopым входом первой схемы совпадени И с выходом второй схемы совпадения (п-1)-го разряда, а выход - с вторыми входами схем совпадения (п+1)-го разряда, сметные входы первого и вто рого дополнительных триггеров соединены с шиной счетных импульсов, входы сброса - соответственно с инверсным прямым выходами сумматора, а прямые выходы - соответственно со счетным входом триггера первого разряда и с вторыми входами схем совпа дения второго разряда, выход второй схемы совпадения (N-l) разряда соединен со счетным входом триггера N-ro разряда. В третьем варианте поставленная цель достигается тем, что в счетчик импульсов в коде Грея, имеющий N разрядов и содержащий N-входовой сумматор по моду/то 2, входы которого соединены с прямыми, выходами тригге-. ров всех разрядов, ив каждом разряде с номером п, где ,2,3...(N-1), первую двухвходовую схему совпадения, выход которой соединен со счетным входом триггера, а .первый вход - с Прямым выходом триггера (п-1)-го разряда введены первый и второй допол- нительные триггеры и в каждый разряд с номером п - вторая двухвходовая схема совпадения, первый вход которой соединен с инверсным выходом триггера (n-t)-ro разряда, второй вход - с вторым входом первой схемы совпадения и с выходом второй схемы совпадения (п-1)-го разряда, а выход - с вторыми входами схем совпадения (п+1)-го разряда, счетные входы первого и второго дополнительных триггеров соединены с шиной счетных импульсов и через инвертор - с вторыми входами схем совпадения первого разряда, входы сброса - соответственно с инверс.ным и прямым выходами сумматора, а прямые выходы - с первыми входами соответственно первой и второй схем совпадения первого разряда, причем выход второй схемы совпадения (N-l)-ro разряда соединен со счетным входом триггера N-ro разряда. Критичность к длительности счетного импульса исключена путем запрета прохождения каждого счетного импуль-. са на вход любого триггера, кроме переключаемого в данном такте. На фиг. 1 приведена схема первого варианта четырехразрядного счетчика импульсов; на фиг. 2 - схема второго варианта; на фиг. 3 - схема третьего варианта. ;Г Первый вариант счетчика импульсов содержит четырехвходовой сумматор 1 по модулю 2, входы которого с прямыми выходами триггеров первого 2-1, второго 2-2,третьего 2-3 и четвертого 2-4 разрядов соответственно, в каждом разряде с номером п, где ,3,t, п-входовые схемы 3 совпадения, первые входы все( схем совпадения соединены между собой, выход каждой схемы 3 совпадения соединен со счетным входом триггера соответствующего разрядаi второй вход - с прямым выходом триггера (n-l)-ro разряда, остальные (п-2) входа - с инверсными выходами триггеров младошх разрядов с номерами от 1 до Сп-2), счетные входы первого и второго дополнительных триггеров соединены с шиной 6 счетных импульсов, входы сброса соответственно с инверсным и прямым выходами сумматора 1, а прямые выходы соответственно со счетным входом триггера первого разряда и с первыми входами схем 3 совпадения./

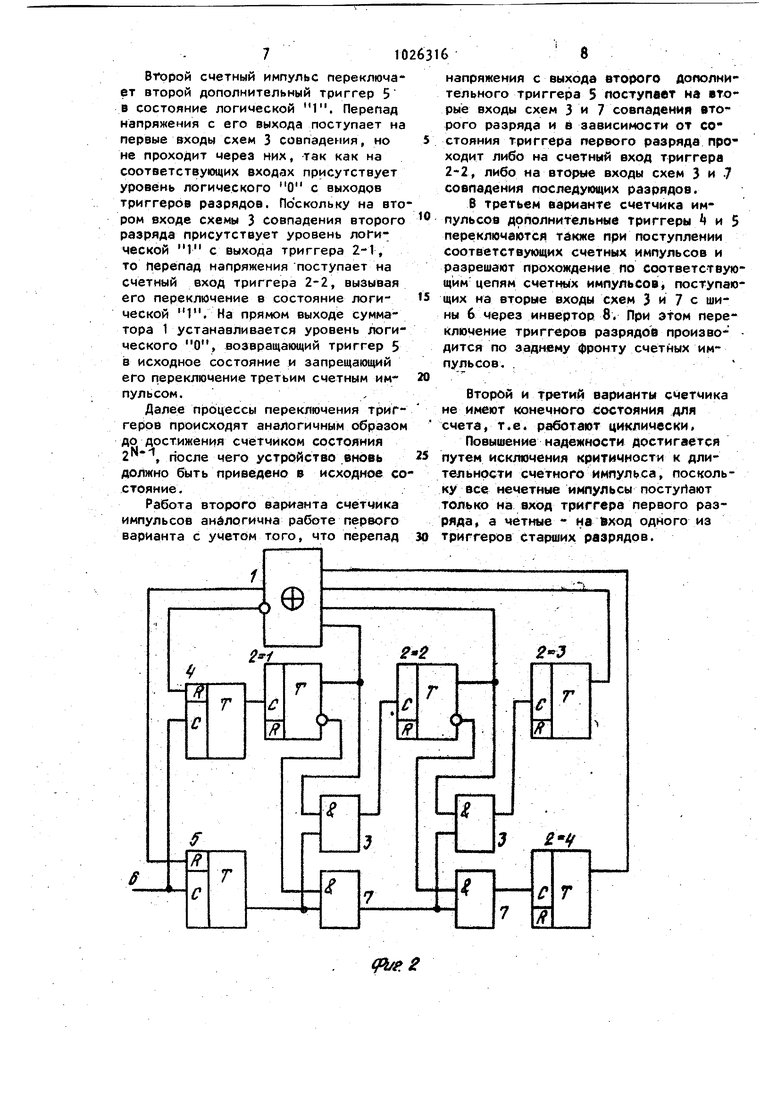

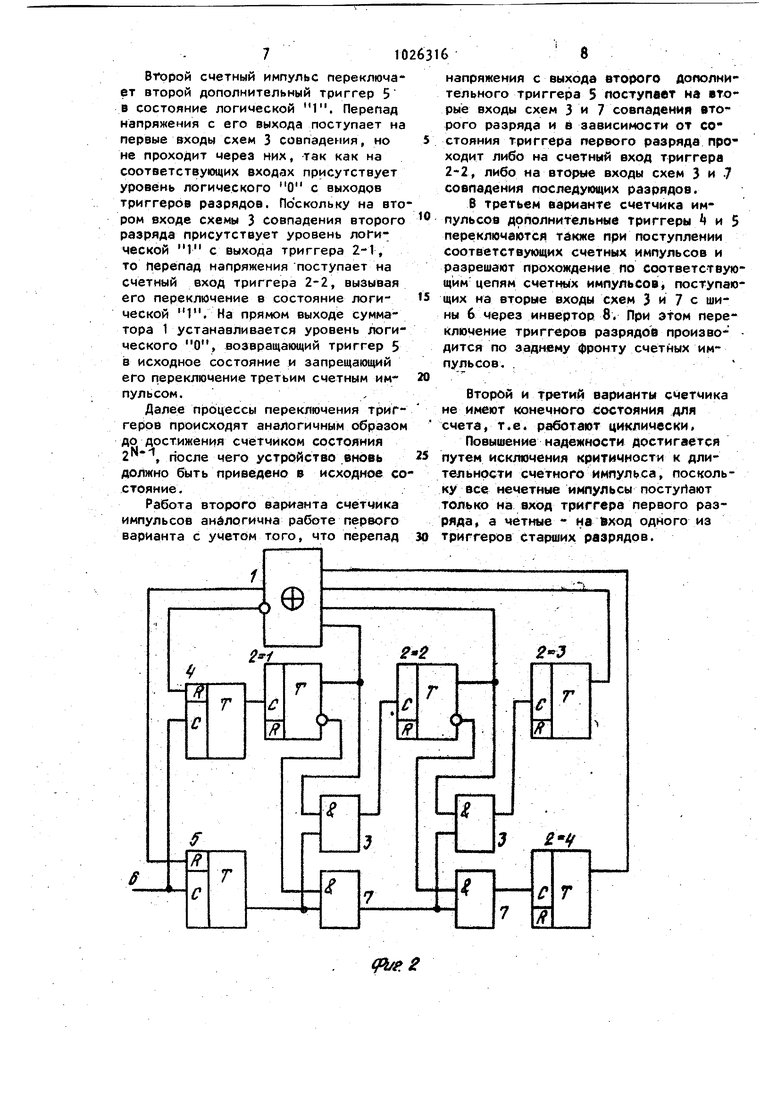

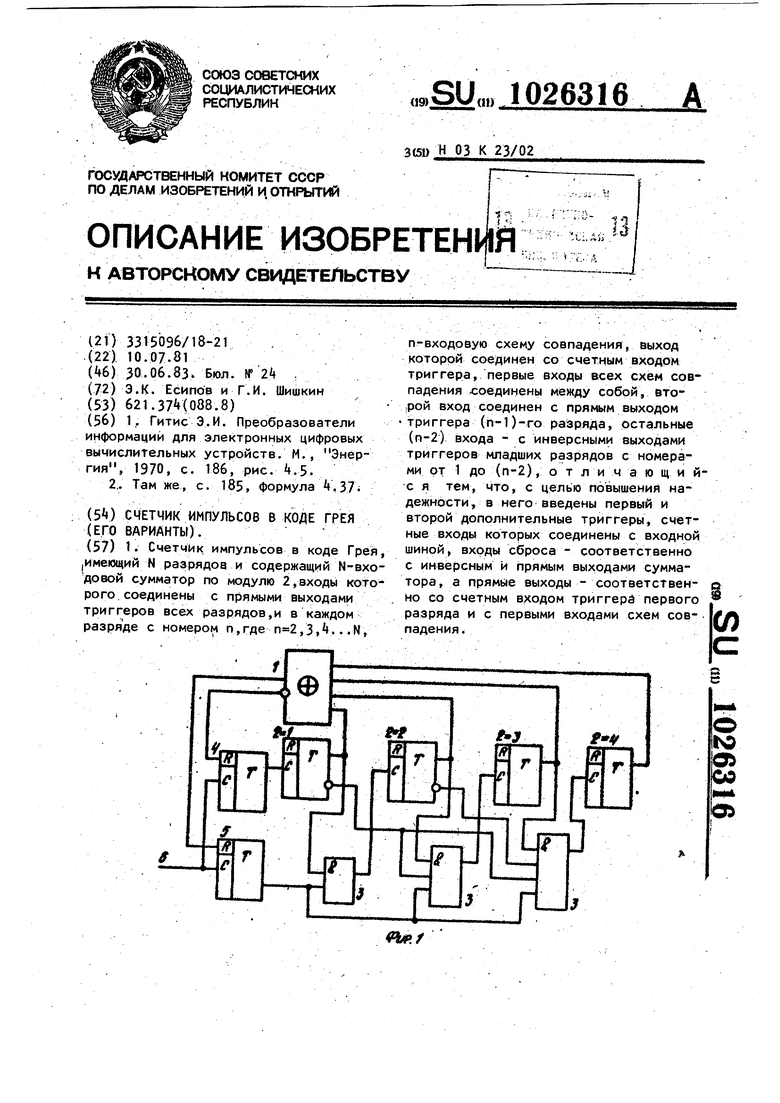

Второй вариант счетчика импульсов содержит четырехвходовой сумматор 1 гю подулю 2, входы которого соединены с прямыми выходами триггеров первого 2-1, второго 2-2, третьего и четвертого 2-А разрядов соответственно ив каждом разряде с номером ri, где ,3, первую 3 и вторую 7 двух вхрдовые схемы совпадения, выход первой схемы совпадения соединен со счетным входом триггера соотаетствующего разряда, а первый вход - с пря мым выходом триггера (п-1)-го разряда, счетные входы первого и второго дополни тел ьных три г геров , 5 соедиме ны с шиной 6 счетных импульсов, входы сброса - соответственно с инверс ным и прямым выходами сумматора Т« а прямые выходы - соответственно со счетным входом триггера первого разряда и с вторыми входами первой и вто рой схем 3i 7 совпадения бторого разряда, первы(| вход второй двухвходовой схемы 7 совпадения разряда с номером п соединен с инверсным выходом триггера (п-1)-го разряда, второй Вход двухвходовой схемы 7 совпадения каждого разряда,начиная с третьего; соединен с вторым входом первой схемы 3 совпадения этого же разряда и с выходом второй схемы 7 совпадения предыдущего разряда.

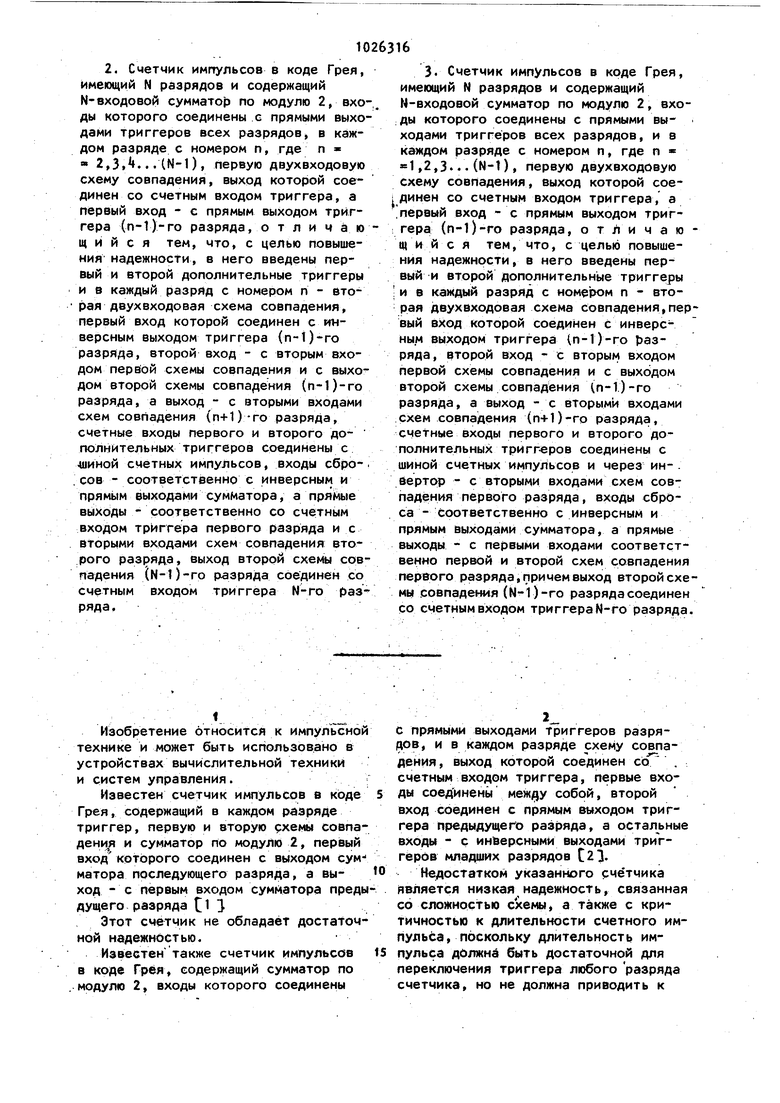

Третий вариант счетчика импульсов содержит четырехвходовой сумматор 1 по модулю 2, входы которого соединены с прямыми выходами триггеров первого 2-1, второго 2-2, третьего 2-3 и четвертого 2- разрядов соответственно, и в каждом разряде с номером п, где ,2,3, первую двухвходовую схему 3 совпадения, выход которой

соединен со счетным входом триггера того же разряда, а первый вход - с прямым выходом триггера (n-l)rro разряда, счетные входы первого и второго дополнительных триггеров f, 5 сое|Динены с Шиной 6 счетных импульсов, входы Сброса - соответственно с инверсным и прямым выходами сумматора 1, а прямые выходы с первыми входами соответственно первой и второй двухвходовых схем 3, 7 совладения первого разряда, BTopbie входы которых через инвертор 8 соединены с шиной 6 счетных импульсов. Первые входы вторых схем 7 совпадения второго и третьего разрядов соединены с инверсными выходами триггеров 2-1 и 2-2 первого и .второго разрядов соответственно, а втбрые входы - с вторыми входами первых схем 3 совпадения того же разряда и с выходами вtopыx схем 7 совпадения преды1дущих разрядов, причем выход второй схемы совпадения третьего разряда соединен со счетным входом триггера четвертого разряда.

вариант счетчика импульсов в Грея работает следующим образом.. . . , ; ;- .

. Перед подачей счетных импульсов по ши«е 6 триггеры разрядов и дополнительный триггер устанавливаются в состояние логического О внешним импульсом обнуления. После окончания импульса обнуления дополнительный триггер i готов к переключению, второй дополнительный триггер 5 удерживается Ef состоянии логического О уровнем логического , поступающим на. Rrвход С прямого выхода сумматора 1,.: - : ,,/,.

При поступлении первого счетного |Импульса по шине 6 первый дополнитель(ный триггер k переключается в состояние логической 1. Перепад напряжения с его прямого выхода поступает на счетный вход триггера первого разряд и вызывает его переключение. При этом изменяются потенциалы на выходах сумматора 1. Уровень логического О с инверсного выхода сумматора 1 поступает на R-вход перёого дополнительного триггера k и вызывает возвращение его в исходное состояние. Уровень логической 1, поступающий с инверсного выхода сумматора 1 на R-вход вtopo o дополнительного триг гера 5, разрешает его переключение вторым счетным импульсом. Второй счетный импульс переключает второй дополнительный триггер 5 в состояние логической 1. Перепад напряжения с его выхода поступает на первые входы схем 3 совпадения, но не проходит через них, так как на соответствующих входах присутствует уровень логического О с выходов триггеров разрядов. Поскольку на вто ром входе схемы 3 совпадения второго разряда присутствует уровень логической 1 с выхода триггера 2-1, то перепад напряжения поступает на счетный вход триггера 2-2, вызывая его переключение в состояние логической 1. На прямом выходе сумматора 1 устанавливается уровень логического О, возвращающий триггер 5 в исходное состояние и запрещающий его переключение третьим счетным им пульсом.. Далее процессы переключения триггеров происходят аналогичным образом до достижения счетчиком состояния , после чего устройство вновь должно быть приведено в исходное со стояние. Работа второго счетчика импульсов аналогична работе первого варианта с учетом того, что перепад

. 2 напряжения с выхода второго дополнительного триггера 5 ооступввт на вторые входы схем 3 и 7 совпадения второго разряда и в зависимости от состояния триггера первого разряда про ходит либо на счетный вход триггера 2-2, либо на вторые входы схем 3 и 7 совпадения последующих разрядов. В третьем варианте счетчика импульсов дополнительные триггеры i и 5 переключаются также при поступлении соответствующих счетных импульсов и разрешают прохождение по соответствующим цепям счетных импульсов, поступающих на вторые входы схем 3 и 7 с шины 6 через инвертор 8. При этом переключение триггеров разрядов производится по заднему фронту счетных импульсов. . Второй и третий варианты счетчика не имеют ««знечного состояния для счета, т.е. работают циклически. Повышение надежности достигается путем исключения критичности к длительности счетного импул« са, поскольку все нечетные импульсы поступают только на вход триггера первого разряда, а четные - на вход одного из триггеров Старших разрядов.

Й Д

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., Энергия, 1970, с | |||

| Пружинная погонялка к ткацким станкам | 1923 |

|

SU186A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Там же, с | |||

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

Авторы

Даты

1983-06-30—Публикация

1981-07-10—Подача