Изобретение относится к автоматическому контролю и может быть использовано для контроля электрических параметров систем управления различных объектов. Известно устройство, содержащее блок коммутации, блок программного упраблэння. Вычислитель, блок преобразования и измерения, генератор входных, воздействий, блок ввода, блок индикации и пульт управления flT,. Недостаток этого устройства заключается в ограниченном объеме получаемой диагностической информации, что затрудняетлокализацию неисправности. Наиболее близким по технической сущ ности к предлагаемому является устройст во для контроля систем управления, содержащее коммутатор, выход которого соединен с информационным входом блока преобразователей, информационным выхо, дом подключенного к первому информационному входу арифметическо-логическкого блока, первый информационный выход которого подсоединен к первому ин,формационному входу блока индикации, второй информационный выход и второй информационный вход - к первому инфор мационному входу и первому информационному выходу- блока памяти соответственно, первый управляющий выход - к первому управляющему входу блока управления, первой группой управляющих выходов соединенного с управляющими входами коммутатора, блока преобразователей, блока памяти, блока индикации н арифметическо-логического блока соответственно, второй, третьей и четвертой группой управляющих входов - с первым н вторым управляющими выходами пульта управления, а также со вторым управляющим выходом арифметйческо-логического блока соответственно .Bjib изобретения - рюсширенве функциональных возможностей устройства, обеспечивающее увеличение глубины контроля, упрощение диагностики неисправности и сокращение времени диагностики.

Поставленная цель достигается тем, . что устройство содержит блок считывания

диагностической информации, информационный вход которого подключен к информационному выходу пульта управления, пер- вый, второй и третий управляющие входы к первому и второму управляющим выходам пульта управления и второму управляющему выходу арифметическо-погического блока соответственно, первый адрес- ный выход - ко второму информационному Входу блока индикации, а второй адресный выход - ко, второму информационно му входу блока памяти, Лричем блок;

считывания диагностической информации Js содержит первый и второй элементы И, элемент ИЛИ, генератор сигналов сдвига, . первый, второй, третий и четвертый узлы элементов И, формирователь импульсов,, счетчик, триггер, шифратор, а также20

сдвиговый и буферный регистры, первый и второй входы первого элемента И подключены к первому и третьему управляющим входам блока соответственно, выход т к управляющему входу первого узла эле- 25 ментов И, информационный вход которого соединен с информационным входом блока, а выходы - с соответствующими уп равляющимгг входамй элемента ИЛИ и ин, формационными- входами шифратора, ин- ,30 формационные, выходы которого подключены к соответствующим информационным входам второго узла элементов И, выходами подсоединенного к соответствующим информационным входам сдвигового ре- j гистра, выходы которого подключены к информационным входам третьего и четвертого узлов элементов И соответственно, выходы четвертого узла элементов И соединены через буферный регистр с соот- Q ветствующими вторыми адресными выходами блока, выход элемента ИЛИ подщиочен к входу формирователя импульсов, первый управляющий выход которого соединен с управляющим входом второго уз- 5 ла элементов И и первым входом второго элемента И, а второй выход - с управч ляющим входом счетчика, первым счетным выходом подключенного к первому цереклю, чающему входу триггера, управляющим

выходом - к второму переключающему входу триггера и управляющему входу, третьего узла элементов И, выход триггера соединен с вторым входом третьего элемента И, выход которого через гене- .,

ратор сигналрв сдвига подключен к синхронизирующему входу сдвигового регист-, ра, второй управляющий вход блока соединен с управляющим входом четвертого

узла элементов И, выход третьего узла элементов И подключен к первому адресному выходу блока.

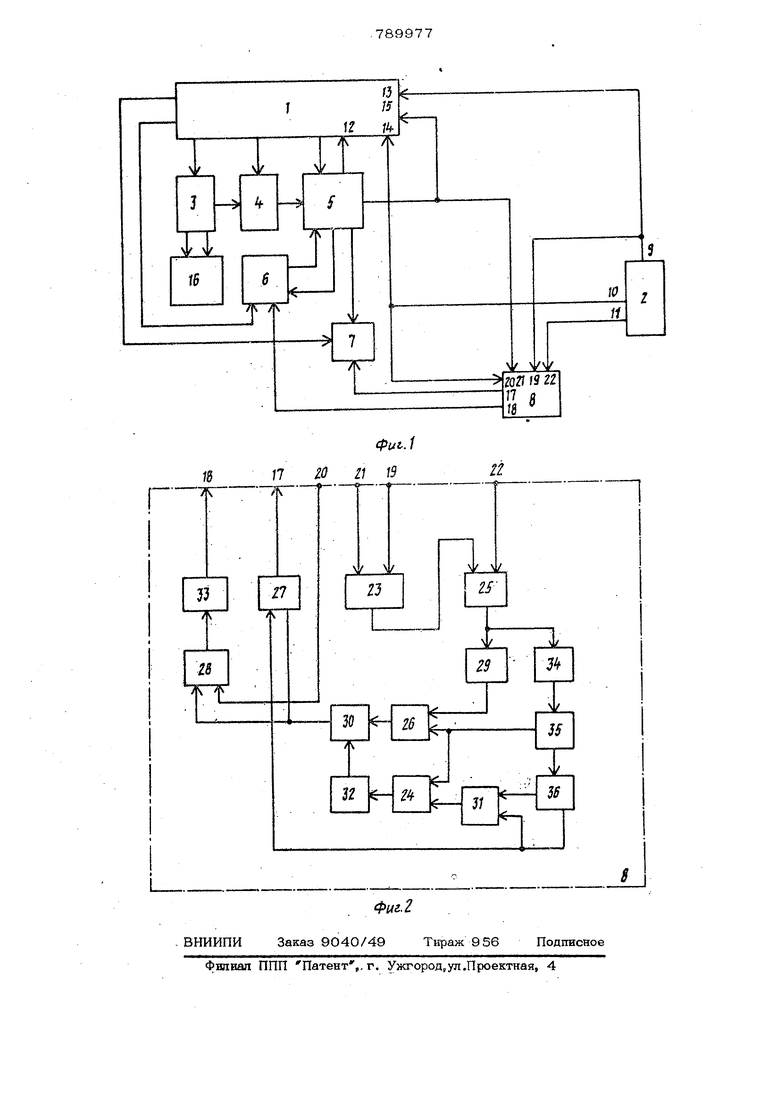

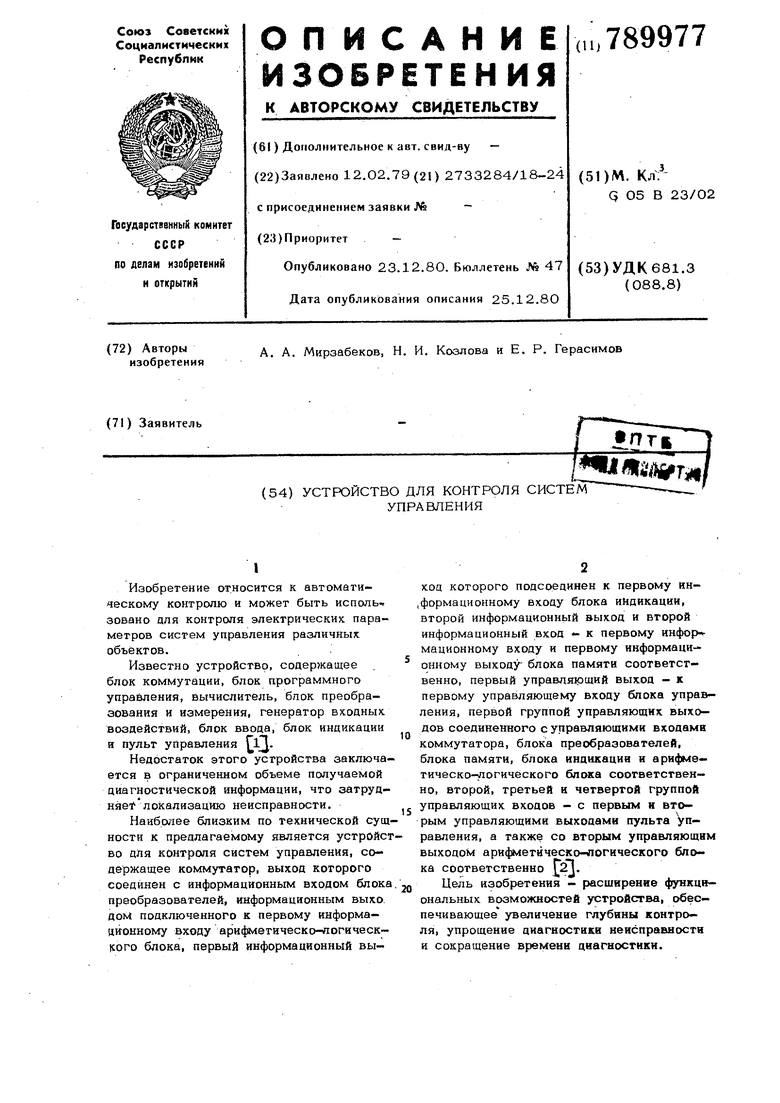

На фиг. 1 представлена 6jiOK - схема устройства ( цепи сброса, устанавливаю-щие элементы в исходное состояние , нг показаны); на фиг. 2 - блок-схема счи-i тывания диагностической информации.

Устройство содержит блок 1 управления, пульт 2 управления, коммутатор 3, блок 4 преобразователей, арифметико-логический блок 5, блок 6 памяти, блок 7 индикации, блок 8 считывания диагностической информации, первый, второй управляющие и информационный выходы 9-11 пульта управления, первый, второй, третий и четвертый управляющие входы 12-15 пульта упр авления, объект 16 контроля, первый 17 и второй 18 адресные выходы блока считывания диагностической информации, первый, второй, третий управляющие и информационный входы 19-22 блока считывания диагностической информации, первый 23 и второй 24 элементы И, пер,вый, второй, третий и четвертый узлы 25-28 элементов И, шифратор 29, сдвиговый регистр 30, триггер 31, генератор 32 импульсов, буферный регистр 33, элемент ИЛИ 34, формирователь 35 импульсов, счетчик 36.

Устройство работает следующим образом.

Программа контроля жестко заложена в схему блока 1 управления и начинает последовательно выполняться по нажатию кнопки Пуск на пульте 2 управления. Цикл контроля электрических параметров системы управления состоит из последовательности отдельных проверок (шагов), вьшолняемык в автоматическом или полу- , автоматическом режимах, задаваемых с помощью органов управления пульта 2. Сигналы выбора типа режима и сигналы управления ,поступают на блок 1 с выхода 9 пульта 2. Переход к следующей проверке определяется сигналом Годен на входе 12 блока 1, а прекращение процесса контрачя, снятие питания с объекта 16 и выдача информации для высвет- ки на индикаторах блока 7 индикации в виде номера проверки и значения контролируемого параметра - сигналом Не годен на входе 15 блока 1. В соответствии с программой контроля вкоды и выходы объекта 16 подключаются через коммутатор 3 к блоку 4 преобразователей. Результат -преобразования поступает в блок 5( куда предварительно заносятся с блока 6 необходимые -исходные данные и значения цопусков контролируемого пара метра. В процессе контроля в соогветст вующие ячейки блока 6 памяти заноситс оперативная информация (данные, обеспе чивающие и контролирующие нормальное состояние устройства и объекта контрол (Гак с блока 1, так и с блока 5. На ос-цовании логической оценки получаемых данных блок 5 формирует сигнал Годен на первом управляющем выходе, если контролируемый параметр находится в прецелах допуска, или сигнал Не годен на втором управляющем выходе, если параметр находится за пределами допус- ка. Эти сигналы поступают на соответст вующие входы блока 1, Кроме того, сигнал, Не годен формируется и в том случае, когда происходит нарушение исходной или оперативной информации, оп- ределяющих правильное протекание процесса контроля, т. е. когда возникает неисправность в системе объект контроля - устройство контроля. Тогда вслучае выбора режима контроля с диагности кой неисправности, что задае гся отдельным признаком с управляющего выхода 9 пульта 2 управления .с помощью, например переключателя, останавливается лишь автоматический процесс контроля к не допускается его продолжение. Сигнал Не годен поступает на вход 21, а приз нак режима на вход -19 блока 8 и элемент И 23 формирует разрешающий сигнал на входе узла. 25 элементов И. Опе ратор получает возможность с помощью информационных сигналов с выхода 11 пульта 2, поступающих на вход 22 блока 8, считывать всю необходимую информацию из ячеек блока 6 для угочне™ ния и увеличения глубины диагностики неисправности. Адрес ячеек формируется следующим образом. Последовательным нансатием цифровых клавиш на пульте 2 вырабатываются информационные сигналы на выходе 11 и поступают на вход узла 25 элементов И. Сигнал с выходов узла 25 одновременно через элемент ИЛИ 34 запускает формирователь 35 импульсов и инициирует на выходе шифратора 29 сигналы двоичного кода, соответствующи цифре нажатой клавиши. Прохождение информации через узел 26 элементов И на сдвиговый регистр 30 обеспечивается разрешающим сигналом со второго выхо- да формирователя 35. Этот же сигнал через элемент И 24, при условии накождения триггера 31 в исходном состоянии запускает генератор 32 сигналов сдзига обесп чивая тем самым преобразование последовательного поразрядного кода адреса в параллельный - в одно двоичное слово. Сигнал с первого выхода формирователя 35, сдвинутый во времени по отношению к сигналу второго выхода, активизирует вход счегчнка 36, который производит подсчет введенных разрядов адреса к после ввода предпоследнего разряда сигналом с выхода переютючает триггер 31, запрещая генератора 32 при вводе последнего разряда адреса. Так осуществляется использование сшвигового регистра 30 без дополнительных буфер- / ыых: разрядов. После ввода последнего разряда сигналом переполнения с выхо«. да счетчика 36 производится через узел 27 элементов И и выход 17 блока 8 перепись содержимого регистра 30 в блок 7 индикации и высветка значения адреса для визуального контроля,- и одновременно триггер 31 устанавливается в в исходное состояние. Конец формирования адреса и начало передачи его на вход блока 6 через узел 28 элементов И, бу4)ерный регистр 33 и выход 18 блока 8 фиксируется управляющим сигналом . с выхода 10 пульта 2, поступающим на вход 20 блока 8 и вырабатываемым при нажатии на клавишу, например Вводвывод пульта 2. По указанному сигналу через блок 1 формируются сигналы -считывания в блоке 6 информации по наб-. . ранному адресу к высветки ее на аругой группе индикаторов блока 7-, Таким образом, предлагаемое изобре тение дает возможность без существенного услоншения алгоритма контроля и аппаратуры Лолучить аополките.г1ьную информацию, увеличивающую глубпну контроля. изобретения о р м у л 1. Устройство для контроля систем управления, содержащее коммутатор, вы- код которого соединен с информационным входом блока преобразователей, информационным выходом подключенного к первому информацнЬннрму входу арнфмети- ческо-логического блока, первый информационный выход которого подсоединен к первому инфopмaциoннo лy входу блока индпкацни, второй информационный выход и второй информационный вход - к первому информационному входу и первому информационному выходу блока памяти соответственно, первый управляющий выход - к первому управляющему входу блока управления, первой группой управляющих выходов соединенного с управляющими входами коммутатора, блока преобразователей, блока памяти, блока индикации и ари4метическо-логического блока соответственно, второй, третьей и четвертой группой управляющих входов - с первым и вторым управляющими выходами пульта управления, а также со вторым управляющим выходом арифметнческо-логического блока соответстч веяно, отличающееся тем, что, с целью увеличения глубины контроля, устройство содержит блок считывания диагностической информации, информационный вход которого подключен . к информационному выходу пульта управления, первый, второй и третий управляющие входы - к первому и второму управляющим выходам пульта управления и второму управляющему выходу ариф- метнческо-логического блока соответственно, первый адресный выход - к второ му информационному входу блока индикации, а второй адресный выход - к втоп рому информационному входу блока памяти.

2. Устройство по п. 1, отлича ю щ е е с я тем, что блок считывания диагностической информации содержит первый и второй элементы И, элемент ИЛИ, генератор сигналов сдвига, первый второй, третий и четвертый узлы элемен тов И, формирователь импульсов, счетчик триггер, шифратор, а также сдвиговый и буферный регистры, первый и второй вхо ды первого элемента И подключены к первому и третьему управляющим входам блока соответственно, выход - к управля ющему входу первого узла элементов И, информационый вход которого соединен с информационным входом блока, а выходы

соответствующими управляющими входаи элемента ИЛИ и информационными входами шифратора, информационные выходы которого, подключены к соответстующим информационным входам второго узла элементов И, выходами подсоединен ного к соответствующим информационным входам сдвигового регистра, выходы которого подключены к информационным вхо. дам третьего и четвертого узлов элементов И соответственно, выходы четвертого узла элементов И соединены через буферный регистр с соответствующими вторыми адресными выходами блока, выход элемента ИЛИ подключен к входу формирователя импульсов, первый управляющий выход которого соединен с управляющим входом второго узла элементов И и первым входом второго элемента И, а второй выход - с управляющим входом счетчика, первым счетным выходом подключенного к первому переключающему входу триггера, управляющим выходом к второму переключающему входу триггера и управляющему входу третьего узла элементов И, выход триггера соединен со- вторым входом третьего элемента И, выход которого через генератор сигналов сдвига подключен к синхронизирующему входу сдвигового регистра, второй управляющий вход блока соединен с управляющим входом четвертого узла элементов И, выход Третьего узла элементов И подключен к первому адресному выходу блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 600560, кл. QI 06 R 11/00, 1976.

ч

2.Авторское свидетельство СССР

, кл. 06 F 15/46, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для сопряжения датчиков с электронной вычислительной машиной | 1984 |

|

SU1208557A2 |

| ОПТИЧЕСКОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2035069C1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

Авторы

Даты

1980-12-23—Публикация

1979-02-12—Подача