1

Изобретение относится к вычислительной технике и предназначено для групнового управления манипуляторами и монтажно-сборочным оборудованием в системах реального масштаба времени.

Целью изобретения является увеличение допустимого количества уп- равляем1ых от ЭВМ датчиков.

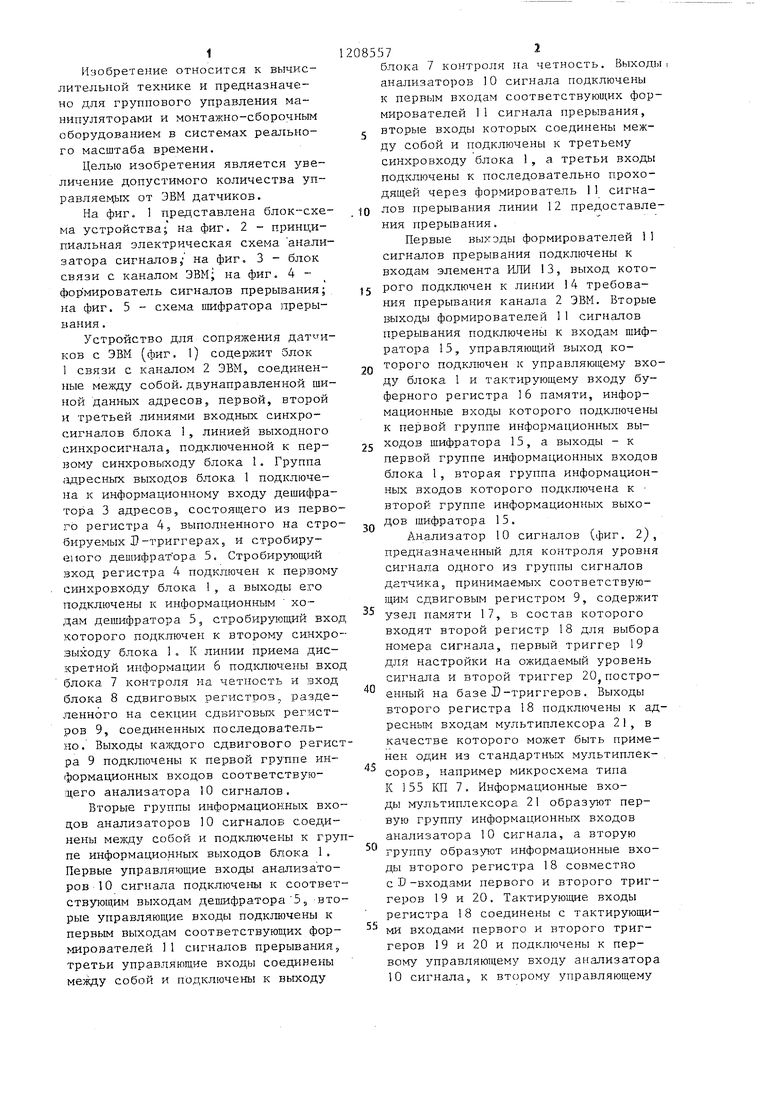

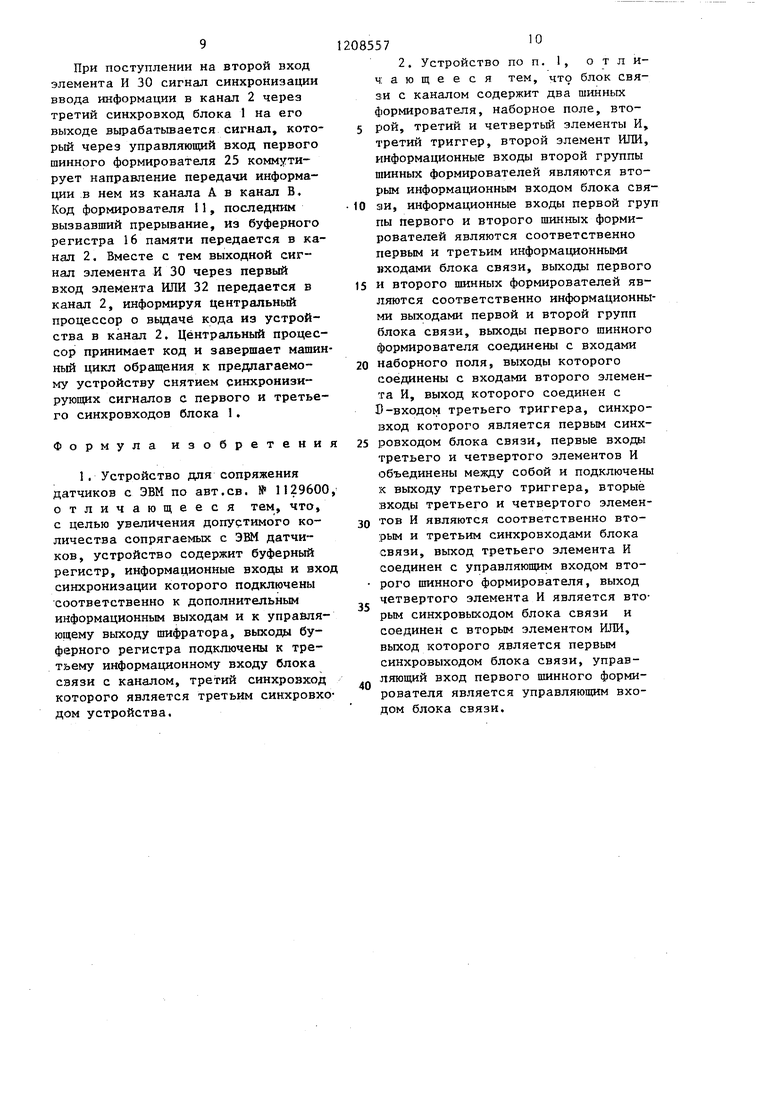

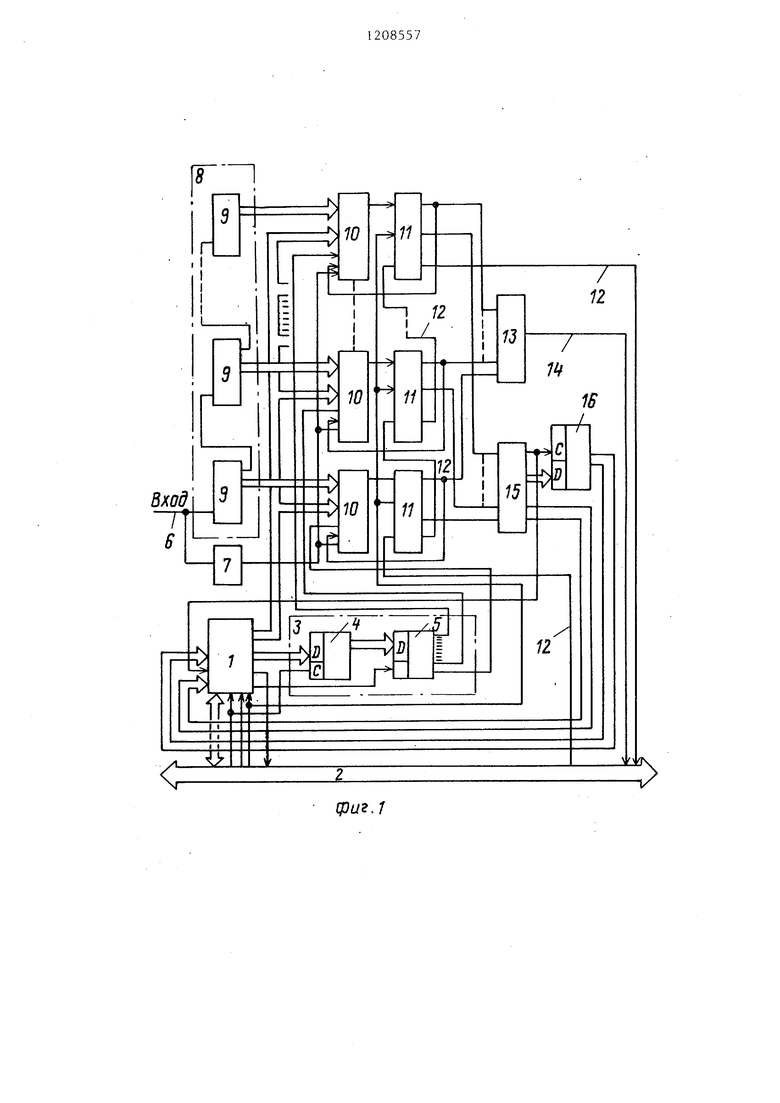

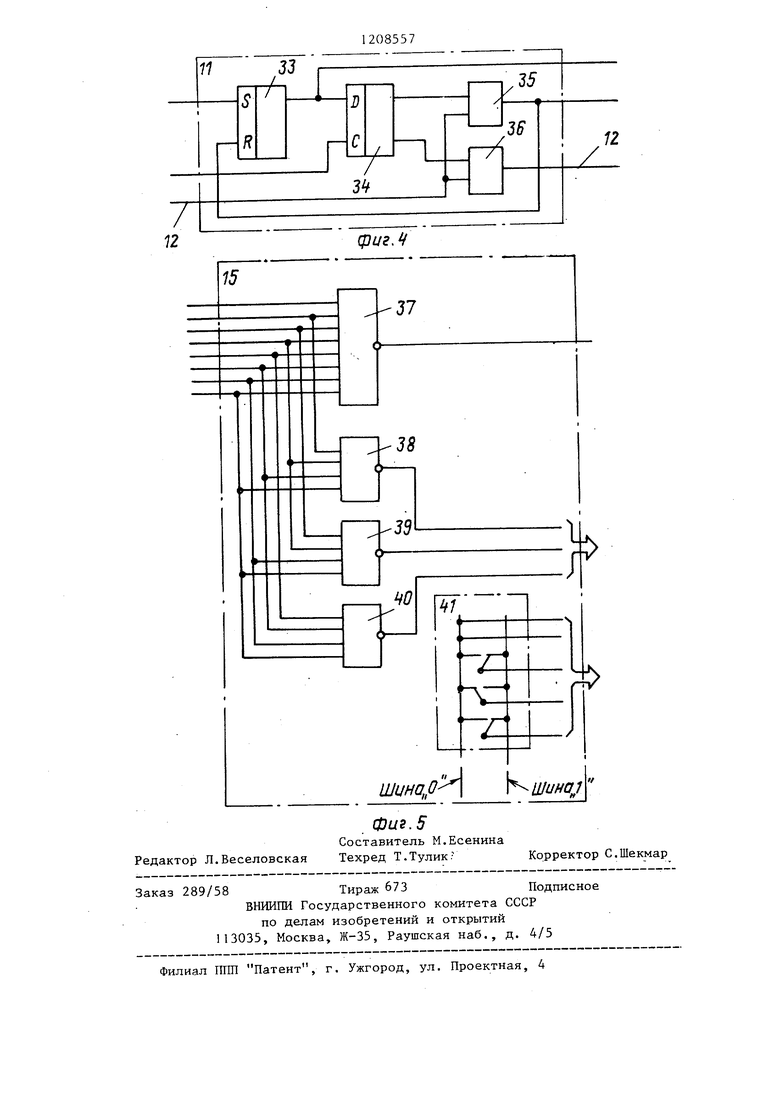

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - принципиальная электрическая схема анализатора сигналов; на фиг. 3 - блок связи с каналом ЭВМ; на фиг. 4 - фор мирователь сигналов прерывания; на фиг. 5 - схема шифратора прерывания .

Устройство для сопряжения ков с ЭВМ (фиг. 1) содержит блок 1 связи с каналом 2 ЭВМ, соединенные между собой, двунаправленной шиной данных адресов, первой, второй и третьей линиями входных синхросигналов блока 1, линией выходного синхросигнала, подключенной к первому синхровыходу блока 1. Группа адресных выходов блока 1 подключена к информационному входу дешифратора 3 адресов, состоящего из первого регистра 4, выполненного на стро бируемых Л-триггерах, и стробиру- еиого дешифратора 5. Стробирующий вход регистра 4 подключен к первому синхровходу блока 1, а выходы его подключены к информационным ходам дешифратора 5, стробирующий вхо которого подключен к второму синхровыходу блока 1. К линии приема дискретной информации 6 подключены вхо блока 7 контроля на четность и вход блока 8 сдвиговых регистров, разделенного на секции сдвиговых регистров 9, соединенных последова.тель- но. Выходы ка5кдого сдвигового регисра 9 подключены к первой группе информационных входов соответствующего анализатора 10 сигналов.

Вторые группы информационных входов анализаторов 10 сигналов соединены между собой и подключены к групе информационных выходов блока 1. Первые управляющие входы ангшизато- ров 10 сигнала подключены к соответствующим выходам дешифратора 5, вторые управляющие входы подключены к первым выходам соответствуюпщх фор- мирователер 1 1 сигналов прерывания, третьи управляющие входы соединены между собой и подключены к выходу

. 10

15

20

25

2085572

блока 7 контроля на четность. Выходы i анализаторов 10 сигнала подключены к первым входам соответствующих формирователей 11 сигнала прерывания, с вторые входы которых соединены между собой и подключены к третьему синхровходу блока , а третьи входы подключены к последовательно проходящей через формирователь 11 сигналов прерывания линии 12 предоставления прерывания.

Первые выходы формирователей 11 сигналов прерывания подключены к входам элемента ИЛИ 13, выход которого подключен к линии 14 требования нрерывания канала 2 ЭВМ. Вторые выходы формирователей 11 сигналов прерывания подключены к входам шифратора 15, управ.тяющий выход которого подключен к управляющему входу блока 1 и тактирующему входу буферного регистра 16 памяти, информационные входы которого подключены к первой группе информационных выходов шифратора 15, а выходы - к первой группе информационных входов блока 1, вторая группа информационных входов которого подключена к второй группе информационных выходов шифратора 15.

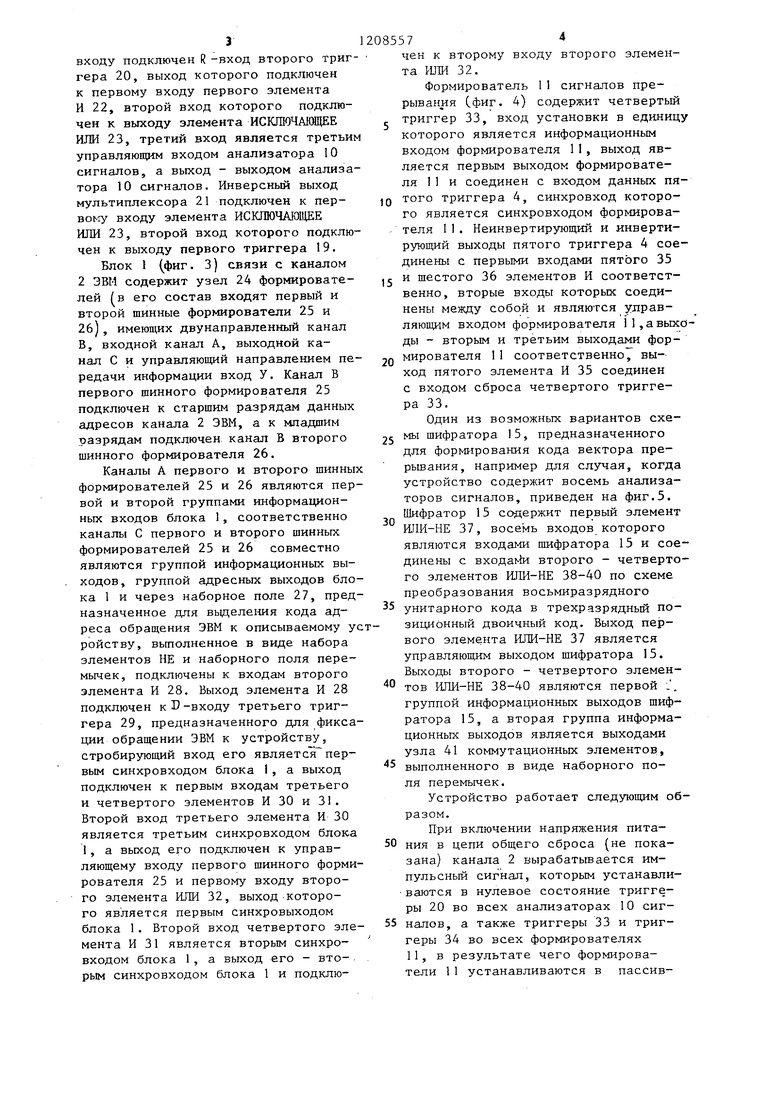

Анализатор 10 сигналов (фиг. 2), предназначенный для контроля уровня сигнала одного из группы сигналов датчика, принимаемых соответствующим сдвиговым регистром 9, содержит узел памяти 17, в состав которого входят второй регистр 18 для выбора номера сигнала, первый триггер 19 для настройки на ожидаемый уровень сигнала и второй триггер 20 построенный на базе Б-триггеров. Выходы второго регистра 18 подключены к адресным входам мультиплексора 21, в качестве которого может быть применен один из стандартных мультиплексоров, например микросхема типа К 155 КП 7. Информационные входы мультиплексора 21 образуют первую группу информационных входов анализатора 10 с 1гнала, а вторую

руппу образуют информационные входы второго регистра 18 совместно с D-входами первого и второго триггеров 19 и 20, Тактирующие входы регистра 18 соединены с тактируюш 1- ми входами первого и второго триггеров 19 и 20 и подключены к первому управляющему входу анализатора 10 сигнала, к второму управляющему

30

35

40

50 „,

55

входу подключен R-вход второго триг гера 20, выход которого подключен к первому входу первого элемента И 22, второй вход которого подключен к выходу элемента ИСКЛЮЧАКЩЕЕ ИЛИ 23, третий вход является третьи управляющим входом анализатора 10 сигналов, а выход - выходом анализатора 10 сигналов. Инверсный выход мультиплексора 21 подключен к пер- BObiy входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23, второй вход которого подключен к выходу первого триггера 19.

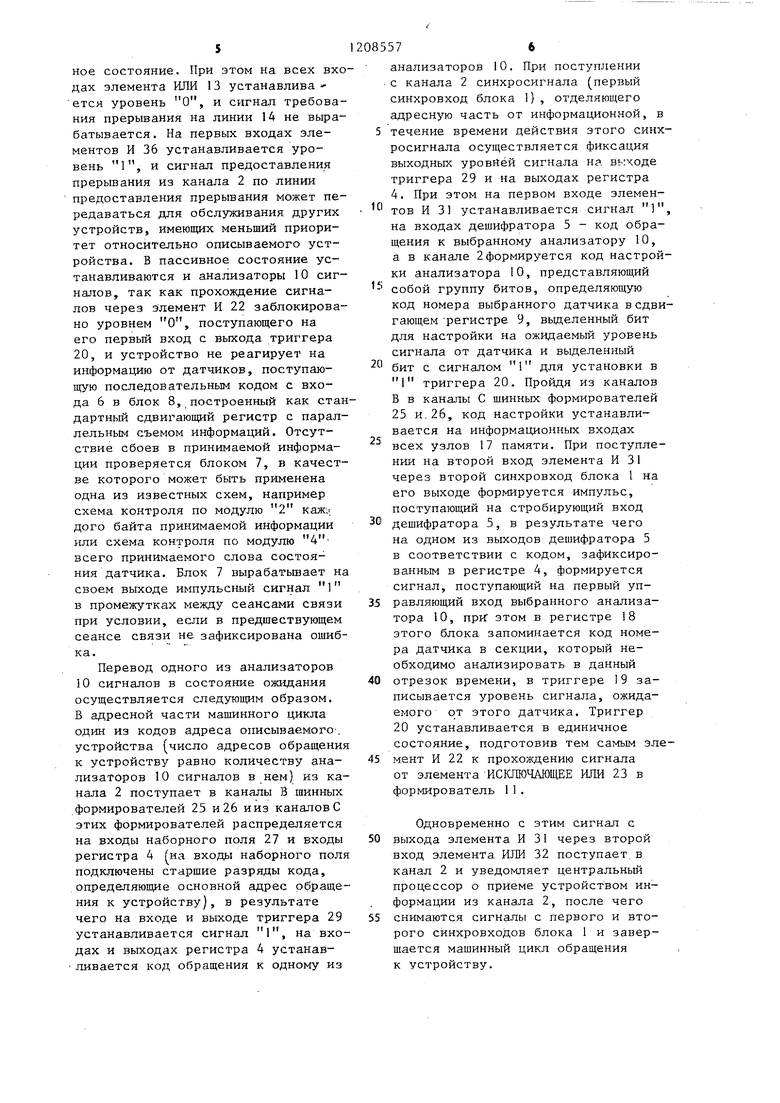

Блок I (фиг. 3) связи с каналом 2 ЭВМ содержит узел 24 формирователей IB его состав входят первый и второй шинные формирователи 25 и 26), имеющих двунаправленный канал В, входной канал А, выходной канал С и управляющий направлением передачи информации вход У. Канал В первого шинного формирователя 25 подключен к старшим разрядам данных адресов канала 2 ЭВМ, а к младшим разрядам подключен канал В второго шинного формирователя 26.

Каналы А первого и второго шинны формирователей 25 и 26 являются первой и второй группами информационных входов блока 1, соответственно каналы С первого и второго шинных формирователей 25 и 26 совместно являются группой информационных выходов, группой адресных выходов блока 1 и через наборное поле 27, предназначенное для выделения кода адреса обращения ЭВМ к описываемому уройству, выполненное в виде набора элементов НЕ и наборного поля перемычек, подключены к входам второго элемента И 28. Выход элемента И 28 подключен к Л-входу третьего триггера 29, предназначенного для фиксации обращении ЭВМ к устройству, стробирующий вход его является первым синхровходом блока 1, а выход подключен к первым входам третьего и четвертого элементов И 30 и 31. Второй вход третьего элемента И 30 является третьим синхровходом блока 1, а выход его подключен к управляющему входу первого шинного формирователя 25 и первому входу второго элемента Ш1И 32, выход-которого является первым синхровыходом блока 1. Второй вход четвертого элемента И 31 является вторым синхровходом блока 1, а выход его - вторым синхровходом блока 1 и подключен к второму входу второго элемента 1-ШИ 32.

Формирователь 11 сигналов прерывания (фиг. 4) содержит четвертый триггер 33, вход установки в единицу которого является информационным входом формирователя 1i, выход является первым выходом формирователя 1 1 и соединен с входом данных пятого триггера 4, синхровход которого является синхровходом формирователя 11. Неинвертирующий и инвертирующий выходы пятого триггера 4 соединены с первыми входами пятого 35

и шестого 36 элементов И соответственно, вторые входы которых соединены между собой и являются управляющим входом формирователя 11, а выходы - вторым и третьим выходами формирователя 11 соответственно, выход пятого элемента И 35 соединен с входом сброса четвертого триггера 33.

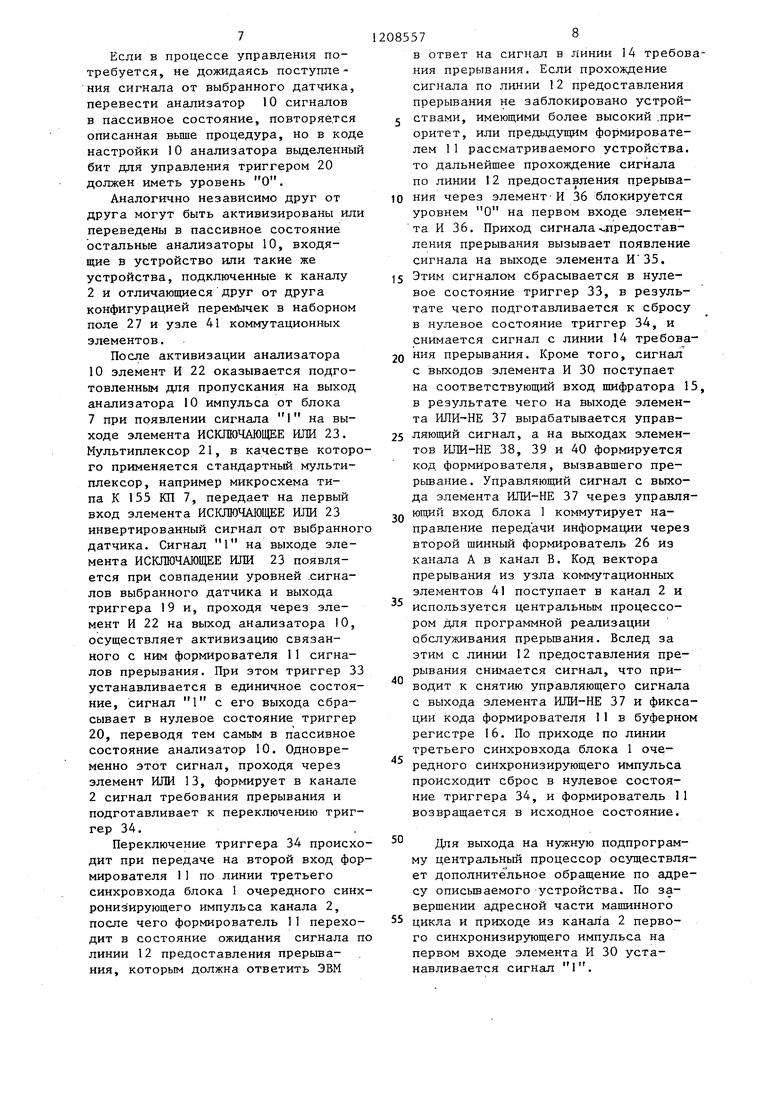

Один из возможных вариантов схемы шифратора 15, предназначенного для формирования кода вектора прерывания, например для случая, когда устройство содержит восемь анализаторов сигналов, приведен на фиг.5. Шифратор 15 содержит первый элемент ШШ-НЕ 37, восемь входов которого являются входами шифратора 15 и соединены с входа второго - четвертого элементов ШШ-НЕ 38-40 по схеме преобразования восьмиразрядного

унитарного кода в трехразрядный позиционный двоичный код. Выход первого элемента ИЛИ-НЕ 37 является управляющим выходом шифратора 15. Выходы второго - четвертого элементов ИЛИ-НЕ 38-40 являются первой . группой информационных выходов шифратора 15, а вторая группа информационных выходов является выходами узла 41 коммутационных элементов,

выполненного в виде наборного поля перемычек.

Устройство работает следующим образом.

При включении напряжения питания в цепи общего сброса (не показана) канала 2 вырабатывается импульсный сигнал, которым устанавли- ваются в нулевое состояние триггеры 20 во всех анализаторах 10 сигналов, а также триггеры 33 и триггеры 34 во всех формирователях 11, в результате чего формирователи 11 устанавливаются в пассив

Ное состояние. При этом на всех вхо дах элемента ИЛИ 13 устанавливав ется уровень О, и сигнал требования прерывания на линии 14 не вырабатывается . На первых входах элементов И 36 устанавливается уровень Г

и сигнал предоставления

прерывания из канала 2 по линии предоставления прерывания может передаваться для обслуживания других устройств, имеющих меньший приоритет относительно описываемого устройства. В пассивное состояние устанавливаются и анализаторы 10 сигналов, так как прохождение сигналов через элемент И 22 заблокировано уровнем О, поступающего на его первый вход с выхода триггера 20, и устройство не реагирует на информацию от датчиков, поступающую последовательным кодом с входа 6 в блок 8, построенный как стан дартный сдвигающий регистр с параллельным съемом информации. Отсутствие сбоев в принимаемой информации проверяется блоком 7, в качестве которого может быть применена одна из известных схем, например схема контроля по модулю 2 каж; дого байта принимаемой информации или схема контроля по модулю всего принимаемого слова состояния датчика. Блок 7 вырабатьшает на своем выходе импульсный сигнал 1 в промежутках между сеансами связи при условии, если в предшествующем сеансе связи не зафиксирована ошибка.

Перевод одного из анализаторов 10 сигналов в состояние ожидания осуществляется следующим образом. В адресной части машинного цикла один из кодов адреса описываемого-, устройства (число адресов обращения к устройству равно количеству анализаторов 10 сигналов в нем) из канала 2 поступает в каналы В шинных формирователей 25 и 26 ииз каналов С этих формирователей распределяется на входы наборного поля 27 и входы регистра 4 (на входы наборного поля подключены старшие разряды кода, определяющие основной адрес обращения к устройству), в результате чего на входе и выходе триггера 29 устанавливается сигнал 1, на входах и выходах регистра 4 устанавливается код обращения к одному из

2085576

анализаторов 10. При поступлении с канала 2 синхросигнала (первый синхровход блока 1), отделяющего адресную часть от информационной, в 5 течение времени действия этого синхросигнала осуществляется фиксация выходных уровней сигнала на выходе триггера 29 и на выходах регистра 4. При этом на первом входе элемен- тов И 31 устанавливается сигнал 1, на входах дешифратора 5 - код обращения к выбранному анализатору 10, а в канале 2 формируется код настройки анализатора Ю, представляющий - собой группу битов, определяющую

код номера выбранного датчика в сдвигающем регистре 9, выделенный бит для настройки на ожидаемый уровень сигнала от датчика и выделенный

бит с сигналом 1 для установки в 1 триггера 20. Пройдя из каналов В в каналы С шинных формирователей 25 и.26, код настройки устанавливается на информационных входах всех узлов 17 памяти. При поступлении на второй вход элемента И 31 через второй синхровход блока 1 на его выходе формируется импульс, поступающий на стробирующий вход

дешифратора 5, в результате чего на одном из выходов дешифратора 5 в соответствии с кодом, зафиксированным в регистре 4, формируется сигнал, поступающий на первый уп35 равляющий вход выбранного анализатора 10, прк этом в регистре 8 этого блока запоминается код номера датчика в секции, который необходимо анализировать в данный

40 отрезок времени, в триггере 19 записывается уровень сигнала, ожидаемого от этого датчика. Триггер 20 устанавливается в единичное состояние, подготовив тем самым эле45 мент И 22 к прохождению сигнала от элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 в формирователь 11.

Одновременно с этим сигнал с 50 выхода элемента И 31 через второй вход элемента ИЛИ 32 поступает.в канал 2 и уведомляет центральньш процессор о приеме устройством информации из канала 2, после чего 55 снимаются сигналы с первого и второго синхровходов блока 1 и завершается машинный цикл обращения к устройству.

7

Если в процессе управления потребуется, не дожидаясь поступления сигнала от выбранного датчика, перевести анализатор 10 сигналов в пассивное состояние, повторяется описанная вьше процедура, но в код настройки 10 анализатора выделенны бит для управления триггером 20 должен иметь уровень О.

Аналогично независимо друг от друга могут быть активизированы ил переведены в пассивное состояние остальные анализаторы 10, входящие в устройство или такие же устройства, подключенные к каналу 2 и отличающиеся друг от ДРУга конфигурацией перемЬгчек в наборном поле 27 и узле 41 коммутационных элементов.

После активизации анализатора 10 элемент И 22 оказывается подготовленным для пропускания на выход анализатора 10 импульса от блока 7 при появлении сигнала 1 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23. Мультиплексор 21, в качестве которого применяется стандартный мультиплексор , например микросхема типа К 155 КП 7, передает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 инвертированный сигнал от выбранног датчика. Сигнал 1 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 появляется при совпадении уровней .сигналов выбранного датчика и выхода триггера 19 и, проходя через элемент И 22 на выход анализатора 10, осуществляет активизацию связанного с ним формирователя 11 сигналов прерывания. При этом триггер 33 устанавливается в единичное состояние, сигнал 1 с его выхода сбрасывает в нулевое состояние триггер 20, переводя тем самым в пассивное состояние анализатор 10. Одновременно этот сигнал, проходя через элемент ИЛИ 13, формирует в канале 2 сигнал требования прерывания и подготавливает к переключению триггер 34.

Переключение триггера 34 происходит при передаче на второй вход формирователя 11 по линии третьего синхровхода блока 1 очередного синхронизирующего импульса канала 2, после чего формирователь 11 переходит в состояние ожидания сигнала п линии 12 предоставления прерьша- ния, которым должна ответить ЭВМ

08557о

в ответ на сигнал в линии 14 требования прерывания. Если прохождение сигнала по линии 12 предоставления прерывания не заблокировано устрой5 ствами, имеющими более высокий .приоритет, или предыдущим формирователем 11 рассматриваемого устройства, то дальнейшее прохождение сигнала по линии 12 предоставления прерыва10 ния через элемент И 36 блокируется уровнем О на первом входе элемента И 36. Приход сигнала-.предоставления прерывания вызывает появление сигнала на выходе элемента ,

)5 Этим сигналом сбрасывается в нулевое состояние триггер 33, в результате чего подготавливается к сбросу в нулевое состояние триггер 34, и снимается сигнал с линии 14 требова20 ния прерывания. Кроме того, сигнал с выходов элемента И 30 поступает на соответствующий вход пшфратора 15, в результате чего на выходе элемента ИЛИ- НЕ 37 вырабатывается управ25 ляющий сигнал, а на выходах элементов ИЛИ-НЕ 38, 39 и 40 формируется код формирователя, вызвавшего пре- рьтание. Управляющий сигнал с выхода элемента ИЛИ-НЕ 37 через управля2Q ющий вход блока 1 коммутирует направление передачи информации через второй шинный формирователь 26 из канала А в канал В. Код вектора прерывания из узла коммутационных элементов 41 поступает в канал 2 и используется центральным процессором для программной реализации обслуживания прерьшания. Вслед за этим с линии 12 предоставления прерывания снимается сигнал, что приводит к снятию управляющего сигнала с выхода элемента ИЛИ-НЕ 37 и фиксации кода формирователя 11 в буферном регистре 16. По приходе по линии третьего синхровхода блока 1 очередного синхронизирующего импульса происходит сброс в нулевое состояние триггера 34, и формирователь 11 возвращается в исходное состояние.

Для выхода на нужную подпрограмму центральный процессор осуществляет дополнительное обращение по адресу описьшаемого устройства. По завершении адресной части машинного

55 цикла и приходе из канала 2 первого синхронизирующего импульса на первом входе элемента И 30 устанавливается сигнал I.

35

40

45

При поступлении на второй вход элемента И 30 сигнал синхронизации ввода информации в канал 2 через третий синхровход блока 1 на его выходе вырабатьшается сигнал, который через управляющий вход первого шинного формирователя 25 коммутирует направление передачи информации в нем из канала А в канал В. Код формирователя I1, последним вызвавший прерывание, из буферного регистра 16 памяти передается в канал 2. Вместе с тем выходной сигнал элемента И 30 через первый вход элемента ИЛИ 32 передается в канал 2, информируя Центральный процессор о вьщаче кода из устройства в канал 2, Центральный процессор принимает код и завершает машинный цикл обращения к предлагаемому устройству снятием синхронизирующих сигналов с первого и третьего синхровходов блока 1.

Формула изобретени

1. Устройство для сопряжения датчиков с ЭВМ по авт.св. № 1129600 отличающееся тем, что, с целью увеличения допустимого количества сопрягаемых с ЭВМ датчиков, устройство содержит буферный регистр, информационные входы и вхо синхронизации которого подключены соответственно к дополнительным информационным выходам и к управляющему выходу шифратора, выходы буферного регистра подключены к третьему информационному входу блока связи с каналом, третий синхровход которого является третьим синхровхо дом устройства.

208557

2. Устройство по п. 1, отличающееся тем, ЧТ9 блок связи с каналом содержит два шинных формирователя, наборное поле, вто5 рой, третий и четвертый элементы И, третий триггер, второй элемент ИЛИ, информационные входы второй группы шинных формирователей являются вторым информационным входом блока свя- 10 зи, информационные входы первой груп пы первого и второго шинных формирователей являются соответственно первым и третьим информационными «ходами блока связи, выходы первого

15 и второго шинных формирователей являются соответственно информационными выходами первой и второй групп блока связи, выходы первого шинного формирователя соединены с входами

20 наборного поля, выходы которого соединены с входами второго элемента И, выход которого соединен с 1 -входом третьего триггера, синхровход которого является первым синх25 ровходом блока связи, первые входы третьего и четвертого элементов И объединены между собой и подключены к выходу третьего триггера, вторые входы третьего и четвертого элемен30 тов И являются соответственно вторым и третьим синхровходами блока связи, выход третьего элемента И соединен с управляющим входом вто- рого шинного формирователя, выход четвертого элемента И является вторым синхровыходом блока связи и соединен с вторым элементом ИЛИ, выход которого является первым синхровыходом блока связи, управляющий вход первого шинного форми35

40

рователя является управляющим входом блока связи.

фиг.Г

гС

А(

ЦЗиг.З

12

фиг,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1985 |

|

SU1282108A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1302281A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к вычислительной технике, предназначено для группового управления манипуляторами и монтажно-сборочнь1м оборудованием в системах реального масштаба времени. Целью изобретения является увеличение количества управляемых, от ЭВМ датчиков. Изобретение является дополнительным к авторскому свидетельству СССР № 1129600. Цель изобретения достигается за счет введения в устройство для сопряжения датчиков с ЭВМ буферного регистра и соответствующих связей. 2 з.п. ф-лы, 5 ил. кэ о 00 СП ел

-J5

40

W

-Г.

л:

.

Редактор Л.Веселовская

фиг. 5

Составитель М.Есенина

Техред Т.Тулик.- Корректор С.Шекмар

Заказ 289/58Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ГШП Патент, г. Ужгород, ул. Проектная, 4

ШиноЛ

,И

Шинот

| Устройство для сопряжения датчиков с ЭВМ | 1983 |

|

SU1129600A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-30—Публикация

1984-07-17—Подача