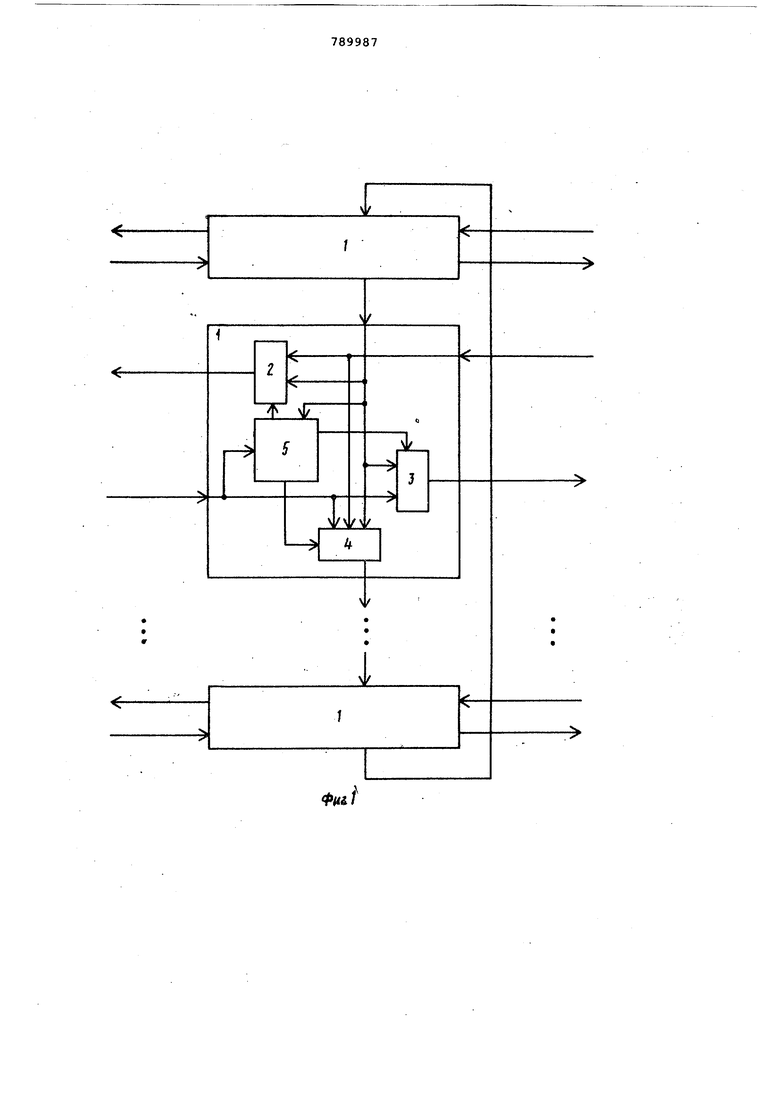

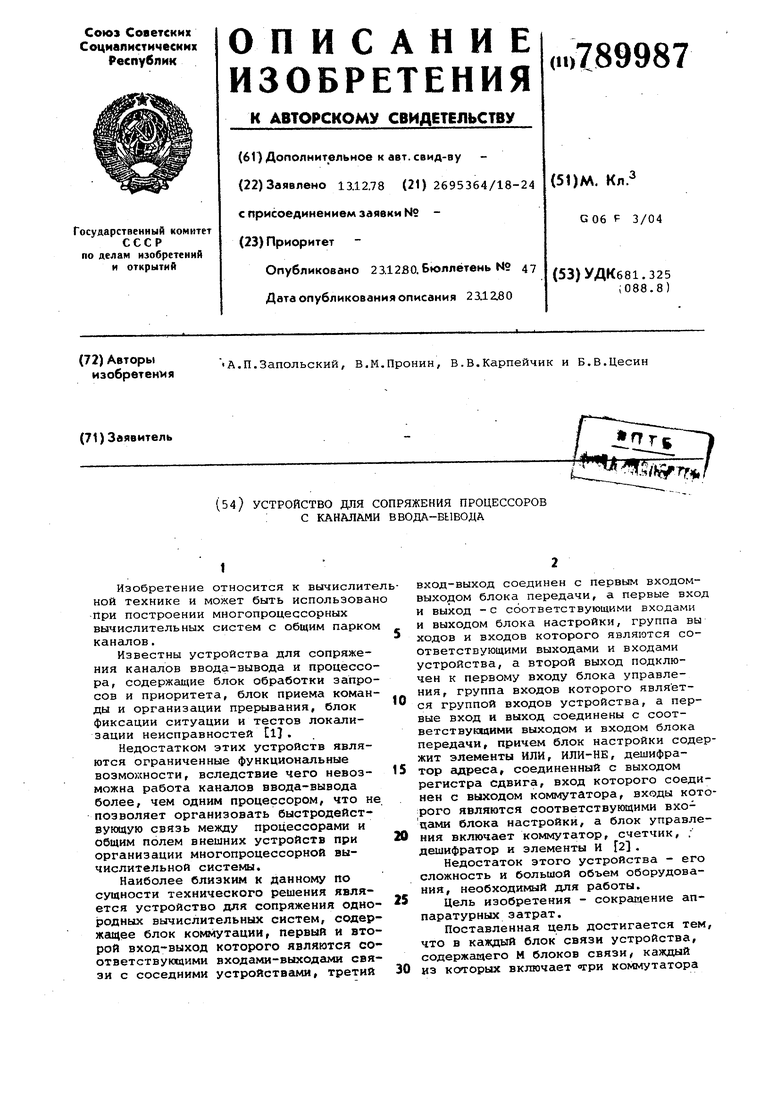

Изобретение относится к вычислите ной технике и может быть использован при построении многопроцессорных вычислительных систем с общим парком канёшов. Известны устройства для сопряжения каналов ввода-вывода и процессора, содержащие блок обработки запросов и приоритета, блок приема команды и организации прерывания, блок фиксации ситуации и тестов локализации неисправностей 1. Недостатком этих устройств являются ограниченные функциональные воэмохсности, вследствие чего невозможна работа каналов ввода-вывода более, чем одним процессором, что не позволяет организовать быстродействующую связь между процессорами и общим полем внешних устройств при организации многопроцессорной вычислительной системы. Наиболее близким к данному по сущности технического решения является устройство для сопряжения однородных вычислительных систем, содержащее блок коммутации, первый и второй вход-выход которого являются соответствующими входами-выходами связи с соседними устройствами, третий вход-выход соединен с первым входомвыходом блока передачи, а первые вход и выход - с соответствующими входами и выходом блока настройки, группа вы ходов и входов которого являются соответствующими выходами и входами устройства, а второй выход подключен к первому входу блока управления, группа входов которого является группой входов устройства, а первые вход и выход соединены с соответствующими выходом и входом блока передачи, причем блок настройки содержит элементы ИЛИ, ИЛИ-НЕ, дешифратор адреса, соединенный с выходом регистра сдвига, вход которого соединен с выходом коммутатора, входы которого являются соответствующими вхоцами блока настройки, а блок управления включает коммутатор, счетчик, ; дешифратор и элементы И 2 . Недостаток этого устройства - его сложность и большой объем оборудования, необходимый для работы. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что в каждый блок связи устройства, содержащего М блоков связи/ каждый из которых включает три коммутатора и дешифратор режима, введены триггер режима, шифратор адреса и регистр, причем первый вход и выход первого коммутатора являются соответственно первым входом и вторым выходом блока связи,выход второго коммутатора я ляется первым выходом блока связи,пе вый вход соединен со вторым входом блока связи, первыми входами шифратора адреса и третьего коммутатора и входом дешифратора режима, выходом подключенного ко входу триггера, выходы которого соединены соответственно со вторым и третьим входами ши ратора адреса, выходом подключенного ко входу регистра, выходыкоторого соединены соответственно со вторыми входами коммутаторов, третьи выходы которых подключены.к третьему входу блока связи и четвертому входу шифратора адреса, четвертый вход и выхо третьего коммутатора соединени соответственно с первым входом и третьим выходом блока связи,первые и вторые входы и выходы которого являются COO ветствующими входами и выходами устройства, третий выход i-го блока связи соединен с третьем входом i + + 1-го блока связи, третий выход М-г блока связи соединен с третьим входом первого блока связи / 1 М/. На фиг. 1 приведена структурная схема устройства; на фиг, 2 - функциональная схема узла местного управ ления. Устройство содержит блоки 1 связи каждый из которых включает три коммутатора 2,3,4 и узел 5 местного управления, содержащий четырехразряд ный регистр 6, шифратор 7 адреса, де шифратор 8 режима и триггер 9 режима. Блок 1 связи предназначен для связи процессора с группами каналов ввода-вывода , узел 5 местного управ ления - для управления коммутаторами Первые вход и выход каждого блока 1 связи подключаются соответственно к выходным и входным шинам одной группы каналов ввода-вывода, а вторые вход и выход - соответственно к выходной и входной шине однбго из процессоров. Регистр 6 предназначен для фиксации состояния коммутаторов 2,3,4 блока1 связи, шифратор 7 служит для формирования адреса направл ния потока информации между процессо рами и группами каналов под управлением любого процессора. Дешифратор 8 предназначен для опознания адреса, поступающего из процессора,непосредственно не соединенного с данным бло ком 1 связи, с номером процессора, соединенного с этим же блоком 1 связ Устройство работает следующим образом. Возможны 3 режима работы устройст ва. 1. Обмен процессора ссоответству ющей ему групйой каналов. При этом триггер 9 сброшен, что обеспечивает занесение через шифратор 7 кода, который устанавливает второй и четвертый и сбрасывает первый и третий разряды регистра 6. Через коммутатор 2 осуществляется передача информации из группы каналов на первые входы блока вязи и далее на входную шину процессора, а через коммутатор 3- переда.ча информации из процессора на второй вход блока связи и далее на входную шину группы каналов,а также возможна передача информации с третьего выхода предыдушего блока 1 связи через коммутатор 4 на третий вход последующего блока 1 связи. 2. Обмен между процессором и группой каналов ввода-вывода, подключенной к блоку 1 связи другого процессора. Для переключения в такой режим работы управляющая системная программа, если ни один из процессоров системы не обменивается информацией с группой каналов ввода-вывода, подключенных к блоку 1 связи другого процессора, а также если нужная группа канад ов не занята обменом информацией с соответствующим процессором, вьщает команду одному из процессоров осуществить переключения в своем блоке 1 связи, а также в блоке 1 связи, к которому подключена нужная группа каналов . Для этого получивший команду процессор в связанном с ним блоке 1 связи устанавливает первый и сбрасывает второй, третий и четвертый разряды регистра 6. Таким образом становится возможной передача информации с третьего выхода предыдущего блока связи через коммутатор 2 на входную шину процессора и передача с выходной шины процессора через коммутатор 4 на третий вход последукицего блока связи. Все остальные блоки ; 1 связи в этот момент находятся в состоянии, определяемом п. 1. Далее получивший команду процессор вьщает адрес требуемой группы каналов, ко-) торый последовательно проходит через коммутаторы 4 каждого блока 1 связи и анализируется дешифраторами 8 каждого из блоков 1 связи. Дешифратор 8, опознавший свой адрес, вьвдает сигнал, устанавливающий триггер 9, тем самым позволяя управлять установкой регистра 6 через шифратор 7 процессору, выдавшему адрес. Затем этот процессор вьадает сигналы, которые, последовательно проходя через блоки 1 связи, устанавливают третий разряд и сбрасывают первый, второй и четвертый разряды регистра б в выбранном блоке 1 связи. При этом становится -i возможной связь между выходной шиной группы каналов через коммутатор 4 с третьим входом последующего блока 1 связи, а также свяйь между третьим выходом предыдущего блока 1 связи через коммутатор 3 со входной шиной

группы каналов. После окончания обмена процессор, управляющий обменрм, переводит блоки 1 связи в исходное состояние, определенное в п. 1 ч обратном порядке.

3. При выходе-из строя одного из процессоров системы управляющая системная программа выдает команду любо у исправному процессору осуществить отключение-неисправного процессора от системы ввода-вывода. Процессор, получивший команду, производит в связанном с ним блоке 1 связи переключения, описанные в п. 2, и выдает через коммутатор 4 адрес требуемой группы каналов, который анализируется дешифраторами 8 каждого из блоков 1, Дешифратор 8, опознавший свой адрес, выдает сигнал, устанавливакмций триггер 9, позволяя управлять установкой регистра б через шифратор 7 процессору, выдавшему адрес. Затем этот процессор выдает сигналы, которые, последовательно проходя через блоки 1 связи, устанавливают четвертый разряд и сбрасывают остальные разряды регистра б в выбранном блоке 1 связи. При этом процессор, связанный с выбранным блоком 1 связи, отключается от работы с каналами, и остаетсявозможной передача информации с третьего выхода предыдущего блока 1 связи через коммутатор 4 на третий вход последующего за выбранным блока 1 связи. Установление связи между группой каналов, соответствующих неисправномупроцессору, с любым процессором для обмена информацией производится аналогично описанному в п. 2. После восстановления неисправного процессора он подключается к системе ввода-вывода в порядке, обратном его отключе нию.

Таким образом, предлагаемое устройство по сравнению с известным имеет меньший объем оборудования при использовании в системах с переменным числом процессоров за счет исключения в известном устройстве общего для всех каналов оборудования, которое проектируется с учетом подключения максимсьльного числа процессоров. Кроме того увеличена пропускная способность системы ввода-вывода за счет введения отдельных обменных магистралей между процессорами и принадлежащими им группгими кангилов ввода-вывода через соответствующие блоки связи, при этом обмен любого из процессоров с не принсодлежсцдей ему группой каналов обеспечивается через односторои.нюю магитраль, связывающую блоки свя:ЗИ.

Формула изобретения

Устройство для сопряжения процессоров с каналами ввода-вывода содер0жащее м блоков связи, каждый из которых включает три коммутатора и дешифратор режима, отличающеес я тем, что, с целью сокращения аппаратурных затрат, в каждый блок вве5дены триггер режима, шифратор адреса и регистр, причем первый вход и выход первого коммутатора являются соответственно первым входом и вторым выходом блока связи, выход второго коммутато0ра является первым выходом блока связи, .первый вход соединен со вторым входом блока связи, первыми входами шифратора сщреса и третье -о коммутатора и входом дешифратора режи5ма, выходом подключенного ко входу триггера, выходы которого соединены соответственно со вторым и третьим входами шифратора адреса, выходом подключенного ко входу регистра, вы0ходы которого соединены соответственно со вторыми входами коммутаторов, третьи выходы которых подключены к третьему входу блока связи и четвертому входу шифратора адреса, четвертый вход и выход третьего коммутато5ра соединены соответственно с первым входом и третьим выходом блока связи, п.ервые и вторые входы и выходы которого являются соответствующими входами и выходами устройства, третий вы0ход « -го блока связи соединен с третьим входом с 1 + 1-го блока связи, третий выход М-го блока связи соединен с третьим входом первого блока связи /i 1, М/.

5

Источники информации, принятые во внимание при экспертизе

1,Вопросы радиоэлектроники, сер. ЭВТ, вып. 1, 1973.

0

2.Авторское свидетельство СССР ,по заявке 2688967/18-24,

кл. G,06 Р 3/04, 21.11.28 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

J

€- е

4,,Ji,

Авторы

Даты

1980-12-23—Публикация

1978-12-13—Подача