1

Изобретение относится к автоматической измерительной технике, а .именно, к анализаторам амплитуд, iслучайных импульсных исследовательностей с различной длительностью импульсов.

Известно устройство, содержащее фильтр нижних частот, пороговый элемент, ищущий мультивибратор, триггер памяти, дешифратор, схему вьаделения заднего фронта l Недостатком этого устройства является недостаточная разрешающая способность, так как преобразователь не различает частично наложенных друг на друга импульсов

Известен также анализатор амплитуд импульсов, содержащий m по числу каналов пороговых элементов,mDтриггеров, дешифратор, триггер управления, формирователь заднегофронта, элемент НЕ, входные шины соединены со входами гп пороговых элементов, выходы которых соединены с Dвходами соответствующих D-триггеров, выходы которых соединены с сигнальными входами дешифратора, а выход триггера управления через формирователь заднего фронта; соединен со входом управления дешифратора, в.ыходами подключенного к выходным шйнам 2.

Недостатком этого устройства также является недостаточная разрешающая способность.

Цель изобретения - повышение разрешающей способности, заключающееся в реализации разделения во времени импульсов различной длительности с

10 произвольной крутизной фронтов, частично наложенных друг на друга, уровень сигнала между соседними максимумами которых лежит в диапазоне от О до порога, превышенного перед

15 этим первым максимумом.

Указанная цель достигается тем, что в анализатор амплитуд импульсов, содержащий группу из m по числу каналов пороговых элементов,тО-триггеров,

20 дешифратор, триггер управления,

формирователь заднего фронта, элемент НЕ, входные шины соединены со входами m пороговых элементов,выхо- ды которых соединены с 0-входами

25 соответствующих D-триггеров, выходы которых соединены с сигнальными входами дешифратора, а выход триггера управления через формирователь заднего фронта соединен со входом

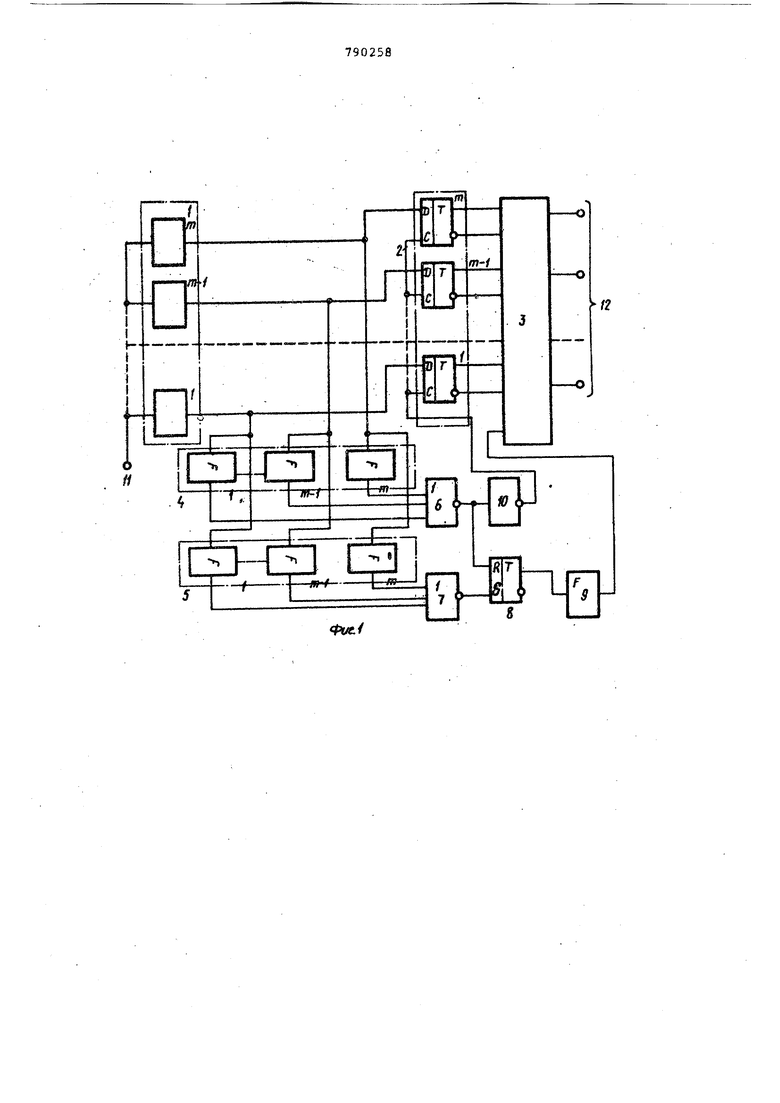

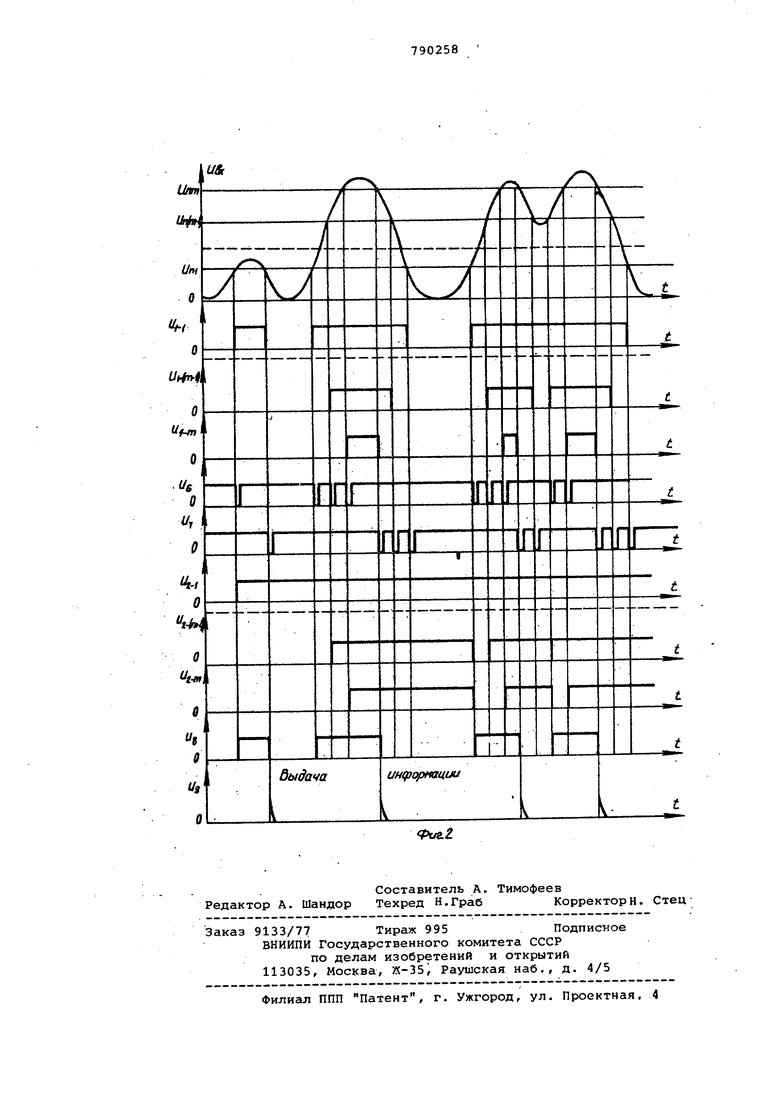

JQ управления дешифратора, выходами подключенного к выходным шинам, вве дены две группы по m формирователей переднего и заднего фронтов и два т входовьвс элемента ИЛИ-НЕ, причем выход каждого пороговогоэлемента соединен со входами соответствующих формирователей переднего и заднего фронтов данного канала, выходы формирователей переднего фронта через первый злемент ИЛИ-НЕ подсоединены ко входу установки в единицу триггера управления и, через элемент НЕ - ко входам синхронизации 0-триг героБ,а выходы формирователей заднего фронта через второй элемент ИЛИ-НЕ подсоединены, ко входу установки в ноль триггера управлений. На Фк:ГЛ изображена блок-схема анализатора амплитуд импульсов; на фиг.2 - временные зависимости основных сигналов анализатора. Анализатор содержит группу из m (по числу каналов) пороговых элементов 1, группу из гаО-триггеров 2,. дешифратор 3, группу из т-формирователей переднего фронта 4, группу из .лрователей заднего фронта 5, первый т-входовой лемент ИЛИ-НЕ 6, второй т-еходовой элемент ИЛИ-НЕ 7, триггер управления 8, формирователь заднего фронта 9, элемент НЕ 10, вход ной зажим анализатора 11, выходные зажикга анализатора 12.В анализаторе входной зажим 11 подключен ко входам Есезс пороговых-элементов 1, выход кзхдоро порогового элемента подключен к D-входу соответствующего триггера 2, а также ко входу соответству ,щего формирователя переднего фронта 4 и форгйирователя заднего фронта 5. Выходы всех D-триггеров 2 под|слючекы к соответствующим входам дёшифрат ра 3, выходы которого подключены к выходным зажимам анализатора 12. Бгйходы всех формирователей переднего фронта 4 подключены ко входам первог элемента ИЛИ-НЕ 6. Выходы всех рователей заднего фронта 5 подключены ко входам второго элемента КЛИЕ Е 7. Выход первого элемента ИЛИ-НЕ б соединен со входом установки в единицу триггера управления 8 и чере элемент НЕ 10 соединен со всеми сиикровходами 0-триггеров 2. Выход вто рого элемента ИЛИ-НЕ 7 подключен к входу установки в нуль триггера управления 8. Прямой выход триггера управления 8 подключен через формирователь заднего фронта 9 ко входу управления дешифратора 3. Элемент НЕ 10 нужен для записи выходных состо ний блоков 1 в триггеры 2 на протяжении времени существования импульсо ка выходах блоков 4. Анализатор амплитуд работает сле д тощим образом. Входной сигнал Ug поступает со Еходных 11 на все пороговые элементы 1. При этом те из них, порог срабатывания УЛК,где К€ 1 ,....1и j которых окажется меньшим амплитуды сигнала и i, и , сработают ( пряжение U. .... U, на фиг.2) и будут находиться в этом состоянии до момента, пока величина и не станет меньше величиныи ц .При и блок 1-k возвратится в исходное состояние. Переходы блоков 1 - 1,...,1-т из исходного в сработавшее состояние и обратно сопровождаются формированием переднего и заднего фронтов, соответственно, с помощью формирователей переднего фронта 4 и заднего фронта 5. Отформированные импульсы с выходов указанных формирователей поступают соответственно на элеГнты 6 и 7, производящие операции . U4-,- « Рассмотрим случай, когда входной сигнал U0J растет. Выходной сигнал блока 6 Ug поступает на единичный вход триггера управления 8 и одновременно через элемент НЕ 10, на С - входы синхронизации всех триггеров 2, на 0-входы которых поступают сигналы и. ... и.|..и выходов блоков 1. Под влиянием указанных сигналов состояния триггеров 2 из юняется,а следовательно, изменится и код на ЕХО де дешифратора 3 . Задний фронт импульса и4 , сбответствуквдий переднему фронту первого же из поступивших импульсов 0 , перебрасывает триггер управления 8 с нулевого в единичное состояние. Обозначим через Т м у логическую единицу на выходе соотвествукицих триггеров триггера управления 8, а через Т., ....,Т , Т - логический нуль на выходе этих триггеров. Обозначим также через А0 процесс выдачи информации с выхода дешифратора. Единица дискретности л и ПК -Uw-1 .Если ,t&,TO работа системы может быть представлена следующим выражениемV Uy .. л т Т, л А в). ел п« ,( в общем случае, если . (состояния системы обозначим, R, (UB«) UBX .л- Т,,АВ). При уменьшении величину, не меньшую & , состояние соответствующих блоков 1 изменится на исходное. Такое изменение состояний приведет к формированию задних фронтов импульсов с помсяаью формирователей 5.

Первый же из отформированных импульсов Uj- .пройдя через блок 7, поступит на S-вход триггера управления 8 и перебросит его в нулевое состояние. Такой переход триггера 8 сопровождается формированием импульса DA блоком 9. Импульс ) д поступает на управляющий вход дешифратора 3, разрешая тем самым преобразование дешифратором выходного кода триггеров 2 и съем преобразованного кода с соответствующих выходных клемм 12. Таким образом, устройство выдает выходной код всякий раз, когда значение Up, становится меньшим величины ближайшего нижнего порога.

Если (it-i ,то в момент появления импульса U-y состояние системы Pj() может быть выражено:

Uв,,...,,,...,л

При дальнейшем уменьшении входного сигнала ниже порогов срабатывания соседних пороговых элементов съем выходного кода не происходит, т.е. если то

V и д Т А , А... А... , Sg) Такие состояния системы обозначим Ъ Ъ )- общем виде состояния системы Q (и вх ) при любой амплитуде импульсов могут быть выражены следующим образом;

Q(Ubx)--P-iCU6 Pa(UB)Ps(Ue)vP(OBx)R2{UBjt(и)Ч Р, (и) Ра{ивк)Рэ (UBX)

Следовательно, дополнительная установка в анализаторе двух групп по т-формирователей переднего и заднего фронтов и т-входовых элементов ИЛИ-НЕ позволило повысить временную разрешающую способность анализатора, вследствие чего стало возможным производить разделение во времени частично наложенных друг на друга импульсов с произвольной крутизной фронтов, уровень сигнала между соседними максимумами которых лежит в диапазоне от О до порога, превышенного перед этим первым максимумом.

5

Формула изобретения

Анализатор амплитуд импульсов,содержащий m по числу каналов пороговых элементов, тО-триггеров, дешифратор, триггер управления, формирователь заднего фронта,элемент НЕ,входные шины соединены со входами т пороговых элементов , выходы которых соединены с 0-входами соответствующих

D-триггеров, выкоды которых соединены с сигнальнЕЛМи входами дешифратора, а выход триггера управления через формирователь заднего фронта соединен со входом управления дешифратора, выходами подключенного к

выходным шинам, отличающийс я тем, что, с целью повышения разрешающей способности, в него введены две группы по т-формирователей переднего и заднего фронтов и два т-входовых элемента ИЛИ-НЕ, причем выход каждого порогового элемента соединен со входами соответствующих формирователей переднего и заднего фронтов данного канала,выходы формирователей

переднего фронта через первый элемент ИЛИ-НЕ подсоединены ко входу установки в единицу управлянвдего триггера и,через элемент НЕ - ко входам синхронизации 0-триггеров, а выходы формироватёлей заднего фронта через второй элемент ИЛИ-НЕ подсоединены ко входу установки в ноль триггера управления.

Источники информации,

принятые во внимание при экспертизе

1.Сб .статей Львовского политехнического ин-та Доклады и научные сообщения, № 8,1977, с. 109-112.

2.Сборник статей Геофизическая аппаратура, вьш.65,Л., Недра,

1978рС.116-120 (прототип).

«Йл/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования параметров потоков частиц | 1981 |

|

SU1080096A1 |

| Амплитудно-временной анализатор | 1983 |

|

SU1257826A1 |

| Статистический анализатор | 1980 |

|

SU896642A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1522406A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Коммутатор | 1980 |

|

SU869032A1 |

| Дискретный амплитудный анализатор | 1977 |

|

SU699668A1 |

| Устройство для функционального контроля логических элементов | 1984 |

|

SU1226468A1 |

| Амплитудно-временной анализатор | 1990 |

|

SU1746523A1 |

| Устройство для передачи и приема двоичной информации | 1989 |

|

SU1688439A1 |

Авторы

Даты

1980-12-23—Публикация

1978-06-15—Подача