Изобретение относится к вычислительной технике и может быть исноль- эовано для контроля логических элементов, в том числе интегралышх микросхем и печатных нлат с логическими элементами.

Целью изобретения является унро-- щение устройства за счет устранения: необходимости в индивидуальных коммутаторах-преобразователях .

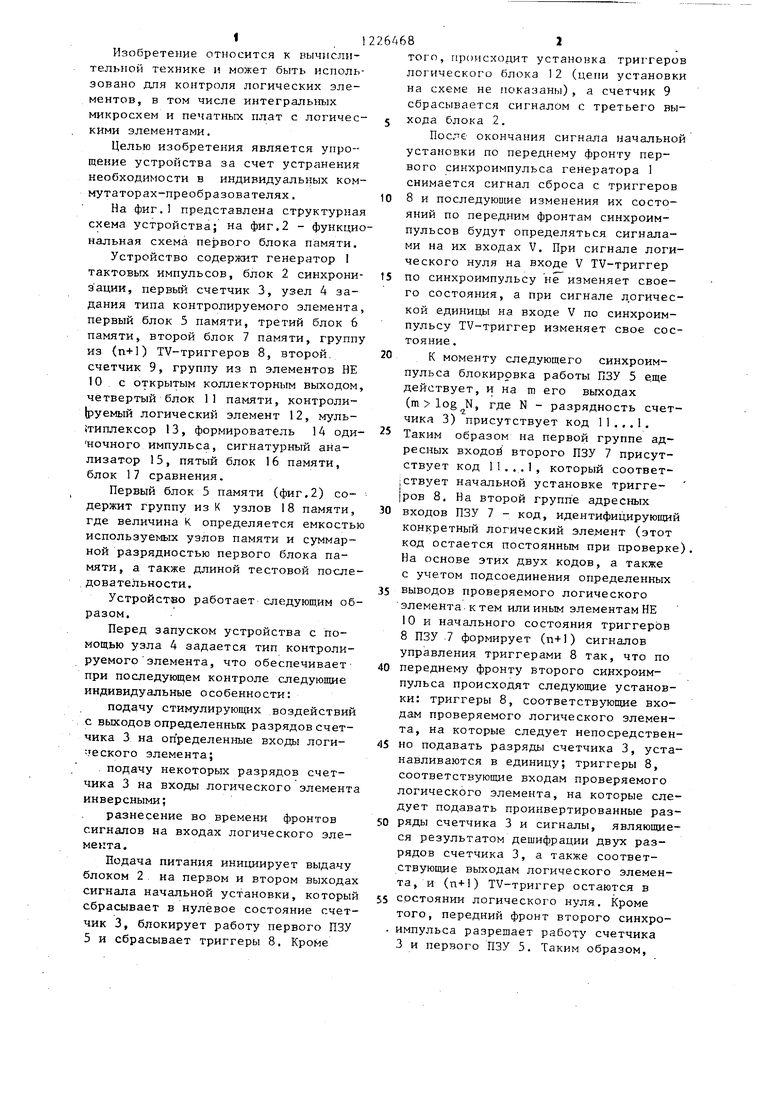

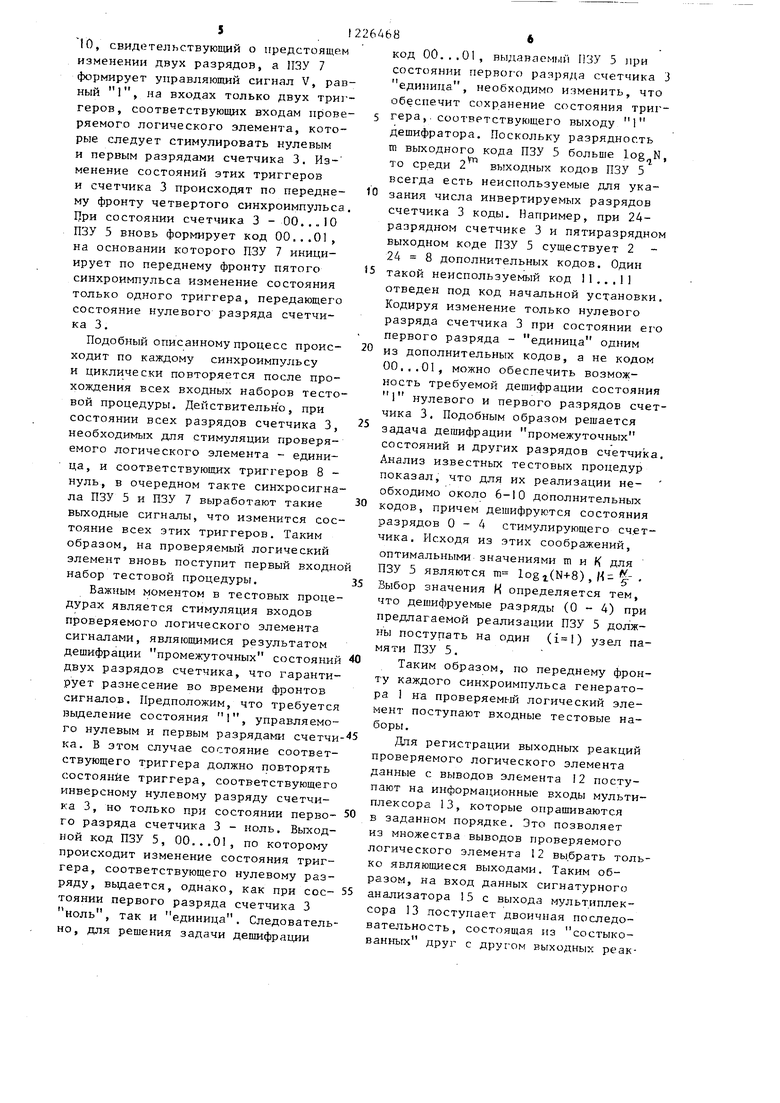

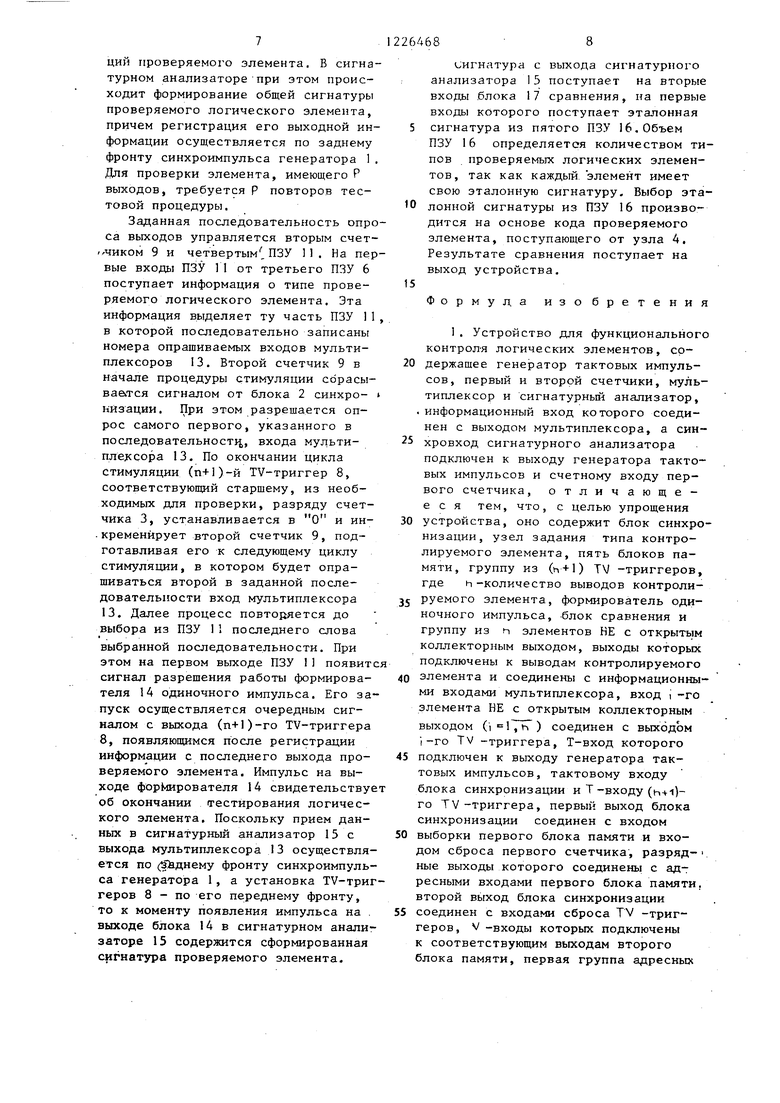

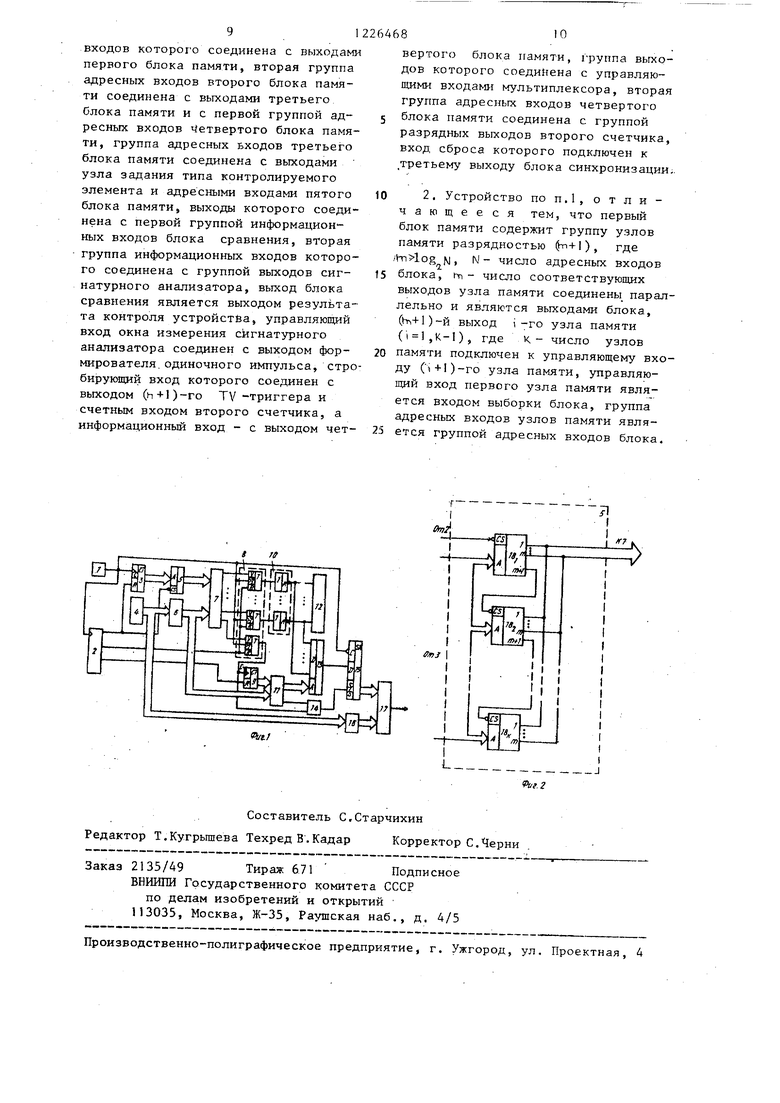

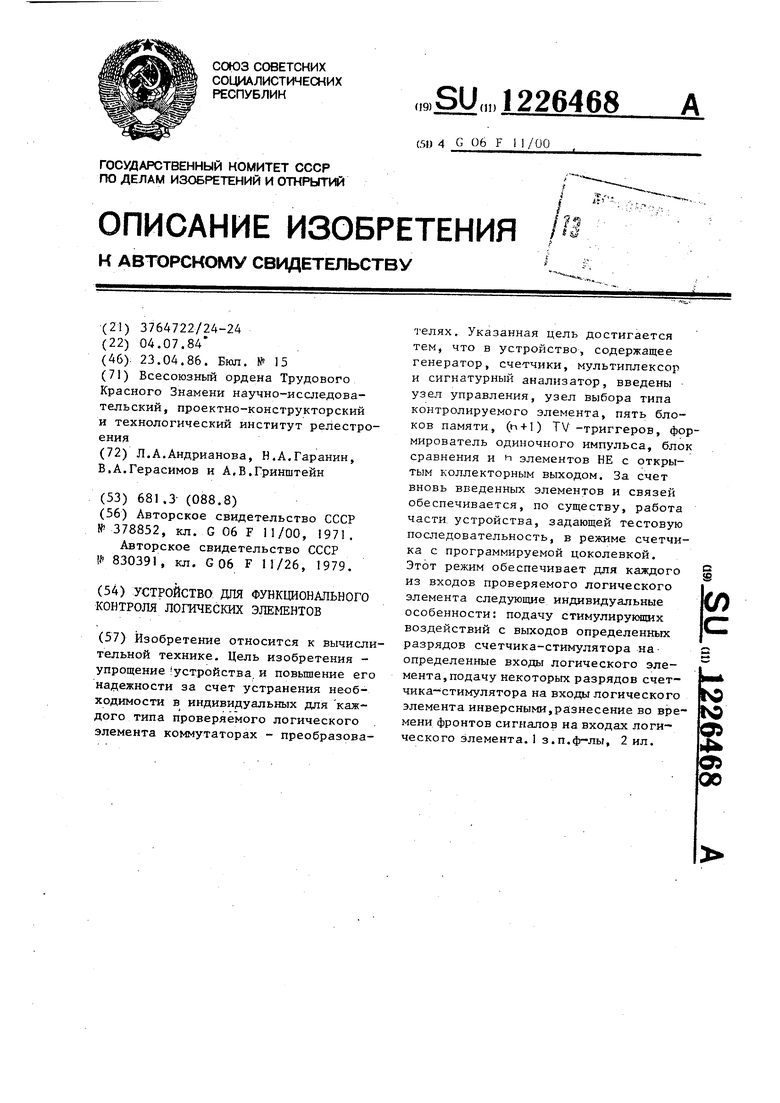

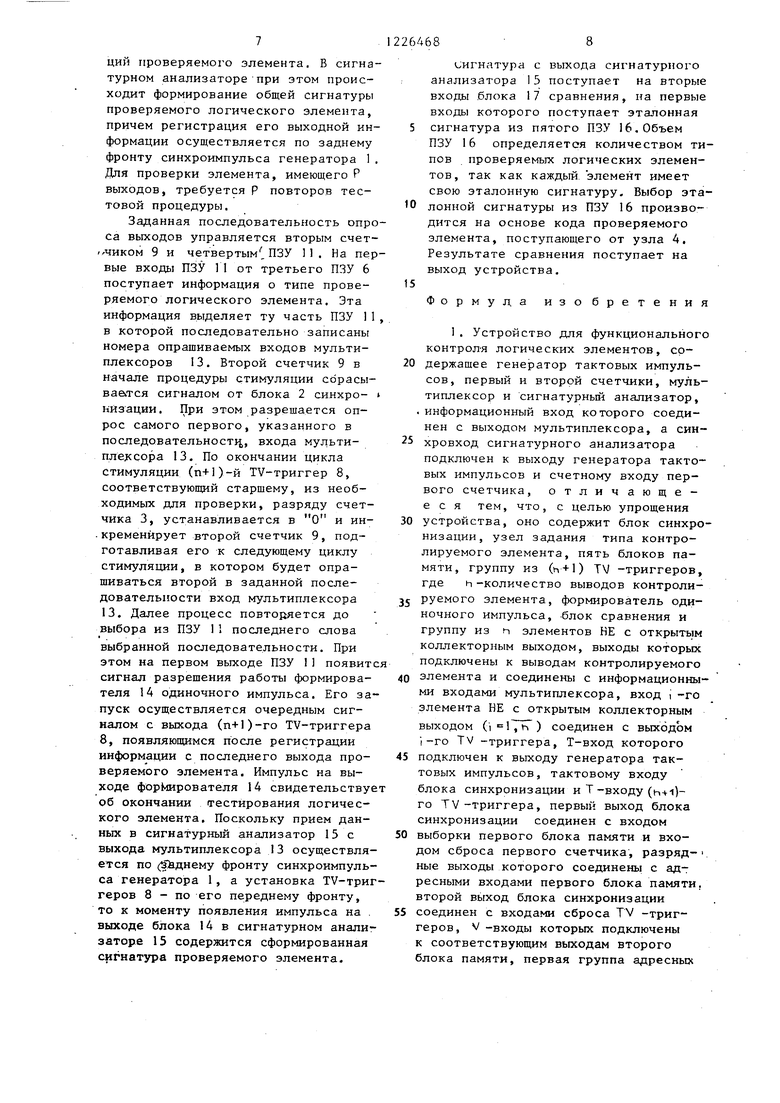

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема первого блока памяти.

Устройство содержит генератор I тактовых импульсов, блок 2 синхронизации, первый счетчик 3, узел 4 задания типа контролируемого элемента, первый блок 5 памяти, третий блок 6 памяти, второй блок 7 памяти, группу из (n+l) TV-триггеров 8, второй. счетчик 9, группу из п элементов БЕ 10с открытым коллекторным выходом, четвертый блок 11 памяти, контроли- |руемьш логический элемент 12, муль- типлексор 13, формирователь 14 оди- ночного импульса, сигнатурный анализатор 15, пятый блок 16 памяти, блок 17 сравнения.

Первый блок 5 памяти (фиг.2) содержит группу из К узлов 18 памяти, где величина К определяется емкостью используемых узлов памяти и суммарной разрядностью первого блока памяти, а также длиной тестовой последовательности.

Устройство работает следующим образом.

Перед запуском устройства с помощью узла 4 задается тип контролируемого элемента, что обеспечивает при последующем контроле следующие индивидуальные особенности:

подачу стимулирующих воздействий с выходов определенных разрядов счетчика 3 на определенные входы логи- еского элемента;

подачу некоторых разрядов счетчика 3 на входы логического элемента инверсными;

разнесение во времени фронтов сигналов на входах логического элемента.

Подача питания инициирует выдачу блоком 2 на первом и втором выходах сигнала начальной установки, который сбрасывает в нулевое состояние счетчик 3, блокирует работу первого ПЗУ 5 и сбрасывает триггеры 8, Кроме

того, происходит установка триггеров логического блока 12 (цепи установки на схеме не показаны), а счетчик 9 сбрасывается сигналом с третьего выхода блока 2.

После окончания сигнала начальной установки по переднему фронту первого синхроимпульса генератора 1 снимается сигнал сброса с триггеров 8 и последующие изменения их состояний по передним фронтам синхроимпульсов будут определяться сигналами на их входах V. При сигнале логического нуля на входе V TV-триггер

5 по синхроимпульсу не изменяет своего состояния, а при сигнале л.огичес- кой единицы на входе V по синхроимпульсу TV-триггер изменяет свое состояние .

0 К моменту следующего синхроимпульса блокировка работы ПЗУ 5 е.ще действует, и на m его выходах (т log N, где N - разрядность счетчика 3) присутствует код 11...1.

5 Таким образом на первой группе адресных входой второго ПЗУ 7 присутствует код 1I ... 1, который соответствует начальной установке триггеров 8. На второй группе адресных

0 входов ПЗУ 7 - код, идентифицирующий конкретный логический элемент (этот код остается постоянным при проверке). На основе этих двух кодов, а также с учетом подсоединения определенных

5 выводов проверяемого логического элемента. к тем или иным элементам НЕ 10 и начального состояния триггеров 8 ПЗУ 7 формирует (п+1) сигналов управления триггерами 8 так, что по

0 переднему фронту второго синхроимпульса происходят следующие установки: триггеры 8, соответствующие входам проверяемого логического элемента, на которые следует непосредствен5 но подавать разряды счетчика 3, устанавливаются в единицу; триггеры 8, соответствующие входам проверяемого логического элемента, на которые следует подавать проинвертированные раз50 ряды счетчика 3 и сигналы, являющиеся результатом дешифрации двух разрядов счетчика 3, а также соответствующие выходам логического элемента, и (n+l) TV-триггер остаются в

55 состоянии логического нуля. Кроме

того, передний фронт второго синхро- . импульса разрешает работу счетчика 3 и первого ПЗУ 5. Таким образом.

после этого синхроимпульса состояние выходов элементов НЕ Ю в точности соответствует тому состоянию, которое должны иметь входы проверяемого логического элемента при их стимуляции от счетчика и управляемого им дешифратора при состоянии счетчика 00...О, т.е. при подаче первого в тестовой процедуре входного набора. Двоичный счетчик при последовательном счете проходит все свои состояния, начиная с 00...О и кончая

11...1. При этом зная текущее состояние счетчика, всегда можно указать, сколько его разрядов изменяется (проинвертируются) при переходе к следующему состоянию. Например, для четырехзарядного счетчика переход из состояний 1010 и 0000 к состояниям 1011 и 0001 соответственно требует изменения одного разряда, а при переходе от состояния 1111 к состоянию 0000 (циклический счет) требуется изменение всех четырех разрядов. Более того, по числу разрядов, которые следует изменить, определяются и сами изменяемые разряды, так как. всегда изменяется группа разрядов, начиная с нулевого и до ближайшего разряда, находящегося в сост оянии О. Для указания числа изменяемых разрядов необходим код разрядностью ..log, N, где N - разрядность счетчика.

На указанном принципе и построена работа блоков 3,5,7,8, представяющих собой по существу счетчик с программируемой цоколевкой.

После поступления переднего фронта второго синхроимпульса разрещена работа первого ПЗУ 5, на которое поступает информация со счетчика 3. ПЗУ 5 представляет собой труппу из К узлов памяти разрядностью т+1 ( N), m выходов которых соединены параллельно, а (т +1)-й выход узла памяти управляет (i +1) узлом. Входы узлов памяти соответствуют адресным входам ПЗУ 5. ,

1-йузел18 памяти (,k) ПЗУ 5 аботает следующим образом.

Если поступающий на него код с выода счетчика 3 содержит хотя бы один разряд в состоянии О, то -и узел сигналов на своем (т -О-м ыходе блокирует работу (i )-го, а следовательно, и последующих узов памяти ПЗУ 5, а на других своих

226Д684

ш выходах .Ф )рм1фуе г код - число, разрядов счетчик; 3, которые изменятся при переходе к следукмцему его состоянию. Это число просто определя- 5 ется исходя из местоположения i-ro узла среди остальных (т.е. от поданной на него части кода с выхода счетчика 3), Если поступивший на i-й узел код не содержит ни одного нуля, 10 то i-й узел устанавливает m своих выходов в единицу, а сигналом с (ш +1)-го выхода разрешает работу (i +1)-го узла.

N На основе кода 00...О на.- млад15 ших разрядах счетчика 3 первый узел памяти ПЗУ 5 запрещает работу остальных узлов памяти, а на своих выходах формирует код 00.,.01, что свидетельствует об изменении счетчиком 3 20 только одного, а именно нулевого раз- ряда .при переходе к своему следующему состоянию. Этот код поступает на соответствующую часть адресных входов второго ПЗУ 7. Поскольку для 25 конкретного проверяемого логического элемента (он идентифицируется кодом на другой группе адресных входов ПЗУ 7) тестовой процедурой определено, какой из его входов должен 30 стимулироваться нулевым разрядом

счетчика 3, то ПЗУ 7 формирует сигнал логической единицы только на одном своем выходе, который связан с TV-триггером, соответствующим это- 35 му входа. Таким образом, по перед нему фронту третьего синхроимпульса изменится состояние только данного TV-триггера и, следовательно, на входах проверяемого логического эле- 40 мента установится информация как при непосредственной стимуляции от счетчика и управляемого им дешифратора при состоянии счетчика OO...OI. т.е. при подаче второго в тестовой 45 процедуре входного набора. Очевидно, что если необходима стимуляция инверсным нулевым разрядом, то работа всех узлов аналогична, а инверсия достигается за счет соответствующей 50 начальной установке нужного триггера по второму синхроимпульсу.

По переднему фронту третьего синхроимпульса произойдет также инкремен- тация счетчика 3 и он перейдет в 55 состояние 00...01. До четвертого синхроимпульса работа узлов 5, 7, 8 аналогична описанной за исключением того, что ПЗУ 5 формирует код 00..

10, свидетельствующий о предстоящем изменении двух разрядов, а ПЗУ 7 формирует управляющий сигнал V, равный 1, на входах только двух триггеров, соответствуюЕдих входам проверяемого логического элемента, которые следует стимулировать нулевым и первым разрядами счетчика 3. Из- менение состояний этих триггеров и счетчика 3 происходят по переднему фронту четвертого синхроимпульса. При состоянии счетчика 3 - 00.,„10 ПЗУ 5 вновь формирует код 00...0, на основании которого ПЗУ 7 инициирует по переднему фронту пятого синхроимпульса изменение состояния только одного триггера, передающего состояние нулевого разряда счетчика 3.

Подобный описанному процесс происходит по каждому синхроимпульсу и циклически повторяется после прохождения всех входных наборов тестовой процедуры. Действительно, при состоянии всех разрядов счетчика 3, необходимых для стимуляции проверяемого логического элемента - единица, и соответствующих триггеров 8 - нуль, в очередном такте синхросигна

ла ПЗУ 5 и ПЗУ 7 выработают такие выходные сигналы, что изменится состояние всех этих триггеров. Таким образом, на проверяемый логический элемент вновь поступит первый входно набор тестовой процедурьг,

Важным моментом в тестовых процедурах является стимуляция входов проверяемого логического элемента сигналами, являющимися результатом дешифрации промежуточных состояний двух разрядов счетчика, что гарантирует разнесение во времени фронтов сигналов. Предположим, что требуется выделение состояния 1, управляемого нулевым и первым разрядами счетчи ка. В этом случае состояние соответствующего триггера должно повторять состояние триггера, соответствующего инверсному нулевому разряду счетчика 3, но только при состоянии первого разряда счетчика 3 - ноль. Выходной код ПЗУ 5, OO...OI, по которому происходит изменение состояния триггера, соответствующего нулевому разряду, вьздается, однако, как при сое- тоянии первого разряда счетчика 3 ноль, так и единица. Следовательно, для решения задачи дешифрации

0

5

5

0

5

5

0

0

КОД 00... 01, выдаваем1,й ПЗУ 5 при состоянии первог о разряда счетчика 3 единица, необходимо изменить, что обеспечит сохранение состояния триггера, , соответствующего выходу 1 дешифратора. Поскольку разрядность m выходного кода ПЗУ 5 больше , то среди 2 выходных кодов ПЗУ 5 всегда есть неиспользуемые для указания числа инвертируемых разрядов счетчика 3 коды. Например, при 24- разрядном счетчике 3 и пятиразрядном выходном коде ПЗУ 5 существует 2 24 8 дополнительных кодов. Один такой неиспользуемый код 1 1 ... 1 отведен под код начальной установки. Кодируя изменение только нулевого разряда счетчика 3 при состоянии ег о первого разряда - единица одним из дополнительных кодов, а не кодом 00...01, можно обеспечить возможность требуемой дешифрации состояния 1 нулевого и первого разрядов счетчика 3. Подобным образом решается задача дешифрации промежуточных состояний и других разрядов счетчика. Анализ известных тестовых процедур показал, что для их реализации необходимо около 6-10 дополнительных кодов, причем дешифруются состояния разрядов 0-4 стимулирующего сч.ет- чика. Исходя из этих соображений, оптимальными значениями m и К для ПЗУ 5 являются т logt(N+8) , М- 5- Выбор значения И определяется тем, что дешифруемые разряды (О - 4) при предлагаемой реализации ПЗУ 5 должны поступать на один () узел памяти ПЗУ 5.

Таким образом, по переднему фронту каждого синхроимпульса генератора 1 на проверяемЕ-ш логический элемент поступают входные тестовые наборы.

Для регистрации выходных реакций проверяемого логического элемента данные с выводов элемента 12 поступают на информационные входы мультиплексора 13, которые опрашиваются в заданном порядке. Это позволяет из множества выводов проверяемого логического элемента 12 выбрать только являющиеся выходами. Таким образом, на вход данных сигнатурного анализатора 5 с выхода мультиплексора 13 поступает двоичная последо- состоящая КЗ состыко- с друг-ом выходных реаквательность, друг

ванных

ций проверяемого элемента, В сигнатурном анализаторе при этом происходит формирование общей сигнатуры проверяемого логического элемента, причем регистрация его выходной информации осуществляется по заднему фронту синхроимпульса генератора 1. Для проверки элемента, имеющего Р выходов, требуется р повторов тестовой процедуры.

Заданная последовательность опроса выходов управляется вторым счет Чиком 9 и четвертым , ПЗУ 11. На первые входы ПЗУ 11 от третьего ПЗУ 6 поступает информация о типе проверяемого логического элемента. Эта информация выделяет ту часть ПЗУ 11 в которой последовательно записаны номера опрашиваемых входов мультиплексоров 13. Второй счетчик 9 в начале процедуры стимуляции сорасы- сигналом от блока 2 синхро- нИзации. При этом разрешается опрос самого первого, указанного в последовательност1|,, входа мульти- пледссора 13. По окончании цикла стимуляции (п+1)-й TV-триггер 8, соответствующий старщему, из необходимых для проверки, разряду счетчика 3, устанавливается в О и ин.кременйрует второй счетчик 9, подготавливая его к следующему циклу стимуляции, в котором будет опрашиваться второй в заданной последовательности вход мультиплексора 13. Далее процесс повторяется до выбора из ПЗУ 11 последнего слова выбранной последовательности. При этом на первом выходе ПЗУ 11 появит сигнал разрешения работы формирователя 14 одиночного импульса. Его запуск осуществляется очередным сигналом с выхода (п+1)-го TV-триггера 8, появляющимся после регистрации информации с последнего выхода проверяемого элемента. Импульс на выходе формирователя 14 свидетельствуе об окончании тестирования логического элемента. Поскольку прием данных в сигнатурный анализатор 15 с выхода мультиплексора 13 осуществляется по (З днему фронту синхроимпульса генератора 1, а установка TV-триггеров 8 - по его переднему фронту, то к моменту появления импульса на . выходе блока 14 в сигнатурном анализаторе 15 содержится сформированная сигнатура проверяемого элемента.

5

сигнатура с выхода сигнатурного анализатора 15 поступает на вторые входы .блока 17 сравнения, иа первые входы которого поступает эталонная

5 сигнатура из пятого ПЗУ 16. Объем

ПЗУ 16 определяется количеством типов проверяемых логических элементов, так как каждый элемент имеет свою эталонную сигнатуру. Выбор эта0 лонной сигнатуры из ПЗУ 16 производится на основе кода проверяемого элемента, поступающего от узла 4. Результате сравнения поступает на выход устройства.

5

Формула изобретения

1. Устройство для функционального контрол-я логических элементов, ср- 0 держащее генератор тактовых импульсов, первый и второй счетчики, мультиплексор и сигнатурньш анализатор, . информационный вход которого соединен с выходом мультиплексора, а син- хровход сигнатурного анализатора подключен к выходу генератора тактовых импульсов и счетному входу первого счетчика, отличающееся тем, что, с целью упрощения 0 устройства, оно содержит блок синхронизации, узел задания типа контролируемого элемента, пять блоков памяти, группу из (h+1) TV -триггеров, где h-количество выводов контроли- 5 Руемого элемента, формирователь одиночного импульса, -блок сравнения и группу из h элементов НЕ с открытым коллекторным выходом, выходы которых подключены к выводам контролируемого 0 элемента и соединены с информационными входами мультиплексора, вход i -го элемента НЕ с открытым коллекторным выходом () соединен с выходом i-го TV -триггера, Т-вход которого 5 подключен к выходу генератора тактовых импульсов, тактовому входу блока синхронизации и Т-входу()- го TV -триггера, первый выход блока синхронизации соединен с входом 0 выборки первого блока памяти и входом сброса первого счетчика, разряд- ные выходы которого соединены с адресными входами первого блока памяти, второй выход блока синхронизации 5 соединен с входами сброса TV -триггеров, V -входы которых подключены к соответствующим выходам второго блока памяти, первая группа адресных

входов KOTOpoi o соединена с выходами первого блока памяти, вторая группа адресных входов второго блока памяти соединена с вьгходами третьего блока памяти и с первой группой ад- ресных входов Четвертого блока памяти, группа адресных входов третьего блока памяти соединена с выходами узла задания типа контролируемого элемента и адресными входами пятого блока памяти, выходы которого соединена с первой группой информацион- нь1х входов блока сравнения, вторая группа информационных входов которого соединена с группой выходов сиг- натурного анализатора, выход блока сравнения является выходом результата контроля устройства, управляющий вход окна измерения сигнатурного анализатора соединен с выходом фор- мирователя.одиночного импульса, стро бирующий вход которого соединен с выходом (h + l)-ro TV -триггера и счетным входом второго счетчика, а информационный вход - с выходом чет-

5 10 tS 20 25

26468 О

вертого блока памяти, группа выходов которого соединена с управляющими входами мультиплексора, вторая группа адресньтх входов четвертого ; блока памяти соединена с группой разрядных выходов второго счетчика, вход сброса которого подключен к третьему выходу блока синхронизации,.

2, Устройство по п.1, о т л и - чающееся тем, что первый блок памяти содержит группу узлов памяти разрядностью +1), где м. М- число адресных входов блока, hn - число соответствующих выходов узла памяти соединены параллельно и являются выходами блока, ()-й выход i-го узла памяти ,К-1), где к- число узлов памяти подключен к управляющему входу ( ii-4-I)-ro узла памяти, управляющий вход первого узла памяти является входом выборки блока, группа адресных входов узлов памяти является группой адресных входов блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Устройство для функционального контроля логических элементов | 1983 |

|

SU1327108A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1363215A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля многоканальной цифровой аппаратуры | 1986 |

|

SU1397860A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

Изобретение относится к вычислительной технике. Цель изобретения - упрощение устройства. и повышение его надежности за счет устранения необходимости в индивидуальных для каждого типа проверяемого логического элемента коммутаторах - преобразователях. Указанная цель достигается тем, что в ycTpofiCTBO, содержащее генератор, счетчики, мультиплексор н сигнатурный анализатор, введены узел управления, узел выбора типа контролируемого элемента, пять блоков памяти, (и + 1) TV -триггеров, формирователь одиночного импульса, блок сравнения и h элементов НЕ с открытым коллекторным выходом. За счет вновь введенных элементов и связей обеспечивается, по существу, работа части устройства, задающей тестовую последовательность, в режиме счетчика с программируемой цоколевкой. Этот режим обеспечивает для каждого из входов проверяемого логического элемента следующие индивидуальные особенности: подачу стимулирующих воздействий с выходов определенных разрядов счетчика-стимулятора на определенные входы логического элемента, подачу некоторых разрядов счетчика-стимулятора на входы логического элемента инверсными,разнесение во времени фронтов сигналов на входах логического элемента.1 з.п.ф-лы, 2 ил.

«Ч/е/

Составитель С.Старчихин Редактор Т.Кугрьшева Техред В.Кадар Корректор С.Черни

Заказ 2135/49 Тираж 671 Подписное ВНИИГШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| УСТРОЙСТВО для КОНТРОЛЯ СХЕМ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 0 |

|

SU378852A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-23—Публикация

1984-07-04—Подача