Изобретение относится к технике связи и может использоваться при построении приемопередатчиков широтно-импульсной манипуляции.

Цель изобретения - увеличение пропускной способности с одновременным упрощением.

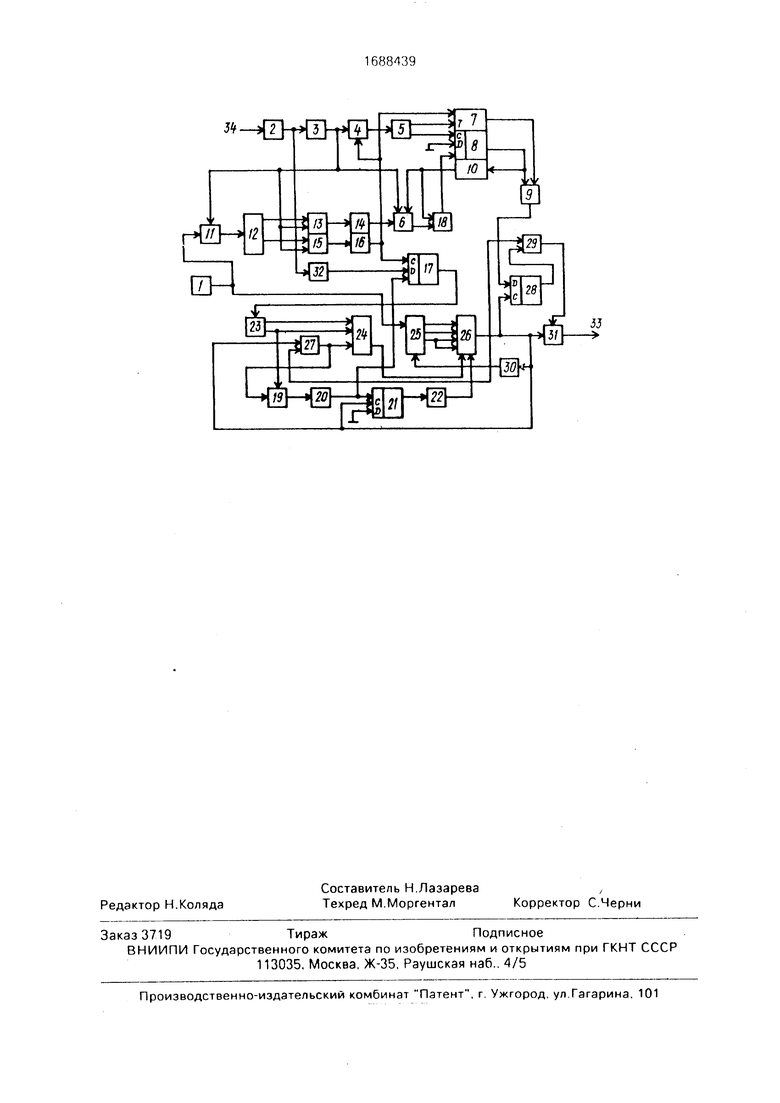

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит генератор 1 тактовых импульсов, фильтр 2 нижних частот, формирователь 3 прямоугольных импульсов, первый счетчик 4, первый дешифратор 5, первый регистр 6 сдвига, первый RS-триг- гер 7, триггер 8 и буфер заполнен, первый элемент ИЛИ 9, второй блок 10 задержки, второй счетчик 11, второй счетчик 11, второй

дешифратор 12, второй RS-триггер 13, первый блок 14 задержки, третий RS-триггер 15 третий блок 16 задержки, второй D-триггер 17, блок 18 потребителя информации, третий счетчик 19, третий дешифратор 20, третий D-триггер 21, четвертый блок 22 задержки, источник 23 информации, второй регистр 24 сдвига, делитель 25 частоты, мультиплексор 26, первый элемент И 27, первый D-триггер 28, второй элемент И 29, формирователь 30 коротких импульсов.амп- литудный манипулятор 31, пороговый блок 32.

Устройство для передачи и приема данных работает следующим образом.

Делитель 25 частоты, работающий от генератора 1, формирует три последовательо

00 00 4 СА) Ю

мости импульсов разной длительности Г) Т Тч, поступающие на вторые входы мультиплексора 26. Выходной сигнал последнего зависит от значения управляющих сигналов, действующих на его четвертом и пятом входах. Формирователь 30 коротких импульсов вырабатывает последовательность импульсов, совпадающих по времени с отрицательными перепадами выходного сигнала. Этой последовательностью производится синхронизации делителя 25 частоты для получения импульсов со скважностью 0,5

Данные от источника 23 информации в параллельном коде записываются регистр 24. Строб сопровождения данных устанав- ЛИВЛРТ в нопь ГЧРТЧИК 10 Очередным пире падом (отрицательным) с выхода- мультиплексора 26 второй D-триггер 21 устанавливается в состояние, при котором сигнал с выхода блока 22 задержки разре тает (через элемен г 27 И) выполнение сдви га регистре 24 сдвига и счет числа переданных бит счетчиком 19. Далее проис ходит сдвиг по каждому заднему фронту импульсов с выхода мультиплексора 26 во втором регистре 24 сдвига. В зависимости от значения очередного бита формируется импульс длительностью Ti или Т-2. По окончании передачи очередного поля данных происходит изменение значения сигнала на выходе дешифратора 20 и установка D-триг- гера 21 в состояние, обеспечивающее передачу импульсов синхронизации длительностью 1 v прекращение сдвига информации в регистре 24 сдвига и счета чис ла импульсов счетчиком 19. Амплитуда формируемых импульсов синхронизации AI или AJ, зависящая от готовности устройства к приему определяется значением сигналов на выходе D-триггера 21 и D-триггера 28. соединенных элементом И 29 выход ко торого управляет амплитудным манипулятором 31 Запись информации в D-триггер 28 может осуществляться, как по заднему фронту, так и по переднему фронту импульса с выходя мультиплексора 26. В последнем случае несколько повышается пропускная способность устройства, так как амплитуда импульсов синхронизации меняется уже в процессе его формирования. Наличие элемента 29 И позволяет выполнять амплитудную манипуляцию лишь импульсов синхронизации, а не всего сигнала в целом Это повышает надежность приема при значительной паразитной амплитудной модуляции сигнала из-за неравномерной амплитудно-частотной характеристики канала связи, вызывающей сильное ослабление импульсов с длительностью Тт и T-j

Входной аналоговый сигнал и линии связи через входной фильтр 2 нижних частот и формирователь 3 прямоугольных импульсов поступает на блоки 4.6 11. Импульс, поступающий на установочный вход счетчика 11, разрешает начать измерение его длительности путем подсчета импульсов с выхода генератора 1. В зависимости от длительности входных импульсов, с по0 мощью дешифратора 12 устанавливаются в 1 триггеры 13 и 15. Если длительность импульса Тз. то оба триггера устанавливаются в 1. а если Т 2 то только триггер 13. По заднему фронту входного импульса проис5 ходит сдвиг данных в регистре 6, Необходимая задержка обеспечивается блоком 14 задержки Одновременно происходит счет числа принятых бит счетчиком 4 Если принят хотя бы один бит, то сигналом с первого

0 выхода дешифратора 5 устанавливается в 1 RS-григгер 7, что означает Приемник занят. После приема всего поля данных с известным фиксированным числом бит устанавливается в 1 триггер 8 (Буфер запол5 нен). С помощью элемента ИЛИ 9 формируется сигнал К приему не готов, поступающий на D-вход D-триггера 28. Он запоминается по фронту импульса, поступающему на тактовый вход триггера D-тригге0 ра 28 с выхода мультиплексора 26. Сигнал Буфер заполнен с выхода триггера 8 через блок 10 задержки поступает на вход регистра 6 сдвига, запрещен сдвиг в нем. Од- новременно он поступает в блок 18

5 потребителя информации, который после считывания данных из регистра 6, выполняет сброс триггера 8 Буфер заполнен.

При поступлении импульсов синхронизации передним фронтом импульса с выхо0 да блока 16 задержки производится сброс RS-триггера 7 в нуль, установка в нуль счетчика 4 принятых бит и запись информации о готовности к приему в D-триггер 17. Последнее происходит лишь при отсутствии сигна5 ла на установочном входе D-триггера 17 и соответствует завершению передачи данных Сигнал К передаче готов с выхода D-триггера 17 поступает на вход источника 23 информации для занесения в регистр 24

0 новых данных в параллельном коде. После окончания входного импульса (во время паузы) происходит сброс RS-триггеров 13 и 14 и прекращение счета счетчиком 11. Готовность у абонента, находящегося на приеме

5 данньк с линии связи, определяется по амплитуде принятых импульсов синхронизации с помощью порогового блока 32. Информация о готовности к приему записывается в D-триггер 17 по переднему фронту импульса с выхода блока 16 задержки.

В устройстве время задержки элементов 10, 14, 16, 22 должно быть не менее времени задержки фронтов тактовых сигналов на входах блоков, на которые они поступают. В общем случае задержка должна быть такой длительности, чтобы при записи в триггер или сдвиговый регистр сигнал на информационном входе начинал меняться лишь после окончания фронта тактирующего импульса.

Формула изобретения Устройство для передачи и приема двоичной информации, содержащее последовательно соединенные фильтр нижних частот, формирователь прямоугольных импульсов пгрпый гчетчик, первый дешифратор, первый RS-триггер, первый элемент ИЛИ, первый D-триггер, последовательно соединенные генератор тактовых импульсов, второй счетчик, второй дешифратор, второй RS-триггер. первый блок задержки, первый регистр сдвига, блок потребителя информации, триггер Буфер заполнен и второй блок задержки, выход которого соединен с вторым входом блока потребителя информации и вторым входом первого регистра сдвига, последовательно соединенные третий RS-триггер. третий блок задержки и второй D-триггер, выход второго дешифратора соединен с первым входом третьего RS-триггера, второй вход которого, второй вход второго счетчика и второго RS-триггера, а также третий вход первого регистра сдвига соединены с выходом формирователя прямоугольных импульсов, выход третьего блока задержки соединен с вторыми входами первого счетчика и первого RS- триггера, второй выход первого дешифратора соединен с птпрым входом триггера Буфер заполнен, выход которого соединен с вторым входом первого элемента ИЛИ, первый , второй выходы источника

информации соединены соответственно с первым, вторым входами второго регистра сдвига, третий вход которого соединен с выходом первого элемента И. подключен- 5 ным к первому входу третьего счетчика, второй вход которого соединен с вторым выходом источника информации, выход третьего счетчика через третий дешифратор соединен с первым входом третьего D-триг0 гера и вторым входом второго D-триггера, выход генератора тактовых импульсов соединен с первым входом делителя частоты, первый, второй, третий выходы которого соединены соответственно с первым, вторым,

5 третьим входами мультиплексора, выход которого через формирователь коротких импульсов соединен с вторым входом делителя частот, выход третьего D-триггера через четвертый блок задержки соединен с

0 четвертым входом мультиплексора и первым входом первого элемента И, второй вход которого соединен с выходом мультиплексора, выход первого D-триггера соединен с первым входом второго элемента И,

5 отличающееся тем, что, с целью увеличения пропускной способности с одновременным упрощением, в него введены пороговый блок и амплитудный манипулятор, причем входом устройства яв0 ляется вход фильтра нижних частот, выход которого через пороговый блок соединен с третьим входом второго D-триггера, выход которого соединен с входом источника информации, выход второго регистра сдвига

5 соединен с пятым входом мультиплексора, шестой вход которого соединен с третьим выходом делителя частоты, а выход - с вторым входом первого D-триггера и первым входом амплитудного манипулятора, выход

0 которого является выходом устройства, а второй вход соединен с выходом второго элемента И. второй вход которого соединен с выходом четвертого блока задержки.

(§

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для последовательного обмена данными с квитированием | 1989 |

|

SU1720164A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для приема и передачи цифровой двоичной информации | 1989 |

|

SU1693734A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для передачи и приема данных | 1988 |

|

SU1589417A1 |

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

Изобретение относится к технике связи и может использоваться при построении приемопередатчиков широтно-импульсной манипуляции. Цель изобретения - увеличение пропускной способности с одновременным упрощением. Устройство для передачи и приема двойной информации содержит генератор 1 тактовых импульсов, фильтр 2 нижних частот формирователь 3 прямоугольных импульсов, счетчики 4, 11, 19. дешифраторы 5, 12, 20, регистры б, 24 сдвига, RS триггеры 7, 13, 15, триггер 8 буфер заполнен, элементы ИЛИ 9, блоки 14, 10, 16, 22 задержки, D-триггеры 28. 17, 21, блок 18 потребителя информации, источник 23 информации, делитель 25 частоты, мультиплексор 26, элементы И 27, 29, формирователь 30 коротких импульсов Цель достигается введением амплитудного манипулятора 31, порогового блока 32. Пропускная способность устройства повышается т к амплитуда импульсов синхронизации меняется уже в процессе формирования Наличие элемента И 29 позволяет выполнять амплитудную манипуляцию лишь импульсов синхронизации, а не всего сигнала в целом. Это повышает надежность приема при значительной паразитной амплитудной модуляции сигнала из-за неравномерной амплитудно-частотной характеристики канала связи 1 ил 00 с

| Устройство для передачи и приема данных | 1988 |

|

SU1589417A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-10-30—Публикация

1989-07-19—Подача