1

Изобретение относится к импульсной технике и предназначено для ис- . пользования в интегральных логических микросхемах цифровых ЭВМ и сие- , тем управления.5

Известны транзисторно-транзисторные логические элементы И-ИЛИ-НЕ, которые представляют собой соединение К резисторно-транзисторных сборок, каждая из которых содержит источник 10 тре.нзистор и многоэмиттерный транзистор с М эмиттерами, и сложный инвертор, содержащий 3-4 транзистора и столько же резисторов 1.

. Недостатком этих элементов яв- 5 ляется относительно большое число компонентов и значительная потребл-яемая мощность.

.Наиболее близким по технической сущности к предлагаемому является 2.0 элемент И-НЕ транзисторно-транзисторной логики , содержагаий шину питания, источник положительного опорного напряжения, транзисторный инвертор и схему И, состоящую из 25 продольного .р-п-р транзистора и многоэмиттерного ь-р-п транзистора. Коллектор транзистора сое.цинен q базой п-р-п транзистора, база р-п-р транзисгтора соединена 30

с источником положительного опорного напряжения, эмиттер р-п-р транизстора соединен с шиной положительного напряжения питания. Эмиттеры п-р-п транзистора соединены с логическими входами элемента, а его коллектор со входом инвертора 2 .

Недостатком данного элемента И-НЕ являются его ограниченные логические возможности.

Цель изобретения - расширение логических возможностей элемента.

Поставленная цель достигается тем, что в транзисторно-транзисторный; логический элемент И-ИЛИ-НЕ, содержащий инвертор, выход которого соединен с выходом элемента,многоколлекторный р-п-р транзистор, эмиттер которого соединен с шиной питания, база - с выходом источника опорного напряжения, введены многоэмиттерные п-р-п транзисторы, коллекторы которых соединены с базой многоколлекторного р-п-р транзистора, базы - с соответствугощ1 ми коллекторами многоколлекторного р-п-р транзистора, первые эмиттеры со входом инвертора, остальные

эмиттеры - с соответствующими логическими входами элемента.

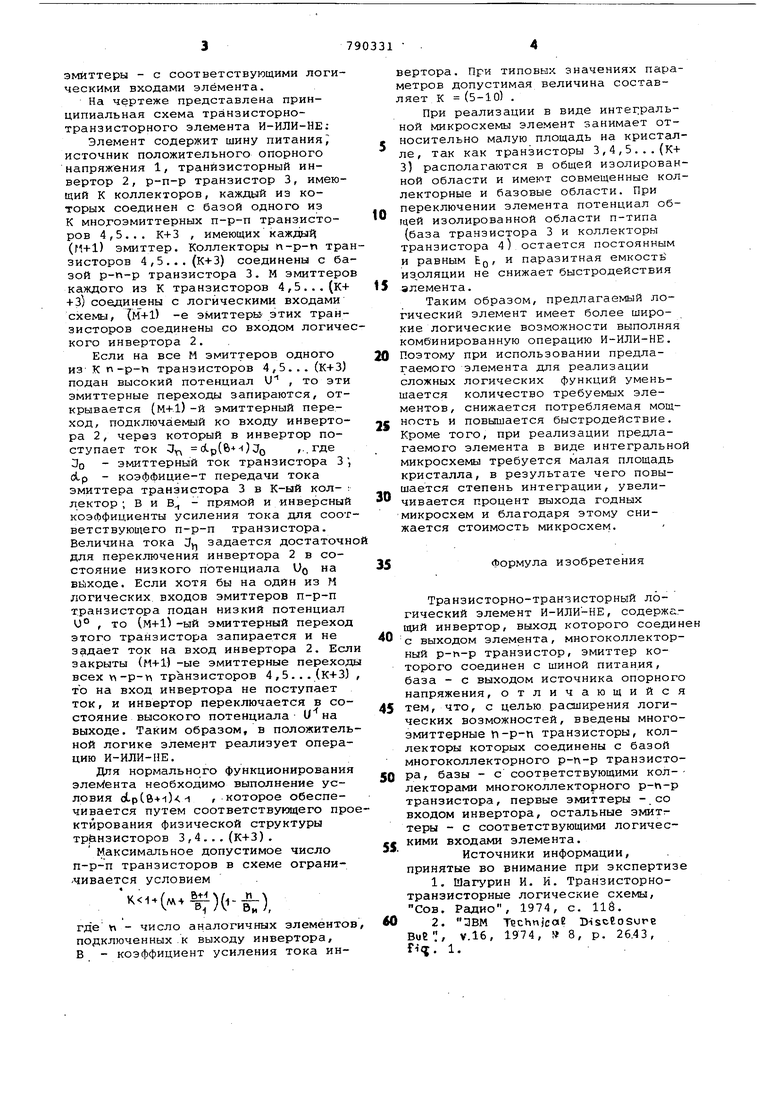

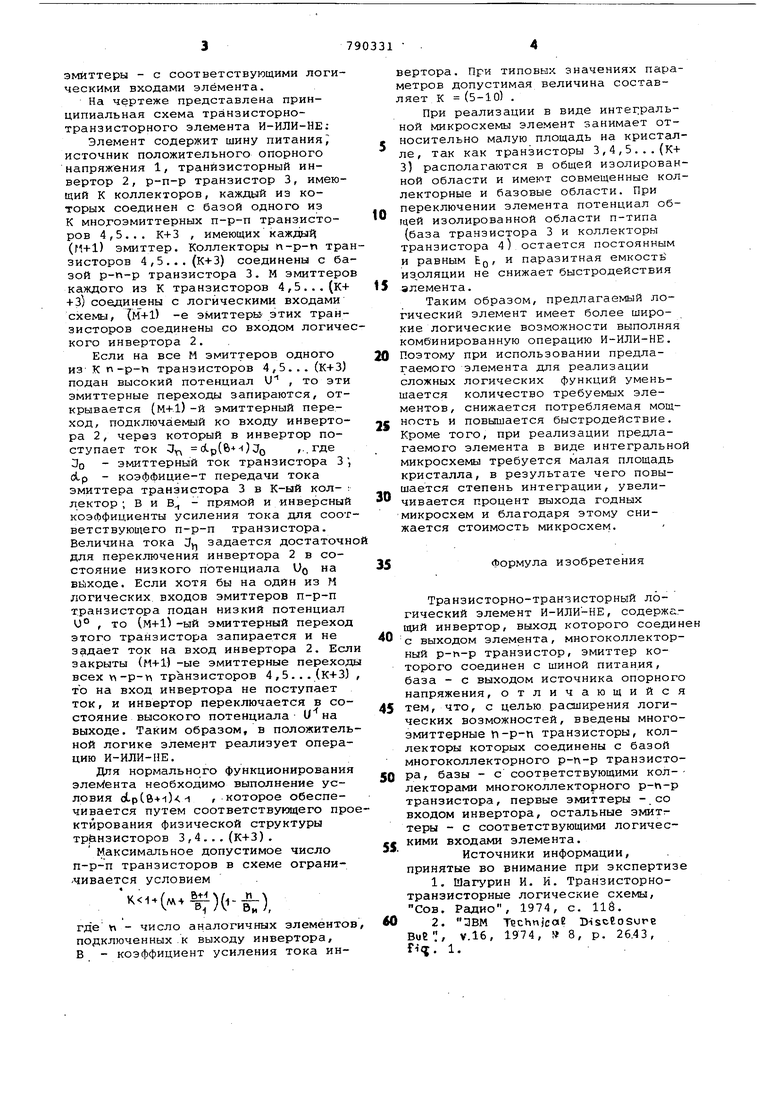

На чертеже представлена принципиальная схема транзисторнотранзисторного элемента И-ИЛИ-НЕ;

Элемент содержит шину питания источник положительного опорного напряжения 1, транйзисторный инвертор 2, р-п-р транзистор 3, имеющий К коллекторов, каждый из которых соединен с базой одного из К многоэмиттерных п-р-п транзисторов 4,5,.. К+3 , имеющих каждый (fHl) эмиттер. Коллекторы п-р-п транзисторов 4,5... (к+3) соединены с базой р-п-р транзистора 3. М эмиттеров каждого из К транзисторов 4,5...(к+ + 3) соедин ены с логическими входами схемы, М+1) -е эМиттеры этих транзисторов соединены со входом логического инвертора 2.

Если на все М эмиттеров одного из К п-р-п транзисторов 4,5... (к+3) подан высокий потенциал U , то эти эмиттерные переходы запираются, открывается (м+1) -и эмиттерный переход, подключаемый ко входу инвертора 2, через который в инвертор поступает ток ;j (6+)crQ ,..где Ло - эмиттерный ток транзистора 3; dp - коэффицие-т передачи тока эмиттера транзистора 3 в К-ый кол- : лектор ; В и В - прямой и инверсный коэффициенты усиления тока для соответствующего п-р-п транзистора. Величина тока J. задается достаточно для переключения инвертора 2 в состояние низкого потенциала UQ на вйходе. Если хотя бы на один из Н логических входов эмиттеров п-р-п транзистора подан низкий потенциал и° , то (м+1) -ый эмиттерный переход этого транзистора запирается и не задает ток на вход инвертора 2. Если закрыты (f1+l) -ые эмиттерные переходы Bcexv -p-v транзисторов 4,5...(к+3) то на вход инвертора не поступает ток, и инвертор переключается в состояние высокого потенциала Uна выходе. Таким образом, в положительной логике элемент реализует операцию И-ИЛИ-НЕ.

Для нормального функционирования необходимо выполнение условия oLp(e+-i)i , которое обеспечивается путем соответствукидего проектирования физической структуры тр&нзисторов 3,4...(к+3).

Максимальное допустимое число п-р-п транзисторов в схеме ограни-чивается условием

H- Ki-tl

где v - число аналогичных элемеитов, подключенных к выходу инвертора, В - коэффициент усиления тока инвертора. При типовых значениях параметров допустимая величина составляет К (5-10) .

При реализации в виде интегральной Микросхемы элемент занимает от. носительно малую площадь на кристалле, так как транзисторы 3,4,5...(К+ 3) располагаются в общей изолированной области и имеют совмещенные коллекторные и базовые области. При

I переключении элемента потенциал общей изолированной области п-типа (база транзистора 3 и коллекторы транзистора 4) остается постоянным и равным EQ, и паразитная емкость изрляции не снижает быстродействия

$ элемента.

Таким образом, предлагаемый логический элемент имеет более широкие логические возможности выполняя комбинированную операцию И-ИЛИ-НЕ.

0 Поэтому при использовании предлагаемого элемента для реализации сложных логических функций уменьшается количество требуемых элементов, снижается потребляемая мощность и повышается быстродействие. Кроме того, при реализации предлагаемого элемента в виде интегральной микросхемы требуется малая площадь кристалла, в результате чего повышается степень интеграции, увеличивается процент выхода годных микросхем и благодаря этому снижается стоимость микросхем.

Формула изобретения

Транзисторно-транзисторный логический элемент И-ИЛИ-НЕ, содержащий инвертор, выход которого соединен

с выходом элемента, многоколлекторный транзистор, эмиттер которого соединен с шиной питания, база - с выходом источника опорного напряжения, отличающийся

тем, что, с целью расширения логических возможностей, введены многоэмиттерные ti-р-п транзисторы, коллекторы которых соединены с базой многоколлекторного р-п-р транзистоР базы - с соответствующими кол-лекторами многоколлекторного р-п-р транзистора, первые эмиттеры - со входом инвертора, остальные эмитгтеры - с соответствующими логическими входами элемента.

Источники информации, принятые во внимание при экспертизе

1. Ыагурин И. И. Транзисторнотранзисторные логические схемы, Сов. Радио, 1974, с. 118.

2. ЭВМ Technicae D-iscEosufe

Bug:/ V.16, 1974, 8, p. 26.43, fiJJ. 1..

/(А,-Аг:...А„НВ,-б2:..... ... fffil

-ОЧ-f

источник опорного напря/кений

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| Транзисторно-транзисторный элемент и-не/и | 1973 |

|

SU450365A1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Входной каскад транзисторно-транзисторной логической схемы | 1979 |

|

SU1012764A1 |

| Транзисторно-транзисторный инвертор | 1989 |

|

SU1651372A1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| Инвертор на транзисторно-транзисторных логических элементах | 1974 |

|

SU645280A1 |

Авторы

Даты

1980-12-23—Публикация

1977-07-11—Подача