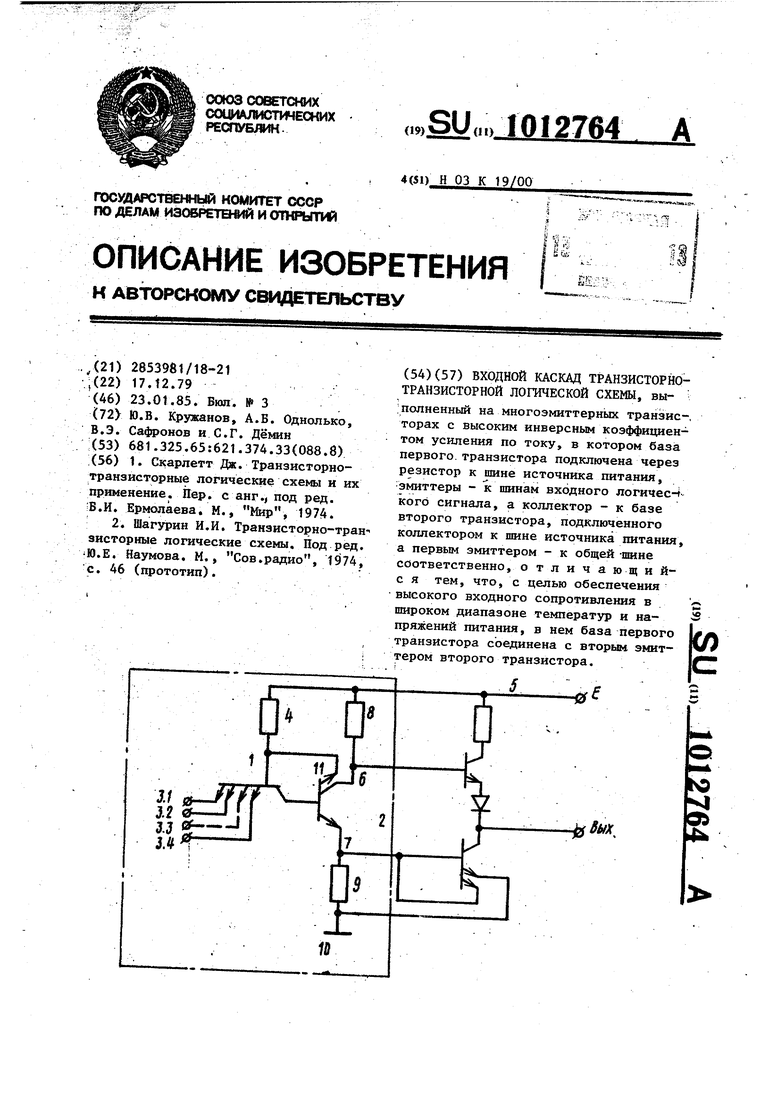

Изобретение относится к автоматике и вычислительной техникеj в частности к транзисторно-транзисторным логическим схемам, и может быть использовано в различных системах управления и контроля, в счетных и управляющих электронно-вьгаислительных машинах. Известны транзисторно-транзисторные логические схемы, выполненные на биполярных транзисторах с низким инверсным коэффициентом, содержащие входной каскад, вьтолненный на много эмиттерном транзисторе, база которог через резистор подключена к шине ис точника питания 5 коллектор - к базе следующего транзистора, а эмиттеры к шинам логических входных сигналов Tl Яедостаток такой схемы состоит в большой занимаемой площади на кристалле, что ограничивает степень интеграции логических устройствэ собранных на таких схемах. Указанный не достаток обусловлен использованием в таких ТТЛ схемах стандартных биполярных транзисторов 5 занимающих на кристалле площадь в три раза большую, чем, например 5 площадь так называемых КИД-транзисторов, Однако КИД-транзисторы имеют высокий инверс ный коэффициент усиления по току, что не позволяет строить на них вход ные каскады упомянутых ТТЛ схем из-з больших втекающих входных токов. Ближайшим техническим решением к предлагаемому является транзисторнотранзисторная логическая (ТТЛ) схема выпол1 енная на транзисторах с высоким инверсным коэффициентом усиления входной каскад которой также выпол нён на многоэмиттерных транзисторах с высоким инверсньи- коэффициентом усиления по току, в котором база первого транзистора подключена, чере резистор к Бшне источника питания, эмиттеры - к шинам входного логического сигнала, а коллектор - к базе второго транзистора, подключенного коллектором к шине источника питания, а эмиттером - к общей шине соответственно . L2j Б указанной ТТЛ - схеме для умень шения входного тока и увеличения Е ходного сопротивления база первого транзистора соединена с базой второго тран истора через резистор, величина сопротивления которого ограничена и сверху и снизу. СопротивлеHVie этого резистора выбирается таким, чтобы коллекторный переход был закрыт как при низком, так и при высоком напряжении на входах. Это ограничивает величину сопротивления сверху, с другой стороны это сопротивление не может быть слишком малым, так как необходимо обеспечить запирание второго транзистора при низком напряжении хотя бы на одном из входов схемы. Указанные условия не соблюда1ртся--в широком диапазоне температур и напряжений питания. Целью изобретения является обеспечение высокого входного сопротивления ТТЛ схемы на транзисторах с высоким инверсным коэффициентом усиления по току в широком диапазоне температур и напряжений питания. Поставленная цель достигается тем, что в входном каскаде схемы, выполненном на многоэмиттерных транзисторах с высоким инверсным коэффициентом усиления по току,в котором база первого транзистора подключена через резистор к шине источника питания, эмиттеры - к шинам входного логического сигнала, а коллектор - к базе второго транзистора, подключенного коллектором к шине источника питания, а эмиттером - к общей шине соответственно, база первого транзистора соединена с вторым эмиттером BTOporo транзистора. Принципиальная электрическая схема входного каскада ТТЛ-схемы, выполненного согласно предлагаемому изобретению, изображена на чертеже. Входной каскад ТТЛ схемы содержит многоэмиттерные транзисторы 1 и 2 с высоким инверсным коэффициентом усиления по току. Эмиттеры первого транзистора подсоединены к шинам 3.1, 3.2, 3.3 и 3,4 логического входного сигнала, база - через резистор 4 к шине 5 источника напряжения питания, а коллектор соединен с базой транзистора 2, коллектор6 и первый эмиттер 7 которого подсоединены ч-ерез резисторы 8 и 9 к шине 5 источника питания и общей шине 10 соответственно. Второй эмиттер 11 второго транзистора соединен с базой первого транзистора. Работа устройства происходит следующим образом. При подаче на все шины 3.1-3.4 высокого потенциала, соответствующего уровню логической единицы (входной каскад ТТЛ схемы обеспечивает выполнение в этом одном из возможных его вариантов логическо функции и), втекающий в каждый из эмиттеров транзистора 1 ток 3g,j связан с током его базы соотношением ,, где 6 , - инверсный коэффициент уси ления первого транзистора по и -му входу. Величина тока коллектора транзистора 1, являющегося током базы транзистора 2, достаточна для насыщения последнего. Как только транзистор 2 входит в насыщение, т.е. потенциал его коллектора становится меньще потенциала базы, и следовательно, меньше потенциала второго эмитд-ера (всегда больщего потенциала базы на величину падения напряжения на переходе база - коллектор транзистора 1) часть тока,протекающего через резистор 4, ответвляется через второй транзисторПО цепи: второй эмитте15 11 - коллектор 6 - первый эмиттер 7. При этом транзистор 2 работает в инверсном режиме по второму эмиттеру. Ток, вытекающий из базы транзистора 1 , поддерживается благодаря действию цепи об,ратной связи, на уровне, обеспечивающем минимальный ток насыщения в базу транзистора 2. Следов§тельно, величина тока базы транзистора 1 в BJ раз меньше минимального тока насьш ения транзистора 2 и стабилизируется обратной связью на этом уровне при всех колебаниях параметров схемы. При возникновении возмущающего воздействия соответствующего изменения тока базы транзистора 1 не произойдет. Так, например, при увеличении питающего напряжения (излищний ток базы транзистора 1 будет стекать через транзистор 2 и резистор 9 на общую шину 10. При уменьшении питающего напряжения то.х в цепи обратной связи уменьшается, обеспечивая неизменность базовых то ков транзисторов 1 и 2. Поскольку сумма всех токов, втекающих в эмиттеры транзистора 1, примерно равна току базы транзистора 2, то обеспечение неизменности и малой величины тока базы транзистора 1 обусловливает постоянство указанной суммы токов и высокое входное сопротивление ТТЛ схемы в широком диапа3оне температур и напряжений питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный транзисторно-транзисторный логический элемент | 1980 |

|

SU902261A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| Транзисторно-транзисторный логический элемент | 1983 |

|

SU1128387A1 |

| Транзисторно-транзисторный логический элемент "и-или-не | 1977 |

|

SU790331A1 |

| Интегральная логическая схема | 1979 |

|

SU1001480A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| ПРИЕМНОЕ ИНТЕГРАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU367553A1 |

| Интегральная логическая схема | 1979 |

|

SU1001479A1 |

ВХОДНОЙ КАСКАД ТРАНЗИСТОРНОТРАНЗИСТОРНОЙ ЛОГИЧЕСКОЙ СХЕМЫ, выполненный на многоэмиттерных транзис-, торах с высоким инверсным коэффициентом усиления по току, в котором база первого, транзистора подключена через резистор к шине источника питания, эмиттеры - к шинам входного логичес-tкого сигнала, а коллектор - к базе второго транзистора, подключенного коллектором к шине источника питания, а первым эмиттером - к общей -шине соответственно, отличающийс я тем, что, с целью обеспечения высокого входного сопротивления в широком диапазоне температур и напряжений питания, в нем база первого (Л транзистора соединена с вторым эмитс тером второго транзистора. ; .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Скарлетт Дж | |||

| Транзисторнотранзисторные логические схемы и их применение | |||

| Пер | |||

| с анг.| под ред | |||

| Б.И | |||

| Ермолаева, М., Мир, 1974 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шагурин И.И | |||

| Транзисторно-транзисторные логические | |||

| Под ред | |||

| Ю.Е | |||

| Наумова | |||

| М., Сов.радио, 1974, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-01-23—Публикация

1979-12-17—Подача