го-цифрового преобразователя и другим входом перемпожителя включены последовательно комбинационный сум1иатор, промежуточный регистр, блок па1у1я ги и блок вычисления модуля, между выходом синхронизатора и другим входом блока памяти включен коммутатор адреса, а межд выходом блока памяти и другим входом комбинационного сумматора включен инвертор, при этом к управляющему входу аналого-цифрового преобразователя и задающему входу синхронизатора подключена шина опорного сигнала, выход син хронизатора соединен с другим входоц промежуточного регистра и с третьим входом накапливающего сумматора, а выход счетчика импульсов подключен к третьему входу блока памяти.

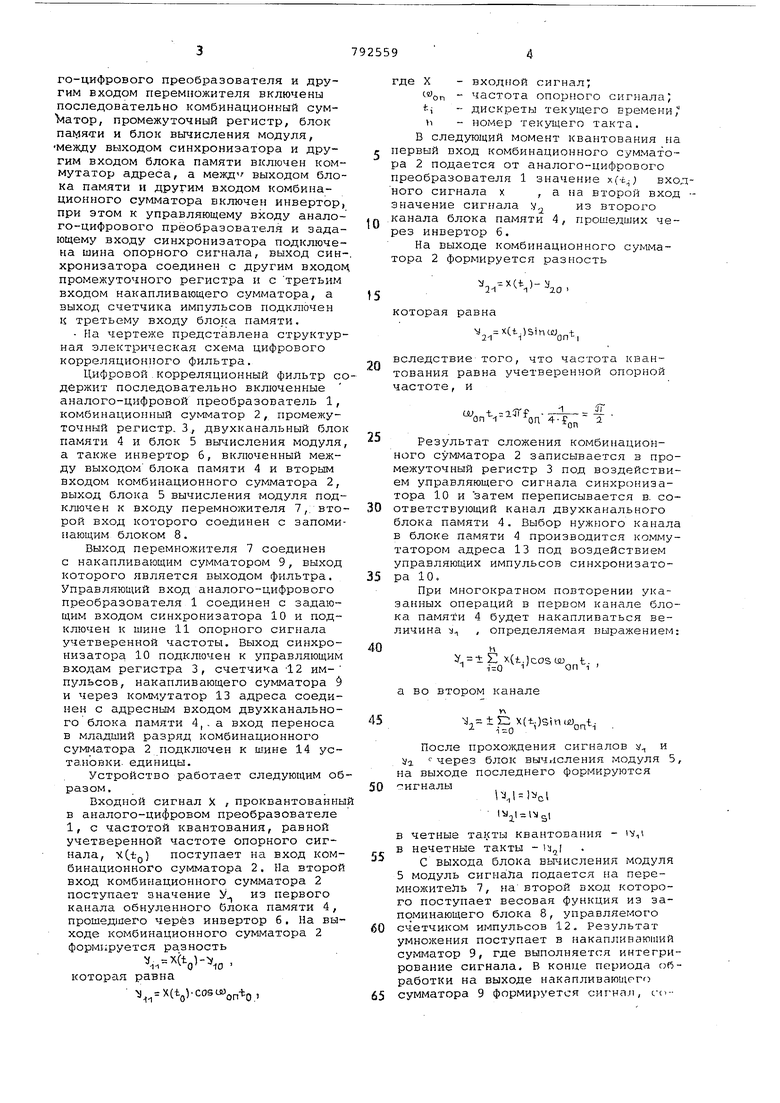

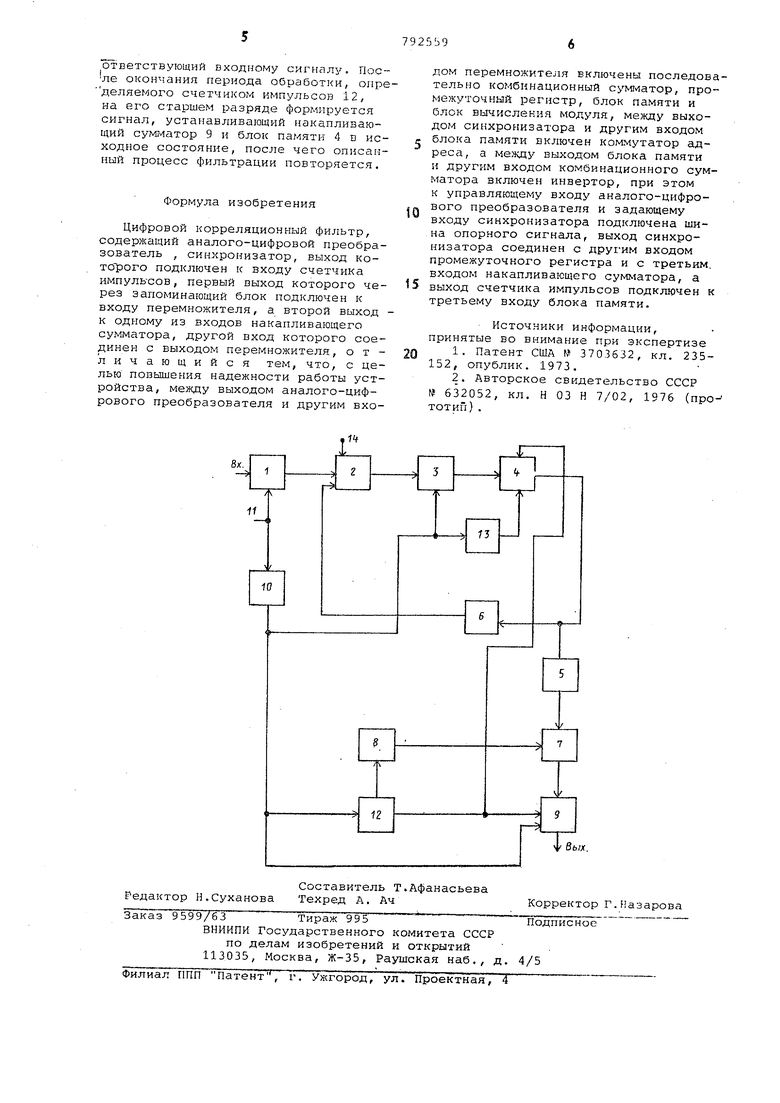

На чертеже представлена структурная электрическая схема цифрового корреляционного фильтра.

Цифровой.корреляционный фильтр сдержит последовательно включенные аналого-цифровой преобразователь 1, комбинационный сумматор 2, промежуточный регистр. 3, двухканальный бло памяти 4 и блок 5 вычисления модуля а также инвертор б, включенный между выходом блока памяти 4 и вторым входом комбинационного сумматора 2, выход блока 5 вычисления модуля подключен к входу перемножителя 7,: второй вход которого соединен с запоминающим блоком 8.

Выход перемножителя 7 соединен с накапливающим сумматором 9, выход которого является выходом фильтра. Управляющий вход аналого-цифрового преобразователя 1 соединен с задающим входом синхронизатора 10 и подключен к шине 11 опорного сигнала учетверенной частоты. Выход синхронизатора 10 подключен к управляющим входам регистра 3, счетчика 12 импульсов, накапливающего сумматора $ и через коммутатор 13 адреса соединен с адресным входом двухканального блока памяти 4,, а вход переноса в младший разряд комбинационного суг«1матора 2 подключен к шине 14 установки, единицы.

Устройство работает следующим образом.

Входной сигнал X , проквантованны в аналого-цифровом преобразователе 1, с частотой квантования, равной учетверенной частоте опорного сигнала, XCI-Q) поступает на вход комбинационного сумматора 2. На второй вход комбинационного сумматора 2 поступает значение У из первого канала обнуленного блока памяти 4, прошедшего через инвертор б, На выходе комбинационного сумматора 2 формируется разность

..-(,0 которая равна

X(tg).cosi ori-to.

где X - входной сигнал;

с«оп - частота опорного сигнала; t-i -- дискреты текущего времени, и - номер текущего такта. В следующий момент квантования на 2 первый вход комбинационного сумматора 2 подается от аналого-цифрового преобразователя 1 значение х(-с) входного сигнала х , а на второй вход

значение сигнала v,,

из второго

«Q .канала блока памяти 4, прошедших через инвертор б.

На выходе комбинац1 онного сумматора 2 формируется разность

2.

которая равна

4)(t)sinc« t,

вследствие того, что частота квантования равна учетверенной опорной частоте, и

IL а

%n% foa-4

on

Результат сложения комбинационного сумматора 2 записывается в промежуточный регистр 3 под воздействием управляющего сигнала синхронизатора 10 и затем переписывается в. соответствующий канал двухканального блока памяти 4. Выбор нужного канала в блоке памяти 4 производится коммутатором адреса 13 под воздействием управляющих импульсов синхронизатора 10,

При многократном повторении указанных операций в первом канале блока памяти 4 будет накапливаться величина , определяемая выражением:

h

ir (t.,cos(,t. ,

а во втором канале

(i)s %n После прохож,цения сигналов v и УЭ. -через блок вычисления модуля 5, на выходе последнего формируются сигналы

(,-

в четные такты квантования -

в нечетные такты - PJ,

С выхода блока вычисления модуля 5 модуль сигнала подается на перемножитеЛь 7, на второй вход которого поступает весовая функция из запоминающего блока 8, управляемого

счетчиком импульсов 12. Результат умножения поступает в накапливающий сумматор 9, где выполняется интегрирование сигнала. В конце периода обработки на выходе накапливающего

сумматора 9 формируется ситна.п, с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой корреляционнойфильТРАции | 1978 |

|

SU799108A1 |

| Измеритель сдвига фаз | 1986 |

|

SU1366966A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| УСТРОЙСТВО для ПРОСТРАНСТВЕННО-ВРЕМЕННОГО СЕЙСМИЧЕСКОГО АНАЛИЗА | 1973 |

|

SU393742A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Устройство для стабилизации средней частоты шумовых выбросов над пороговым уровнем | 1980 |

|

SU902269A1 |

| Измеритель сдвига фаз | 1979 |

|

SU834593A2 |

| Цифровой фазометр | 1982 |

|

SU1033983A1 |

Авторы

Даты

1980-12-30—Публикация

1978-06-19—Подача