t

Изобретение относится к цифровой бработке сигналов, в частности, к ифровой фильтрации, и может быть cnojibsoBaHO, например в цифровых анализаторах спектра.

Известен цифровой корреляционный фильтр, содержащий аналого-цифровой преобразователь (АЦП), блок первичного интегрирования, состоящий из двух квантователей опорного сигнала, вух квадратурных каналов, каждый из которалх состоит из последовательно соединенных умножителя и накапливающего сумматора и цифрового сумматора, перемножитель, запоминающий блок, блок вторичного интегрирования в виде выходного накапливающего сумматора, реверсивный счетчик и синхронизатор HI .

Однако известный цифровой фильтр не предназначен для многоканальной обработки нескольких сигналов. В случае же использования известного фильтра для многокангшьной обработки нескольких независи влх сигналов, его необходимо существенно усложнять путем использования большого числа накапливающих сумматоров и умножителей ,

Известен также цифровой фильтр, содержащий аналого-цифровой преобразователь, выходы которого соединены со входами п основных блоков интегрирования, а управляющий вход с выходом задающего генератор ар .

Однако это устройство имеет более низкую избирательность за счет наличия боковых лепестков в частотной

0 характеристике.

Цель изобретения - повышение избирательности .

Поставленная цель достигается тем, что в устройство для цифровой корреляционной фильтрации, содержащее аналого-цифровой преобразователь, выходы которого соединены со входами п основных блоков интегрирования, а управляющий вход - с выходом задающе0го генератора, введены синтезатор опорных частот, коммутаторы стробов и адресов, делитель частоты, формирователь стробов, элемент сдвига,инвертор, триггеры весовой функции и

5 знака весовой функции и дополнительный блок интегрирования, состоящий нз последовательно соединенных суммагора, регистра и оперативного запоминающего устройства, выход которого

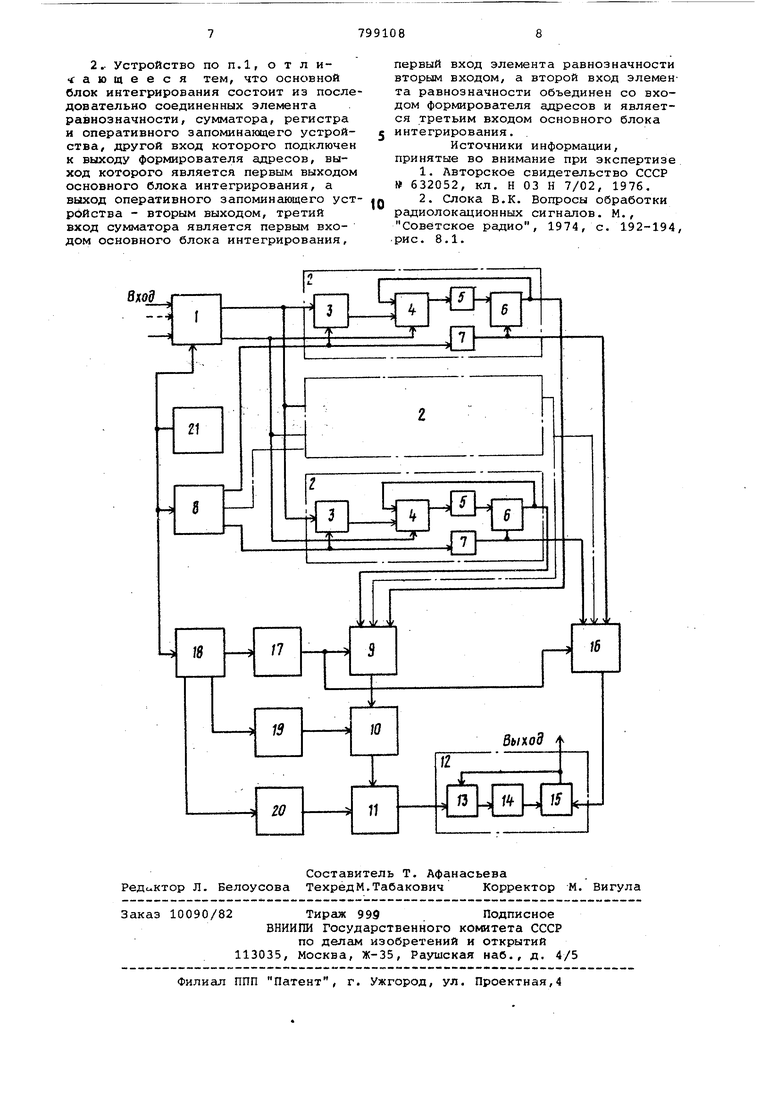

D соединен с другим входом сумматора. при этом ко входу синтезатор опорны частот подключен выход задакхцего ген ратора, а к выходам - третьи входы основных блоков интегрирования,первый и второй выходы каждого из которых соединены со входами соответственно коммутатора адресов и коммутатора стробов, ко входу делителя частоты подключен выход задакяцего генератора, к первому выходу через формирователь стробов - управляющие входы коммутаторов стробов и адресов, ко второму выходу через триггер весовой функции - управляющий вход элемента сдвига, а к третьему выходу через триггер знака весовой функции управляющий вход инвертора, сигнешьный вход которого через элемент сдви га соединен с выходом коммутатора стробов, а выход - с первым входом дополнительного блока интегрирования второй вход которого подключен к выходу коммутатора адресов, а также то что основной блок интегрирования сос тоит из последовательно соединенных элемента равнозначности, сумматора, регистра и оперативного запоминакяцег устройства, другой вход которого под ключен к выходу формирования адресов выход которого является первым выходом основного блока интегрирования, а выход оперативного запоминающего устройства - вторым выходом, третий вход сумматора является первым входо основного блока интегрирования,первый вход элемента равнозначности вторым входом, а второй вход элемент равнозначности объединен со входом формирователя адресов и является третьим входом основного блока интег рирования. На чертеже представлена структурная электрическая схема устройства для корреляционной фильтрации. в устройстве сигнальные входы аналого-цифрового преобразователя (АЦП) 1 являются входами устройства выходы АЦП1 подключены к соответствующим входам п блоков 2 интегрирования, каждый из которых содержит элемент 3 равнозначности, соединенны в кольцо сумматор: 4, регистр 5, оперйтивное запоминающее устройство (ОЗУ) б и формирователь 7 адреса, Подключенный выходом к адресному входу оперативного запоминающего устройства б. Знаковый выход аналого-цифрового преобразователя 1 подключен к первому входу элемента 3 равнозначности, а числовой выход к числовому входу сумматора 4, ко второму входу элемента 3 равнозначности, соединенному со входом формирователя 7 адреса, подключен соответствующий выход синтезатора 8 опо ных частот, а вЕзкод элемента 3 равнозначности подключен к знаковому входу сумматора 4. Выходы ОЗУ 6, являющиеся выходами блоков 2 интегрирования, связаны через последовательно включенные коммутатор 9 стробов, элемент 10 сдвига и инвертор 11 с дополнительным блоком 12 интегрирования, содержащим, соединенные в кольцо сумматор 13, регистр 14 и оперативное запоминающее устройство (ОЗУ) 15. Выходы формирователей 7 адреса связаны через коммутатор 16 адресов с адресным входом ОЗУ 15, выход которого является выходом устройства. С управляккцими входами коммутаторов 9 и 16 стробов и адресов связа« через формирователь 17 стробов первый выход делителя 18 частоты, второй и третий вькоды которого через триггеры 19 и 20 весовой функции и знака весовой функции соответственно связаны с управляющими входами элемента сдвига и инвертора 11. Управляющий вход аналого-цифрового преобразователя 1 и входы синтезатора 8 опорных частот и делителя 18 частоты соединены с выходом задающего генератора 21. Устройство работает следующим образом. Поступающие на вход устройства независимые сигналы в АЦП1 квантуются по амплитуде и во времени и подаются на п блоков 2 интегрирования, настроенных на различные частоты. Квантование во времени осуществляется сигналами задающего генератора 21 с достаточно высокой частотой, пригодной для работы всех п блоков 2 интегрирования, и таким образом, что в течение периода квантования на выходе АЦП 1 последовательно формируются квантованные по амплитуде значения всех входных, сигналов. Сигнал на выходе АЦП 1 формируется в виде знака на знаковом выходе и числа - на числовом выходе. Эти сигналы поступают в блоки 2 интегрирования. Знаки сигналов с АЦП 1 поступают на элементы 3 равнозначности , на вторые входы которых поступают знаковые сигналы опорных частот с соответствующих выходов синтезатора 8 частот. Получающееся при этом произведение полярностей с выхода элемента 3 равнозначности поступает на знаковый вход сумматора 4. При этом на числовой вход сумматора 4 поступает значение с числового выхода АЦП 1. Одновременно формироват1 ль 7 адреса под воздействием сигнала синтезатора 8 опорных частот формирует адрес соответствующей ячейки ОЗУ 6, с выхода которой сигнал поступает на второй вход сумматора 4. Результат сложения в сумматоре 4 представляет собой промежуточный результат интегрирования и записывается в регистр 5 и затем переписывается в ОЗУ б в ту же ячейку на место

предьвдущего промежуточного результата. Интервал времени между получением предыдущего и последующего промежуточного результата интегрирования, называемый периодом обработки, определяется частотой опорного сигнала и выбирается в два раза меньшим периода опорного сигнала. В связи с тем, что каждый сигнал в блоке 2 интегрирования обрабатывается раздельно с синусной и косинусной составляющими опорного сигнала, число ячеек в ОЗУ б каждого блока 2 интегрирования в два раза превьаиает число входных сигналов. Каждая-ячейка соответствует одному квадратурному каналу одного из входною сигнала. За один период обработки обновляются все промежуточные результаты интегрирования. Все входные сигналы в блоке 2 интегрирования обрабатываются аналогично предлагаемому выше со сдвигом во времени на часть периода обработки,необходимую для обработки предшествующего сигнала.

С выходов ОЗУ 6 абсолютные значения сигналов (без знака) поступают на коммутатор 9 стробов. Работа коммтатора 9 строЬов тактируется стробируквдими импульсами с формирователя 17 стробов. Каждый строб пропускает на вход элемента 10 сдвига сигналы с выхода только одного из блоков 2 интегрирования. В элементе 10 сдвига в зависимости от состояния триггера 19 весовой функции сигналы либо удваивают свою величину (сдвигаются на разряд в сторону старших разрядов), либо проходят без изменения на иирсртор 11, где в зависимости от состояния триггера 20 знака весовой функции либо инвертируются, либо без , изменения полярности проходят на блок 12 интегрирования,где поступают на вход сумматора 13. Одновременно со стробированием коммутатора 9 стробов формирователь 17 стробов управляет также коммутатором 16 адресов , с выхода которого сигналы соответствующего формирователя 7 адреса поступают на адресный вход ОЗУ 15. При этом на выходе ОЗУ 15 формируется промежуточный результат вторичного интегрирования соответствующего сигнала, который поступает на второй вход сумматора 13. На выходе сумматора 13 формируется новый промежуточный результат, являкхдийся суммой сигналов на выходах сумматора 13. Новый промежуточный результат вторичного интегрирования записывается в регистр 14 и затем в ОЗУ 15 в ту же ячейку вместо предыдущего промежуточного результата вторичного интегрирования. Каждой паре ячеек ОЗУ б блока 2 интегрирования, хранящей промежуточные результаты интегрирования одного из входных сигналов в

двух квадратурных каналах, соответствует одна ячейка ОЗУ 15 блока 12 интегрирования. Поэтому сигнал, хранящийся в ячейке ОЗУ 15, является результатом объединения и вторичного интегрирования выходных сигналов двух ква,цратурных каналов блока 2 интегрирования. Общее количество ячеек в ОЗУ 15 равно произведению числа обрабатываемых сигналов на число частотных каналов, в которых обрабатывается каждый сигнал.

Задающий генератор 21 управляет работой синтезатора 8 опорных частот 1 делителя 18 частоты, который, в

5 свою очередь, управляет работой формирователя 17 стробов и состоянием

триггеров 19 и 20 весовой функции

и знака весовой функции.

20

Формула изобретения

1. Устройство для цифровой корреляционной фильтрации, содержащее

аналого-цифровой преобразователь, выходы которого соединены со входами п основных блоков интегрирования, а управляющий вход - с выходом задающего генератора, о тличающееся тем, что, с целью повышения избирательности, в него введены синтезатор опорных частот, коммутаторы стробов и адресов, делитель частоты, формирователь стробов, элемент сдЬига, инвертор, триггеры весовой функции и знака весовой функции и дополнительный блок интегрирования, состoяttц й из последовательно соединенных сумматора, регистра и оперативного запоминающего устройства, выход которого соединен с другим входом сумматора, при этом ко входу синтезатора опорных частот подключен выход задающего генератора, а к

выходам - третьи входы основных блоков интегрирования, первый и второй выходы каждого из которых соединены со вxoдa tи соответственно коммутатора адресов и коммутатора стробов, ко входу делителя частоты подключен выход задающего генератора, к первому выходу через формирователь стробов - управляющие входы коммутаторов стробов и адресов, ко втором- выходу через триггер весовой функции - управляющий вход элемента сдвига, а к третьему выходу через триггер знака весовой функции - управляющий вход инвертора/ сигнальный вход которого через элемент сдвига соединен с выходом коммутатора стробов, а выход с первым входом дополнительного блока интегрирования, второй вход которого подключен к выходу коммутатора адресов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор спектра | 1985 |

|

SU1318925A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| Арифметическое устройство для цифровой фильтрации с автоматической регулировкой усиления | 1979 |

|

SU881987A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

Авторы

Даты

1981-01-23—Публикация

1978-06-19—Подача