вместе со входом блока синхронизации подсоединен ко входу устройства 2.

Недостатком устройства является относительно низкая ломехоустойчи-.. вость, так как для передачи информации используется код Хэминга, позволяющий обнаружение сбоев одного или двух символов в коде, а сбои трех , четырех и т.д. символов не обнаруживаются. Причем необнаруживаемые сбои могут быть как в младших, так и в старших разрядах кода информации,что приводит к большим погрешностям.

Цель устройства - повышение его помехоустойчивости.

Поставленная цель достигается тем что в устройство для приема информации в каждый информационный канал введены блок вычитания, блок умножения, блок выделения максимума,блок сравнения,элемент ИЛИ и счетчик,выход блока памяти соединен с первым входом блока вычитания,выход которого соединен с первым входом блока сравнения и с первым входом блока выделения макси 1«ума, выход которого соединен с первым входом блока умножения, выход которого соединен со вторым входом блока сравнения, первый выход блока сравнения соединен с третьим входом элемента И и первым входом счетчика, выход которого соединен со вторым входом блока умножения, второй, выход блсЗка сравнения соединен с первым входом элемента ИЛИ, выход которого соединен со вторым входом счетчика,второй выход которого соединен со вторым входом блока выделения максимума, выходы распределителя соединены со вторыми входами блоков вычитания, третьи входы которых объединены и подключены к выходу блока промежуточной памяти, третий выход дешифратора соединен со вторыми входами элементов. ИЛИ информационных каналов.

В связи с этим сбои, которые не обнаруживаются с помощью помехозащищенного кода и уровень которых больше уровня обнаружения, не будут записаны в блок памяти.

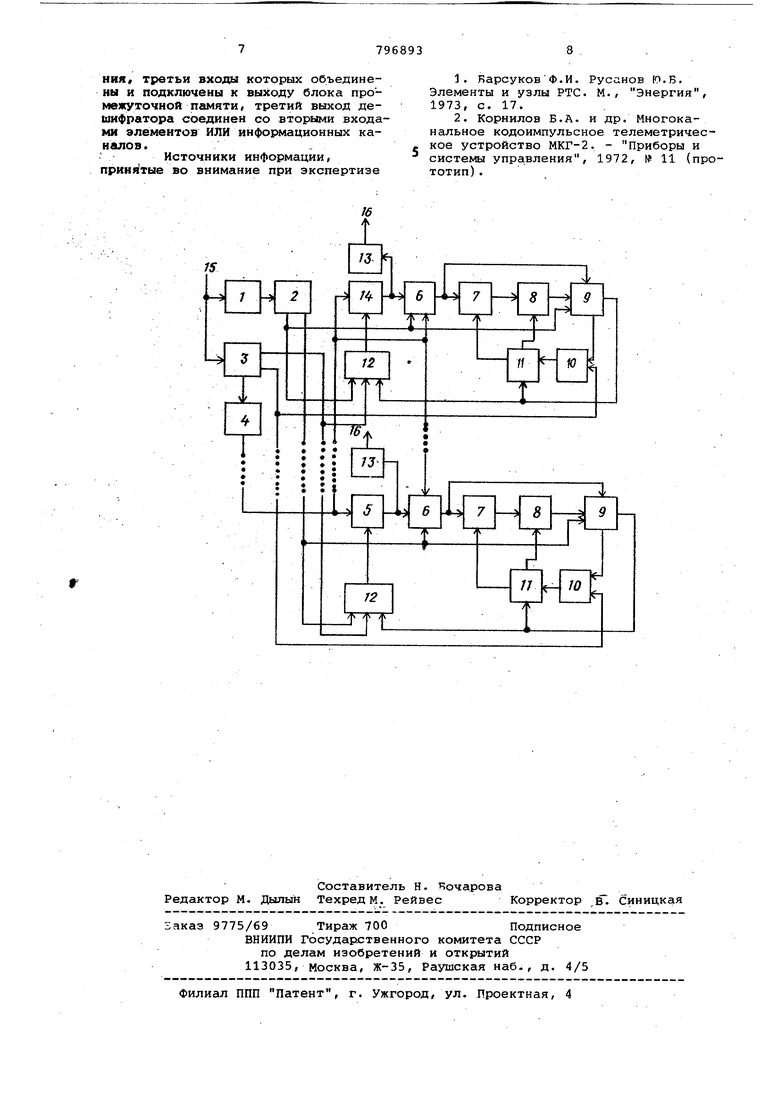

На чертеже приведена блок-схема устройства.

Устройство для приема информации содержит блок 1 синхронизации, распределитель 2, дешифратор 3, блок 4 промежуточной памяти (БПП), а также в каждом информационном канале 5 содержит блок б вычитания, блок 7 выделения максимума, блок 8 умножения блок 9 сравнения, элемент 10 ИЛИ, реверсивный счетчик 11, элемент 12 И, цифроаналоговый преобразователь 13, блок 4 памяти, вход 15 устройства, выходы 16 устройства. Блок 1 синхронизации служит для выделения синхроимпульсов и обеспечения синхронной работы распределителя 2 передающей и распределителя приемной

стороны (на чертеже не показан). Распределитель 2 формирует на своих выходах управляющий единичный импульс, последовательно сдвигающийся в соответствии с тактовой частотой от блока 1 синхронизации. Дешифратор 3 осуществляет проверку принятого кода информации и обнаруживает слои одного.и двух символов за счет избыточности кода. При обнаружении сбоя формируется единичный импульс на втором (управляющем) выходе дешифратора, если сбоя нет, иди он не обнаружен (так как сбиты три и более символа), то сигнал 1 формируется на третьем (управляющем) выходе. На пятом (информационном) выходе дешифратора 3 формируется код отсчета..г Блок 4 промежуточной памяти предназначен для оперативного запоминания кода отсчета (на время одного такта) Блок 14 памяти предназначен для запоминания кода на его входе,причем момент запоминания соответствует появлению сигнала 1 на его первом (управляющем) входе. Блок б вычитания осуществляет вычитание кодов на двух своих входах и формирует код разности на своем выходе при наличии разрешающего сигнала 1 на его втором (управляющем) входе. Блок 8 умножения осуществляет операцию умножения входных кодов и формирует результат на своем выходе. Блок 9 сравнения предназначен для сравнения на двух своих входах, при наличии разрешакяцего сигнала 1 на его третьем (управляющем) входе , и если код на первом его втором входе (от блока 8) больше (меньше) кода на первом его входе (от блока 6) то на первом его выходе формируется сигнал 1 (О), а второй выход является инверсным к первому. В случае сигнала О на управляклцем входе на обоих выходах. Элемент ИЛИ 10 и элемент и 12 выполняют соответствующие логические операции. Реверсивный счетчик 11 предназначен для подсчета числа единиц, поступивших на первый вход в прямом коде (т.е. для суммирования), и в инверсном коде (вычитания) импульсов, поступивших на .второй вход. На первом выходе счетчика 11 формируется код результата суммирования (вычитания). Исходное состояние счетчика должно соответствовать единице. Кроме того, на втором выходе счетчика 11 формиесли выходной

руется сигнал

код счетчика соответствует единице, в противном случае - О. Цифроаналоговый преобразователь 13 служит для формирования аналогового напряжения на выходе, соответствунхцего коду на входе.

Устройство для приема информации работает следующим образом.

Из входной информации Б блоке 1 формируются тактовые импульсы,управляющие .работой распределителя 2, а в дешифраторе 3 осуществляется проверка принятого помехозащищенного кода, с помощью которой выявляются сбои одного или двух символов.При , обнаружении сбоя на одном выходе дешифратора 3 формируется запирающий сигнал который поступает на вход всех элементов И 12, благодаря этому записи кода данного отсчета в блоке 14 не произойдет. Кроме того, на другом выходе дешифратора 3 формируется управляющий сигнал 1, кото.рый пройдет .через соответствующий элемент ИЛИ 10 на второй вход реверсивного счетчика 11, последний при этом изменит свое состояние на единицу, и на управляющем (втором) входе блока 7 возникает (или же сохранится) запрещающий сигнал 1.Если же в дешифраторе 3 не произошло овнаружения сбоя, то на втором управляющем его выходе образуется разрешающий сигнал 1, на первом управляющем выходе - сигнсш О, и код отсчета через блок 4 пройдет на входы всех блоков 4 и 6. В блок 6 каиала, по которому пришел отсчет (блок 6 и 9 стробируются сигнгшами от распределителя 2), определяется разность между пришедшие, отсчетом и предьщущим (последний хранится в памяти дан ного блока 5): . Код, соответствующий этой разности, поступает на вход блока 9 данногр канала и сравнивается с допустимой разностью, которая вычисляется в блоке 8 как uXjj nuXfn, где - максимальное изменение сигнала за такт дискретизации при нулевой экстраполяции, п - кратность сбоев отсчетов, величина ziXv« вычисляется в блоке 7 отдельно для каждого канала, так как эта величина зависит от свойств телеметрируемого сигнала, причем лХуу, определяется только из тех приращений сигнала за такт дискретизации, которые соответствуют разности двух соседних принятых отсчетов, в других случаях на управляющем входе блока 7 запрещающий сигнал О. Величину необходимо умножить на п с тем, чтобы не забраковать несбитый отсчет после п подряд сбитых отсчетов. Кроме того, после каждого принятого отсчета , состояние счетчика 11 уменьшается на единицу. Если ЛХ:,- &Х, то на втором выходе блока -9 формируется сигнал 1, который через элемент ИЛИ 10 поступит на вход реверсивного счетчика 11, последний изменит свое состояние на единицу, а на первом выходе блока 9 формируется запрещающий сигнал О, который закрывает элемент 12 И, вследствие чего записи кода отсчета в блок 5 не последует, т.е. произойдет обнаружение сбоя трех или большего числа символов в коде отсчета. Если л. -i ЛХото на втором выходе блока 9 формируется сигнал О, а на первом выходе формируется разрешающий сигнал 1, благодаря этому произойдет запись -информации в блок 6 и выходной код .реверсивного счетчика 11 уменьшится на единицу.

Таким образом, в предлагаемом уст,. ройстве происходит обнаружение сбоев одного или двух разрядов кода отсчета (благодаря избыточному коду) и обнаружение сбоев трех и более разрядов, вес которых больше АХ&,т.е. помехоустойчивость устройства повышается.

Формула изобретения

0

Устройство для приема информации, содержащее блок синхронизации, вход которого соединен со входом устройства и входом дешифратора, первый выход которого соединен со входом блока промежуточной памяти, выход

5 блока синхронизации соединен со входом распределителя, И в каждом информационном канале блок памяти, выход которого соединен со входом цифроансшогового преобразователя, выход

0 которого соединен с выходом устройства, и элемент И, выход которого соединен с первым входом блока пггмяти, выходы распределителя соединены с первыми входами элементов И всех информационных каналов, вторые входы которых объединены и подключены ко второму выходу дешифратора, выход блока промежуточной памяти соединен с объединенными, вторыми входами бло0ков памяти всех информационных каналов, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в каждый информационный канал введены блок вычитания, блок умножения, блок выделения максимума, блок чзравнения, элемент ИЛИ и счетчик, выход блока памяти соединен с первым входом блока вычитания, выход которого соединен с первым входом блока сравнения и с первым входом блока выделения максимума/ выход которого соединен с первым входом блока умножения, выход которого соединен со вторым входом блока сравнения, первый выход блока сравнения соединен с третьим входом элемента.И и первым входом счетчика, выход которого соединен .со вторым входом блока умножения, второй выход блока сравнения соединен с первым входом элемента ИЛИ, выход которого соединен со вторым входом счетчика, второй выход которого соединен со вторым входом блока выделения максимума, выходы распределителя соединены со вторЕлми входами блоков вычитания, третьи входы которых объединены и подключены к выходу блока промежуточной пгиияти, третий выход дешифратора соединен со вторыми входами элементов ИЛИ информационных каналов.

Источники информации, приня(тые во внимание при экспертизе

1.БарсуковФ.И. Руссхнов Ю.Б. Элементы и узлы РТС. М., Энергия, 1973, с. 17.

2.Корнилов Б.А. и др. Многоканальное кодоимпульсное телеметрическое устройство МКГ-2. - Приборы и системы управления, 1972, № 11 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемное устройство телеизмери-ТЕльНОй СиСТЕМы | 1979 |

|

SU805382A1 |

| Линейный интерполятор | 1979 |

|

SU842914A1 |

| Приемное устройство телеизмерительнойСиСТЕМы | 1979 |

|

SU842915A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Приемное устройство телеизмерительной системы | 1978 |

|

SU771698A1 |

| Приемное устройство телеизмерительной системы | 1977 |

|

SU714457A1 |

| Адаптивный амплитудный анализатор | 1982 |

|

SU1078435A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство для вычисления структурной и интервальной функций | 1984 |

|

SU1166135A1 |

Авторы

Даты

1981-01-15—Публикация

1979-02-08—Подача