I

Изобретение относится к эапоминак щнм устройствам.

Известно устройство для записи и контроля программируемых блсясов постоянной памяти, содержащее регистры, задающий генератор, формирователи сигналов и схему сравнения 13 .

Недостатком этого устройства является невысокое быстродействие.

Наиболее близким к изобретению по своему решению является устройство для записи и контроля программируемых блоков постоянной памяти, содержащее ре- гистр текущего адреса и регистр данных,

одни из входов которых подключены к Bbf

ходам задающего генератора и блсжа оперативной памяти, а выходы - соответст венно к первым входом формирователя адресных счгналов и формирователя сигналов данных, компаратор конечного адреса, входы которого соединены с (исходами регистра конечного адреса ir регистра текущего адреса, компаратор выходг ых данных, один ив входов KOTiipoio подключен ко

вхсау устройства, а другие входы соединны с выходами регистра данных и блсжа оперативной памяти, один из входов которого подключен к выходу счетчика, и блок управления ,

Недостатком этого устройства является отсутствие универсальности при работе с разнотипными программными блсжами памяти, что сужает область применения устройства.

Цель изобретения - расщиренне области применения устройства за счет обеспечения возможности записи я конт родя разнотипных блсков памяти.

Поставленная цель достигается том, что устройство содержит блок аналоговой памяти, ключи, цкфроаналоговый преобразователь, дещифратор, дополнительны блс« оперативной памяти и счетчик, формирователь синхросигналов и блок программируемых синхросигналов, причем входы блока аналоговой памяти соедино- ны с выходами ключей, выходы - со вторыми входами формирователя адре(-:ги,|х

сигналов и формирователя сигналов данны и первым входом формирователя синхросигналов, второй вход которого подключен к выходу блсжа программируемых синхроимпульсов и другим входам регистр ра текущего адреса и регистра данных, а выход к одному иа выходов устройства, выходы дешифратора и цифроаналогового преобразователя соединены со входами ключей, а входы - соответственно с выходами дсяюлнительного счетчика я дополнительного блока оперативной памяти, первый вход которого подключен к выходу дополнительного счетчипка, выход блсжа управления соединен со входом дополнительного счетчика, вторым входом дополнительного блока оперативной памяти и одним из входов блока программируемых синхроимпульсов, другой вход которого подключен к выходу задающего генератора.

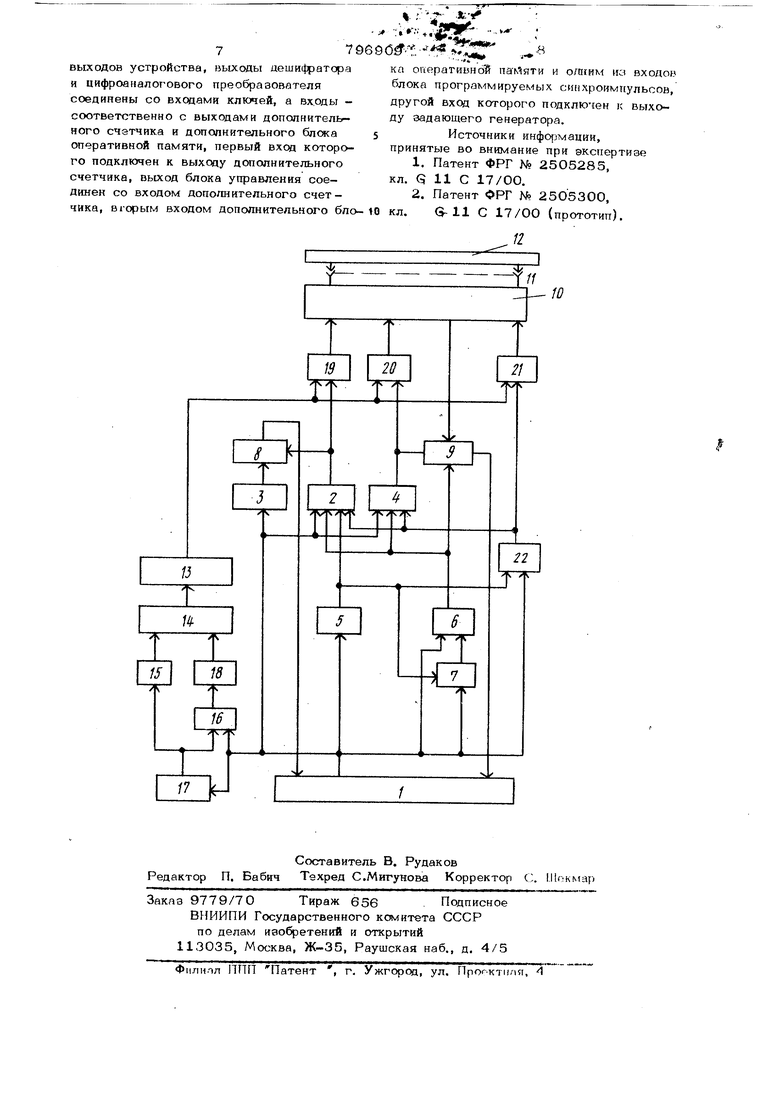

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит блок 1 управления, регистр 2 текущего адреса, регистр 3 конечного адреса, регистр 4 данных, задающий генератор 5, блек 6 оператив- ной памяти, счетчик 7, компаратор 8 конечного адреса, компаратср 9 данных. Входы и выходы устройства подключают ся к выходам и входам индивидуального модуля 10, который через контакты 11 соединяется с программируемым блсжом 12 постоянной памяти.

Устройство также содержит блок 13 аналоговой памяти, ключи 14, дешифратор 15, дополнительныеблдк 16 оперативной памяти и счетчик 17, цифроаналоговый преобразователь 18, формиро ватель 19 адресных сигналов, формирователь 20 сигналов данных, формирователь

21синхросигналов, блок 22 программируемых синхросигналов,

Выходы регистров 2 и 4 подключены к первым входам формирователей 19 и 20 соответственно. Один из входов 6 соединен с выходом счетчика 7, Входы блсжа 13 соединены с выхода- .ма ключей 14, а выходы - со вторыми входами формирователей 19 и 20 и первьлм входом формирователя 21, второй BXOQ которого подключен к выходу блока

22н другим входам регистров 2 н 4, а выход - к одному из выходов устройства

Выходы дешифратора 15 а преобразователя 18 соединены со входами ключей 14, а входы - соответственно с выходам 1счетчика 17. Выхса блока 1 соединен со вхсяом счетчика 17, вторым входом блока 16 и одним из входов блока 22, другой вход которого подключен к выходу задающего генератора 5„

Устройство работает следующим образом.

К модулю 10 через контакты 11 пспключается программируемый блок 12 поо тоянной памяти.

И а блока i в соответствии с программой вхоцного контроля необходимая инфорк ация заносится в блок 16 для зада НИИ величины верхних и нижних границ импульсов формирователей 19, регистров 3 и 4 с целью определения начала и

конца контроля, в блок 22 для выбора номера канала, задержки и длительности импульсов синхронизации, в задающий генератор 5.

По команде из блока 1 в соответстВИИ с .временной диаграммой работы блока 12-блок 22 программируемых синхроимпульсов выдает сигналы на индивидуальный модуль 10, на регистры 2 и 4, По первоначальному адресу, записанному в регистре 2, информация считывается из блока 12 на компаратор 9, где идет сравнение с содержимым регистра 4. Положительный результат сравнения позволяет добавить единицу в регистр

2 с периодсум, определяемым задающим генератором 5. Отрицательный результат сравнения поступает в блек 1 и 8апреща ет добавление единицы в регистр 2. При сравнении содержимого регистра 2 с содержимым регистра 3 в блок 1 проходит команда Годен.

Формирование величин верхних и нижних границ импульсов формирователей 19. 21 происходит автономно после записи в блок 16 последнего слова. Счетчик 17 тактируется собственным внутренним ге- нераторсм. Каждое состояние счетчика 17 расшифровывается дешифратором 15 в позиционный йод и вызывает считывание соответствующего слова в виде двоичноьго кода из блока 16.

Двоичный код каждого слова из блока 16 преобразуется цифроаналоговым преобразователем 18 в аналоговый сигнал. Этот сигнал черев отсрытый соответсгвующим позиционным кодом дешифратора 15 ключ 14 поступает и запоминается в блоке 13. С выходов блока 13 соответствующие сигналы напряжения поступают на формирователи 19-21. Этими напряжениями подготавливаются к работе формирователи 19-21.

После подготовки формирователей 19- 21 с регистра 2 на формирователь 19 последовательно поступают кеды адресов ячеек программируемого блсжа 12. Они, преобразовываясь формирователем 19 адреса в необхсщймую форму, пос-1упают на адресные входы бпска 12. С кодом каждого адреса блсжа 12 выдается управляющий сигнал бпокам 22, Этот сир нал через формирователь 21 также посту .пает на соответствующие входы блока 12 По кажцому адресу происходит считывание инффмации выбранной ячейки, блока 12 и сравнение втой информапии с первоначально записанной в регистре 4 компаратором 9. Так продолжается до тех пор, пока код регистра 2 не сравнится с кодом регистра 3 компараторсм 8. Компаратор 8 выдает в блок 1 соответст вующий сигнал. Цикл входного контроля работоспособности блока 12 заканчивается. После проведения входного функпионального контроля выпопняется программирование в соответствии с таблицей истинности, занесенной в блок 1. С втсй цепью после занесения требуемой информации и подготовки к работе формирова тепей 19-21 аналогично описанному выш с регистра 4 на формирователь 20 сик- хрояно с каждым адресом nocTjmaeT ин формация, в соответствии с которой прО исходит электрическое программирование блока 12. Отличия режима программирования от режима входного контроля следующие. Добавление единицы в регистр 2 проводится по команде из блока 1, а не из задающего генератора 5. Оакн из каналов синхронизации выбирается для организации паувы посяе прор раммирования, в режиме; программирован в течение паузы проводится контрсшь правильности программирования в аавис мости от типа блока 12 после каждого бита или всего слова, Задающий генератор 3 необходим толь ко для организации синхроимпульсов в паузы в блоке 22. Режим программирования выполняется как и в первом случае до тех пор, пока код регистра 2 не станет равным коду регистра 3. После окончания режима программирования проводится режим выходного функ ционального контроля. Отличие режима выходного контроля от входного состоит в том, что ожидаемая информация для сравнения при считывании на блсжа 12 на компаратор 9 поступает из бпсжа 6, в который предварительно была занесена из блсжа 1, добавление единицы в счет чик 7 и регистр 2 идет синхронно по сигналу иа генератора 5 с частотой пре дельной для конкретного типа блсжа l2f если объем памяти блока 6 меньше памяти блсжа 12, то режим выходного фугжционального контроля повторяется несколько раз, при ВТОМ последовательно увеличивается содержимое регистра 2, Окончание выходного функционального контроля проводится так же .по содержимому регистра 3. Описанное устройство является более . универсальным по сравнению с известнь -ми, а также отличается повышенной наде жностью и точнсютью работы. Формула изобретения Устройство для записи и контроля программируемых блоков послоянной памяти, содержащее регистр текущего адреса и регистр данных, одни из входов которых подключены к выходам эадаго щего генератора и блсжа оперативной па-мяти, а выходы - соответственно к первым выходам формирователя адресных сигналов и формирователя сигналовданйь,1г, компаратс конечного -адреса, входы которого соединены с выходами регнсп-ра конечного адреса к регистра текущего адреса, компаратор данных, один из входов которого подключен ко входу устройства, а другие входы соединены с выходами регистра данных и блока оперативной памяти, один из входов которого подключен к выходу счетчика, и блок управления, отлича ющее ся тем, что, с целью расширения области npta eнения устройства за счет обеспечения возможносгти . записи и контроля разнотип« ных блоков памяти, оно содержит блок анайоговсй памяти, ключи, цифроаналого вый преобразователь, дешифратор, ДОпси- нительные бпсж оперативной памяти и счетчик, формирователь синхросигналов и блок программируемых синхросигналов причем входы бпсжа аналоговой памяти соединены с выходами ключей, а выхо ды со вторыми входами формирователя адресных сигналов в формирователя сигналов данных и первым входсы формирователя сннхросигналов, второй вход которого подключен к выходу бЬсжа програм мкруемых синхроимпульсов и другим входам регисл-ра текущего адреса и регнстр а данных, а выход - к однся у ив выходов устройства, выходы дешифратора и цифроаналогового преобразователя соедипены со вхонами ключей, а входы - соответственно с выходами дополнительного счэтчика и дополнительного блока оперативной памяти, первый вход которо го подключен к выходу дополнительного счетчика, выход блока управления соединен со входом доаолнительного счетчика, вторым входом дополнительного бло- 10 кл.

. n

(3-11 С 17/00 (прототип). Л

J

ж

/f

W .- « , т -Jf -. 4F.)--t- кп оперативной naNlgTH и о/пшм на входов блока программируемых синхроимпульсов, другой вход которого подключен к выходу задающего генератора. Источники инфо змации, принятые во внимание при экспертизе 1.Патент ФРГ № 2505285, кл. Q 11 С 17/00, 2.Патент ОРГ № 2505300,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и контроля программируемых блоков постоянной памяти | 1978 |

|

SU911613A2 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| ПРОГРАММАТОР | 1991 |

|

RU2078381C1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для программного управления технологическими процессами | 1979 |

|

SU877476A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

Авторы

Даты

1981-01-15—Публикация

1978-01-20—Подача