Изобретение относится к области автоматики и вычислительной техники и. предназначено для использования в средствах, вычислительной техники (СВТ) при решении задач по защите информации и идентификации пользователя.

Цель изобретения - повышение надежности защиты средств вычислительной техники (СВТ) от несанкционированного доступа за счет введения многоуровневого алгоритма идентификации.

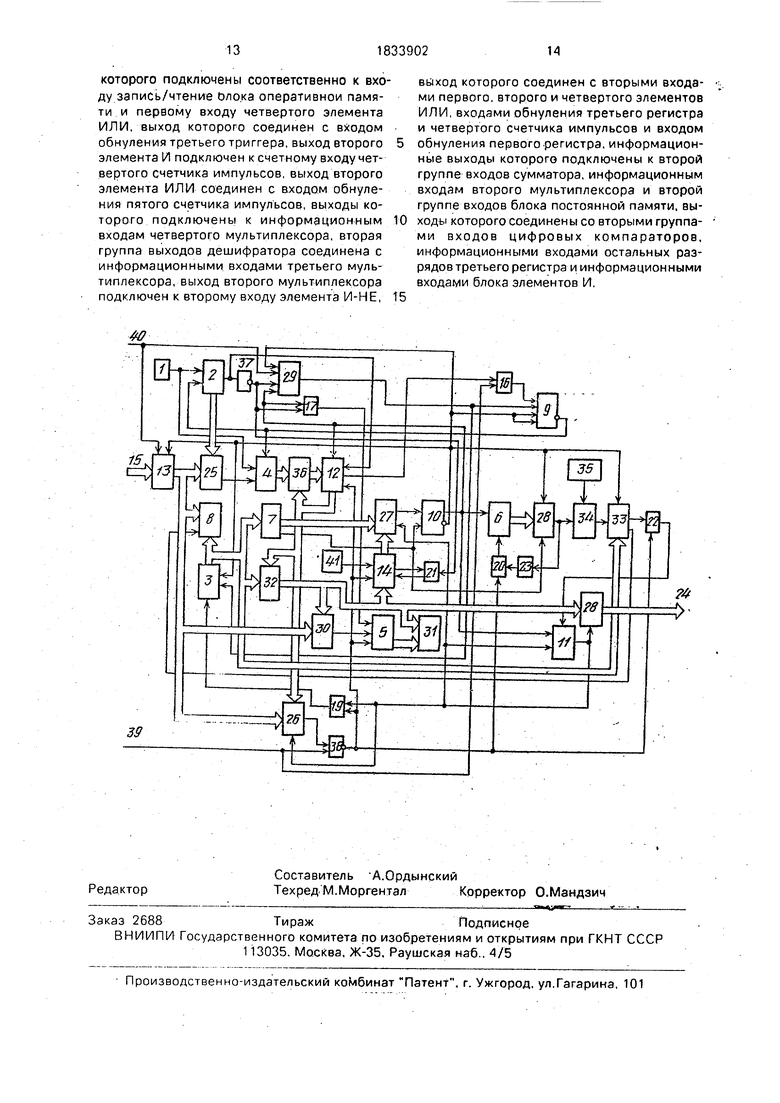

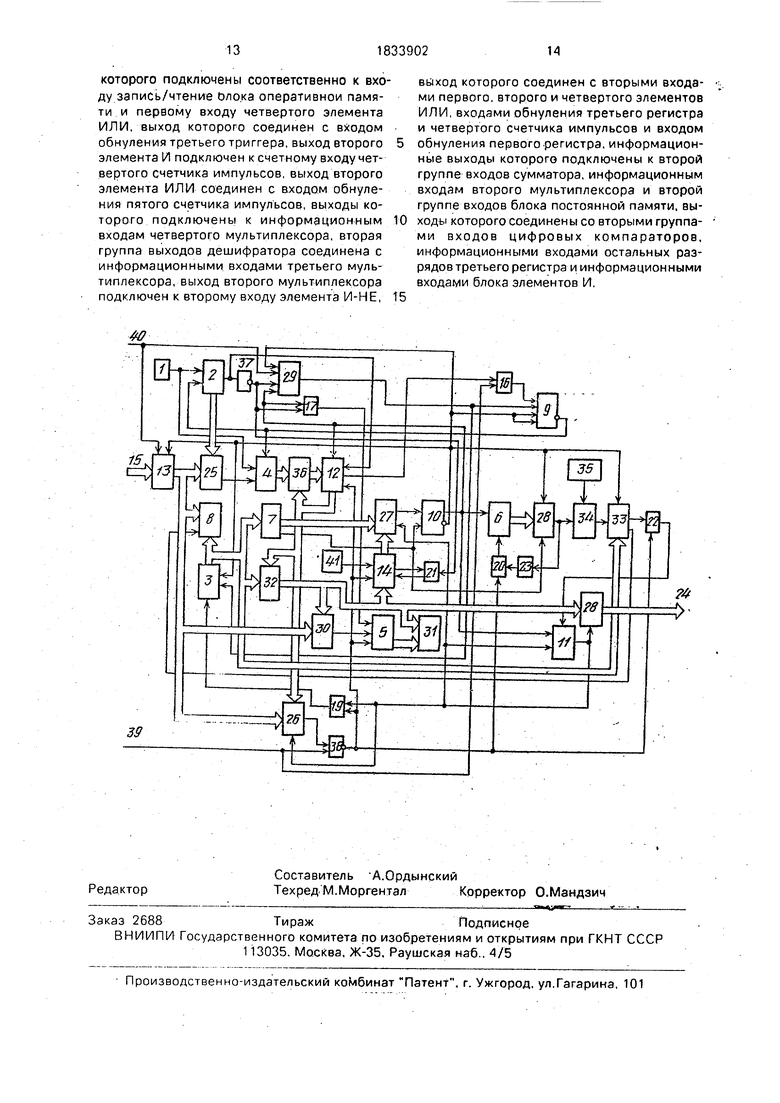

На чертеже представлена структурная схема устройства.

Устройство контроля и. идентификации пользователя содержит генератор 1 тактовых импульсов, первый 2, второй 3, третий 4, четвертый 5 и пятый 6 счетчики импульсов, дешифратор 7, блок 8 оперативной памяти., первый 9, второй 10 и третий 11 триггеры;, первый 12, второй- 13 и третий 14 регистры, информационный вход 15 устрой- ства, первый 16 и второй 17 элементы И, блок 18 элементов И, первый 19, второй 20, третий 21 и четвертый 22 элементы ИЛИ, элемент задержки 23, информационный выход 24 устройства, первый 25, второй 26, третий 27, четвертый 28 и пятый 29 мультиплексоры, первый 30 и второй 31 цифровые компараторы, блок 32 постоянной памяти, блок 33 программируемой памяти, ключевой элемент 34, источник 35 напряжения перепрограммирования, сумматор 36, элемент НЕ 37, элемент И-НЕ 38, вход 39 СБРОС, вход 40 синхронизации, источник 41 логической единицы.

00 00 СА Ю О ГО

Генератор 1 тактовых импульсов предназначен для генерации непрерывной импульсной последовательности.

Первый 2 счетчик совместно с первым 25 мультиплексором предназначены для побитового просмотра информационных посылок, поступающих со второго 13 регистра. Второй.13 регистр предназначен для промежуточного хранения информативных посылок пароля и признаков пользователя. Группа элементов, состоящая из первого 25 мультиплексора, третьего 4 счетчика, сумматора 36 и первого 12 регистра, выполняет функцию преобразователя кодовой последовательности пароля пользователя в количественную оценку, числа логических О для определения области памяти СВТ, предназначенной для конкретного пользователя.

Второй 3 счетчик выполняет функцию формирователя адресов при накоплении в блоке 8 оперативной памяти входной информации и последующем контроле и идентификации пользователя.

Дешифратор 7, второй 26 мультиплексор, третий 14 регистр и логический элемент ИЛИ 21 предназначены для распределения коммутативной информации, определяющей длину числовой последовательности пароля пользователя.

Третий 27 мультиплексор, первый 19 элемент ИЛИ и элемент И-НЕ 38 предназначены длл формирования сигналов установки устройства в исходное состояние по сигналу СБРОС на входе 39 устройства или коду числа по завершении работы пользователя и передачи СВТ другому пользователю.

Блок 32 постоянной памяти предназначен для хранения кодовых структур паролей пользователей СВТ.

Первый 30 и второй 31 цифровые компараторы, четвертый 5 счетчик и второй 10 триггер предназначены для реализации режима контроля и идентификации пароля пользователя и формирования сигнала блокировки СВТ в случае несанкционированного доступа (НСД).

Пятый 6 счетчик импульсов, четвертый 28 мультиплексор, элементы обратной связи задержки 23, второго 20 элемента ИЛИ и ключевого элемента 34 предназначены для формирования режима программирования блока 33 программируемой памяти (при выполнении определенного количества попыток НСД) в целях долговременной блокировки СВТ.

Блок 33 программируемой памяти предназначен для формирования сигналов ЧТЕ- НИЯ/ЗАПИСЬ, используемых в работе

блока 8 оперативной памяти, и сигналов блокировки СВТ.

Блок 18 элементов И и третий 11 триггер предназначены для управления работой

первого 2 и третьего 4 счетчиков импульсов в режимах накопления и обработки информационных посылок пароля пользователя.

Второй 17 элемент И предназначен для передачи информации на выход 24 устройетва, указывающей на разрешенную область памяти при правильном вводе пароля пользователя.

Рассмотрим принцип работы устройства контроля и идентификации пользователя.

5 При включении питания и подаче сигнала СБРОС на вход 39 устройство переходит в исходное состояние, т.е. все компоненты, содержащие элементы памяти (кроме блока 8 оперативной памяти, блока 32 постоянной

0 памяти и блока 33 программируемой памяти), устанавливаются в нулевое состояние. Причем второй 1.0 триггер переводится в нулевое состояние за счет сигнал а, поступающего на установочный вход с первого ин5 формационного выхода дешифратора 7 и который формируется при нулевом состоянии второго 3 счетчика импульсов. Парафаз- ный сигнал со второго 10 триггера переключает пятый 29 мультиплексор в ре0 жим передачи сигналов синхронизации по входу 40 для подсчета во втором 3 счетчике импульсов количества входных кодовых чисел, составляющих пароль пользователя. С приходом первой информационной

5 посылки (кодового числа) и сопровождающего ее синхросигнала во второй 13 регистр производится запись содержимого посылки. Одновременно с этим, производится увеличение содержимого второго 3 счетчика

0 импульсов (режим суммирования/вычитания обусловлен состоянием второго Ю.триг- гера). При этом, выходное состояние второго 3 счетчика импульсов и второго 10 триггера обеспечивают формирование в

5 блоке 33 программируемой памяти сигнала запись информации из второго 13 регистра в блок 8 оперативной памяти по адресу, определяемому состоянием второго 3 счетчика импульсов. Кроме того, число, записан0 ное во второй 13 регистр, поступает на информационный вход первого 25 мультиплексора. Синхросигнал, пройдя через пятый 29 мультиплексор, поступает на тактовый вход третьего 11 триггера, на ин5 формационный вход которого поступает сигнал с уровнем логической 1 с инверсного выхода второго 10триггера. С инверсного выхода третьего 11 триггера сигнал с уровнем логического О поступает на R-входы первого 2 и третьего 4 счетчиков импульсов

и тем самым разрешается их работа. Импульсная последовательность генератора 1 тактовых импульсов поступает на счетный вход первого 2 счетчика импульсов и произ- водит последовательное увеличение его состояния на единицу. Информационный выход первого 2 счетчика импульсов соединен с адресным входом первого 25 мультиплексора и п-ри изменении адреса производится мультиплексирование разря- дов кодового числа на информационный выход, соединенный со входом разрешения третьего 4 счетчика импульсов. Если в соответствующем разряде входного слова имеется логический О, то содержимое третьего 4 счетчика увеличивается на 1, если же в разряде присутствует логическая 1, тотретий 4 счетчик импульсов не реагирует на воздействие тактового импульса. После завершения просмотра последнего бита ко- довой посылки в третьем 4 счетчике импуль- сов будет зафиксировано число, соответствующее количеству нулей в выходном состоянии второго 13 регистра, которое суммируется в. сумматоре 36 с числом, находящимся в первом 12 регистре. По фронту t(0.1) сигнала переноса на выходе первого 2 счетчика импульсов содержимое сумматора 36 переписывается в первый 12 регистр. Сигнал с выхода подтверждения записи первого 12 регистра, пройдя через первый 16 элемент И, переводит первый 9 триггер в нулевое состояние/Сигнал .с уровнем логической 1 с инверсного выхода первого 9 триггера устанавливает первый 2 и третий 4 счетчики импульсов в нулевое состояние. Информация о структуре пароля (количест- веинформационных посылок в пароле пользователя) выбирается из ячейки блока 32 постоянной памяти согласно состояниям первого 12 регистра и второго 3 счетчика импульсов и по фронту t(1,0) сигнала переноса на выходе первого 2 счетчика импуль- сов переписывается в третий 14 регистр. Причем информационный вход старшего разряда третьего 14 регистра подключен к шине питания, а информационный выход старшего разряда подключен ко входу ЗАПРЕТ логического элемента ИЛИ 21, выход которого соединен со входом записи третьего 14 регистра. Такое схемотехническое решение обеспечивает однократную запись информации о структуре пароля в регистр и не позволяет изменять эту информацию в пределах одного цикла ввода пароля пользователя. Младшие информационные выходы третьего 14 регистра соединены с адресным входом второго 26 мультиплексора, а информационные входы последнего со старшими информационными выходами

дешифратора 7. Таким образом осуществляется коммутация сигналов с выходов дешифратора 7 на S-вход второго 10 триггера согласно информации о структуре пароля, записанной в-третий 14 регистр. При этом на входе разрешения второго 26 мультиплексора присутствует сигнал с уровнем логического О (выход третьего 11 триггера), который разрешает выполнение операции мультиплексирования.

Если пароль пользователя содержит i кодовых посылок пароля, поступающих на вход 6 устройства, то после приема первой поеыдки устройство ожидает поступления на вход 6 следующей посылки и сопровождающего ее синхросигнала по входу 34. При этом алгоритм приема остальных слоев пароля такой же, как описано выше, за исключением того, что состояние третьего 29 регистра не изменяется. Не изменяется состояние и второго 10 триггера, т.е. он продолжает оставаться в нулевом состоянии. Эта последовательность работы будет продолжаться до поступления i-ой посылки пароля.

При получении i-ой посылки, т.е. последней кодовой посылки или когда пароль пользователя состоит из одного слова, алгоритм работы устройства изменяется. Согласно информации на выходе третьего 14 регистра третий 27 мультиплексор передает сигнал на S-вход второго 10 триггера с i-ro разряда дешифратора 7, который формируется по состоянию второго 3 счетчика импульсов, подсчитывающего количество синхросигналов сопровождения посылок по входу 40. Переключение второго 10 триггера в единичное состояние обеспечивает перевод устройства в режим контроля и идентификации пароля пользователя. При этом производятся следующие действия: сигнал с уровнем логического О с инверсного выхода второго 10 триггера запрещает прохождение синхросигналов через пятый 29 мультиплексор, определяет область памяти блока 33 программируемой памяти, в которой записана информация о сигналах режима чтения блока 8 оперативной памяти, устанавливает первый 9 триггер по S-входу в единичное состояние, с инверсного выхода которого сигнал с уровнем логического О разрешает по R-входу работу первого 2 счетчика импульсов, т.е. устанавливается режим счета импульсов, поступающих от генератора 1 тактовых импульсов, на первом входе разрешения четвертого 28 мультиплексора устанавливается сигнал разрешения мультиплексирования, второй 13 регистр по входу разрешения устанавливается в режим отключения выходов от инфорационной шины (высокоимпедансное сотояние или третье состояние выходов) и- ереключение по входу направления счета второго 3 счетчика импульсов в режим вычиания; сигнал с уровнем логической 1 с прямого выхода второго 10 триггера поступает на информационный вход третьего 11 триггера, разрешает прохождение сигналов переноса от первого 2 счетчика импульсов через пятый 29 мультиплексор и второй 17 элемент И, запрещает запись новых чисел и первый 4 регистр и.по фронту t{0,1) произведет изменение состояние пятого 6 счетчика импульсов, на информационном выходе которого будет присутствовать двоичное число 1. Следовательно, в пятом 6 счетчике импульсов будет зафиксирована первая попытка.овода пароля пользователя. ..

В первом 12 регистре находится двоичное число рапное количеству нулей всех.информационных посылок пароля, которое поступает на второй адресный вход блока 32 постоянной памяти и тождественно определяет область памяти по идентификации пароля i-ro пользователя (здесь i - признак отождествления пользователя по количеству информационных посылок). С; появлением .первого сигнала на выходе переполнения первого 2 счетчика импульсов, который пройдя через пятый 29 мультиплексор, произведет уменьшение состояния второго 3 счетчика импульсов на единицу, т.е. на выходе, второго 3 счетчика импульсов будет присутствовать число, соответствующее (Н)-ой информационной посылки, и которое поступает на адресные входы блока 8 оперативной памяти и блока 32 постоянной -памяти.. При этом,блок 33 программируемой памяти формирует сигнал ЧТЕНИЯ для блока 8 оперативной памяти, информация с которого поступает на первый информационный вход первого 30. цифрового компараторе, а на второйинфор- мационный вход поступает информация, с блока 32 постоянной памяти. Если компари- руемые числа равны, то с информационного выхода РАВНО сигнал логической 1 устанавливает четвертый 5 счетчик импульсов в счетный режим. В этом случае, сигнал переноса первого 2 счетчика импульсов, пройдя через элемент НЕ 37, второй 17 элемент И, по фронту t(0,1) произведет увеличение состояния четвертого 5 счетчика импульсов на единицу. Если же компенсируемые числа не равны, то четвертый 5 счетчик импульсов останется в. прежнем состоянии.

Рассмотрим случай правильного ввода пароля, т.е. все информационные посылки пароля пользователя, записываемые в.блок 8 оперативной памяти соответствуют содержанию и последовательности информации, записанной в блок 32 постоянной памяти. Когда во втором 3 счетчике импульсов будет зафиксировано двоичное число один, на выходе блока 32 постоянной памяти будет присутствовать число, которое поступает на второй информационный вход второго 31 цифрового компаратора и сравнивается с выходным числом четвертого 5 счетчика импульсов, поступающим на первый информационный вход второго 31 компаратора. При сравнении чисел на информационном выходе РАВНО второго31 цифрового компаратора сформируется сигнал с уровнем

логической 1 и по переднему фронту t(0,1) произойдет запись единицы в третий 11 триггер ( на информационном входе) присутствует сигнал с уровнем логической Т, поступающий с прямого выхода второго

10 триггера). Выходной сигнал третьего 11 триггера разрешает-прохождение кода области памяти пользователя с выхода блока 32 постоянной памяти через блок 18 элементов И на информационный выход 24 устройства; разрешает работу второго .26 мультиплексора, с помощью которого определяется момент окончания работы пользователя; устанавливает по R-входу второй 3 счетчик импульсов в исходное (нулевое) состояние, пройдя через первый 19 элемент ИЛИ, а также отключает по входу разреше- ния второй 26 мультиплексор. В тот мсмент времени, когда на информационном выходе второго 3 счетчика импульсов присутствует

двоичное число один, на первый и второй .входы разрешения четвертого 28 мультиплексора поступают сигналы с уровнем логйческого О с инверсного выхода второго

10триггера и первого информационного выхода дешифратора 7, соответственно, которые открывают его для анализа состояния пятого 6 счетчика импульсов: Допустим, что четвертый 28 мультиплексор запрограмми- . рован на мультиплексирование активного

5 уровня сигнала в k-ом канале (где k - число разрешенны-х попыток ввода пароля, фиксируемых в пятом 6 счетчике импульсов), то при первой попытке (как в данном случае) на выходе четвертого 28 мультиплексора ак0 тивный сигнал будет отсутствовать и ключевой элемент 34 не откроется. При завершении режима контроля и идентификации и положительном исходе пользователю предоставляются средства ВТ с

5 указанной областью памяти. После этого устройство переходит в режим ожидания, т.е. не участвует в работе пользователя с предоставленными ему средствами. Если на информационный вход 15 устройства поступает информационная посылка (идеитификатор пользователя) и сигнал сопровождения (вход 40), то она записывается во второй 13 регистр, с выхода которого поступает на адресный вход второго 26 мультиплексора. Одновременно с этим выходное число второго 13 регистра подвергается преобразованию (первый 19 мультиплексор, третий 4 счётчик импульсов, сумматор 36 и первый 12 регистр) в оценку количества нулей в посылке, которая с выхода первого 12 регистра поступает на информационный вход второго 26 мультиплексора. При соответствии количественной оценки числовому отображению идентификатора .на информационном выходе второго 26.мультиплексора будет сформирован сигнал с уровнем логического О, который, ка.к и входной ситная на выходе 39 СБРОС, произведет установку устройства в исходное состояние. Устройство готово к приему нового пароля, т.е., к смене пользователя. Если: идентификатор не соответствует i-му пользователю, то устройство останется в преж нем состоянии.

Если хотя бы одна информационная по сылка пароля пользователя, записанная в блок 8 оперативной памяти, не соответствует содержанию информации, записанной в блок 32 постоянной памяти, то на выходе первого 12 -регистра информация не будет соответствовать истинной и адресное пространство блока 32 постоянной памяти будет переориентировано. В этом случае в первом 30 цифровом компараторе не будет выполнено условие непрерывной идентификации входных информационных потоков и. следовательно, в четвертом 5 счетчике импульсов будет зафиксировано число (меньшее по величине), которое вб втором 31 цифровом компараторе не будет скомпа- рировано с формированием на выходе сигнала РАВНО, что, в свою очередь, не вызовет переключения третьего 11 триггера, а следовательно, на информационном выходе 24 устройства будет отсутствовать код идентификации области памяти пользователя. Возможна и другая ситуация/когда последовательность ввода информационных посылок пароля пользователя не соответствует адресному распределению информации в блоке 32 постоянной памяти. При этом выходное число первого 12 регистра идентифицирует истинного пользователя. При этом сравниваемые числа в первом 30 цифровом компараторе не будут во времени идентичны (равными) и при несравнении четвертый 5 счетчик импульсов не будет производить подсчет истинного числа информационных посылок. Следовательно, на выходе второго 31 цифрового компаратора не будет сформирован сигнал

идентификации длины информационных посылок пароля пользователя, третий 11 триггер останется в прежнем состоянии и на информационном выходе 24 устройства бу- 5 дет отсутствовать информация об инициализации области памяти пользователя.

При выполнении попыток НСД допустимо выполнение k попыток ввода пароля. Каждая попытка фиксируется в пятом 6 снет0 чике импульсов/После завершения k-ой попытки на информационном выходе пятого 6 счетчика импульсов устанавливается двоичное число k, которое переводит четвертый 28 мультиплексор в режим коммутирования

5 k-ro канала. На вход программирования блока 33 программируемой памяти поступает от источника 35 напряжение перепрограммирования. Длительность цикла программирования определяется элемен0 том 23 задержки. Следует отметить, что программирование блока 33 программируемой памяти производится только в нулевой ячейке, выходной сигнал которой, пройдя через пятый 29 мультиплексор, поступает на R5 вход третьего ;11 триггера и устанавливает его в нулевое состояние. Выходной сигнал триггера с уровнем логического О запрещает прохождение информации через блок 18 элементов И на информационный выход

0 24 устройства и отключает второй 26 и третий 27 мультиплексоры, а также, пройдя через первый 19 элемент ИЛИ, по R-входу удерживает в нулевом состоянии второй .3 счетчик. При последующих попытках ввода

5 кода пароля (любого из допустимых или произвольного) на информационный выход 24 устройства информация поступать не будет и, следовательно,- пользователь не будет иметь доступа к CBJ. Такая же ситуация

0 будет иметь место и при многократном выключении/включении источника питания. Восстановление устройства возможно только после того, как будет перепрограммирован блок 33 программируемой памяти.

5 Таким образом, по сравнению с прототипом предлагаемое устройство контроля и идентификации пользователя обладает рядом преимуществ. Во-первых, устройство позволяет применять пароли прльзовате0 лей, отличающиеся как по количественным, так и по информативным признакам. Во- вторых, в устройстве использована многоступенчатая структура защиты, которая реализует алгоритм определения количест5 ва нулей по всей последовательности пароля, что является необходимым условием для контроля самого пароля, проверки последовательности информативных посылок пароля, ограничения пользователя по доступу ко всему объему памяти и по числу попыток

пользователя получить доступ к запрещенным областям СВТ, при превышении числа разрешенных попыток устройство блокирует активацию СВТ.

Формула изобретения Устройство для контроля и идентификации пользователя, содержащее генератор тактовых импульсов, первый и второй счетчики имг1ульсов, дешифратор, блок оперативной памяти, первый триггер, первый регистр, второй регистр, информационные входы которого являются информационными входами устройства, третий регистр, первый и второй элементы И« первый - четвертый элементы ИЛИ, элемент задержки, выход которого соединен с первым входом второго элемента ИЛИ,и блок элементов И, выходы которого являются выходами устройства, отличающееся тем, что, с целью повышения надежности защиты средств вычислительной техники от несанкционированного доступа за счет введения многоуровневого алгоритма идентификации, в устройство введены первый-пятый мультиплексоры, третий-пятый счетчики импульсов, первый и второй цифровые компараторы, блок постоянной памяти, блок программируемой памяти, ключевой элемент, источник напряжения перепрограммирования, второй и третий триггеры, сумматор, элемент НЕ и элементИ-НЕ, первый вход которого объединен с первым входом первого элемента И и является входом сброса устройства, первый информационный вход пятого мультиплексора объединен с тактовым входом второго регистра и является входом синхронизации устройства, выходы второго регистра подключены к информационным входам/выходам блока оперативной памяти, информационным входам первого и адресным входам второго мультиплексоров и первой группе входов первого цифрового компаратора, выход которого соединен с разрешающим входом четвертого счетчика импульсов, выходы которого подключены к первой группе входов второго цифрового компаратора, выход которого соединен с тактовым входом третьего триггера, выход которого подключен к управляющему входу блока элементов И, разрешающим входам второго и третьего мультиплексоров и первому входу первого элемента ИЛИ, выход которого соединен с входом обнуления второго счетчика,импульсов, выход генератора тактовых импульсов подключен к счетным входам первого и третьего счетчиков импульсов, выход переполнения первого счетчика импульсов соединен с тактовым входом первого регистра и входом элемента НЕ, выход которого подключен к второму информационному входу пятого мультиплексора, первому входу второго элемента И и первому входу третьего элемента ИЛИ, выход которого соединен с

5 тактовым входом третьего регистра, информационный вход старшего разряда которого подключен к источнику логической единицы, старший разряд выходов третьего регистра соединен с вторым входом третьего

0 элемента ИЛИ, остальные разряды третьего регистра подключены к адресным входам третьего мультиплексора, выход которого соединен с первым установочным входом второго триггера, инверсный выход которо5 го подключен к первому адресному входу пятого мультиплексора, входу запрета записи второго регистра, входу реверсирования счета второго счетчика импульсов, первым группам адресных входов четвертого муль- 0 типлексора и блока программируемой памяти и информационному входу первого триггера, выход которого соединен с входами обнуления первого и третьего счетчиков импульсов, разрядные выходы первого

5 счетчика импульсов подключены к адресным входам первого мультиплексора, выход которого соединен с разрешающим входом третьего счетчика импульсов, выходы которого подключены к первой группе входов

0 сумматора, выходы которого соединены с информационными входами первого регистра, выход подтверждения записи которого подключен к второму входу первого элемента И, выход которого соединен с ус5 тановочным входом первого триггера, прямой выход второго триггера подключен к информационному входу третьего триггера, счетному входу пятого счетчка импульсов, входу запрета записи первого регистра, вто0 рому входу второго элемента И и второму адресному входу пятого мультиплексора, выход которого соединен с тактовым входом первого триггера и счетным входом второго счетчика импульсов, выходы которого

5 подключены к адресным входам блока оперативной п.амяти, второй группе адресных входов блока программируемой памяти, первой группе входов блока постоянной памяти и входам дешифратора, первый вы0 ход которого соединен с вторым установочным входом второго триггера и вторым адресным входом четвертого мультиплексора, выход которого подключен к входу элемента задержки и управляющему

55 входу ключевого элемента, информационный вход и выход которого соединены соот- ветственно с выходом источника напряжения перепрограммирования и информационным входом блока программируемой памяти, первый-и второй выходы

которого подключены соответственно к входу запись/чтение оло.ка оперативной памяти и первому входу четвертого элемента ИЛИ, выход которого соединен с входом обнуления третьего триггера, выход второго элемента И подключен к счетному входу четвертого счетчика импульсов, выход второго элемента ИЛИ соединен с входом обнуления пятого счетчика импульсов, выходы которого подключены к информационным входам четвертого мультиплексора, вторая группа выходов дешифратора соединена с информационными входами третьего мультиплексора, выход второго мультиплексора подключен к второму входу элемента И-НЕ,

5

выход которого соединен с вторыми входами первого, второго и четвертого элементов ИЛИ, входами обнуления третьего регистра и четвертого счетчика импульсов и входом обнуления первого-регистра, информационные выходы которого подключены к второй группе входов сумматора, информационным входам второго мультиплексора и второй группе входов блока постоянной памяти, выходы которого соединены со вторыми группами входов цифровых компараторов, информационными входами остальных разрядов третьего регистра и информационными

входами блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1990 |

|

SU1748156A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для ввода информации | 1989 |

|

SU1645949A1 |

| Устройство для идентификации паролей пользователей | 1988 |

|

SU1661814A1 |

| Программируемый многоканальный формирователь серий импульсов | 1991 |

|

SU1775846A1 |

| Устройство для идентификации паролей пользователей | 1990 |

|

SU1730615A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЯЕМОЙ ПАМЯТИ | 2014 |

|

RU2550555C1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для информационного поиска | 1988 |

|

SU1587543A2 |

Изобретение относится к автоматике и вычислительной технике. Если использование в средствах вычислительной техники позволяет повысить надежность защиты средств вычислительной техники от несанкционированного доступа за счет введения многоуровневого алгоритма идентификации. Благодаря введению дополнительных элементов устройство позволяет применять пароли пользователей, отличающиеся по количественным и информативным признакам; используется многоступенчатая структура защиты, реализующая алгоритм определения количества нулей во всей последовательности пароля. Т ил.

| Сяо Д., Керр Д., Мэдник С | |||

| Защита ЭВМ | |||

| - М.: Мир, 1982 | |||

| Устройство для статического анализа кодов | 1988 |

|

SU1571615A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1993-08-15—Публикация

1991-03-04—Подача