(5) УСТРОЙСТВО для ЗАПИСИ и КОНТРОЛЯ ПРОГРАММИРУЕМЫХ БЛОКОВ ПОСТОЯННОЙ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

По основному авт. св. № 796909 известно устройство для записи и контроля программируемых блоков постоянной памяти, которое содержит регистр текущего адреса и регистр данных, одни из входов которых подключены к выходам задающего генератора и блока рперативной памяти, а выходы соответственно к первым выходам фор мирователя адресных сигналов и формирователя сигналов данных, компаратор конечного адреса, входы которого соединены с выходами регистра конечного адреса и регистра текущего адреса, компаратор данных,один из входов которого подключен ко входу устройства, а другие входы со.единены с выходами регистра данных и блока оперативной памяти, один из входов которого подключен к выходу счетчика, блок управления, блок аналоговой памяти, ключи, цифроаналоговый

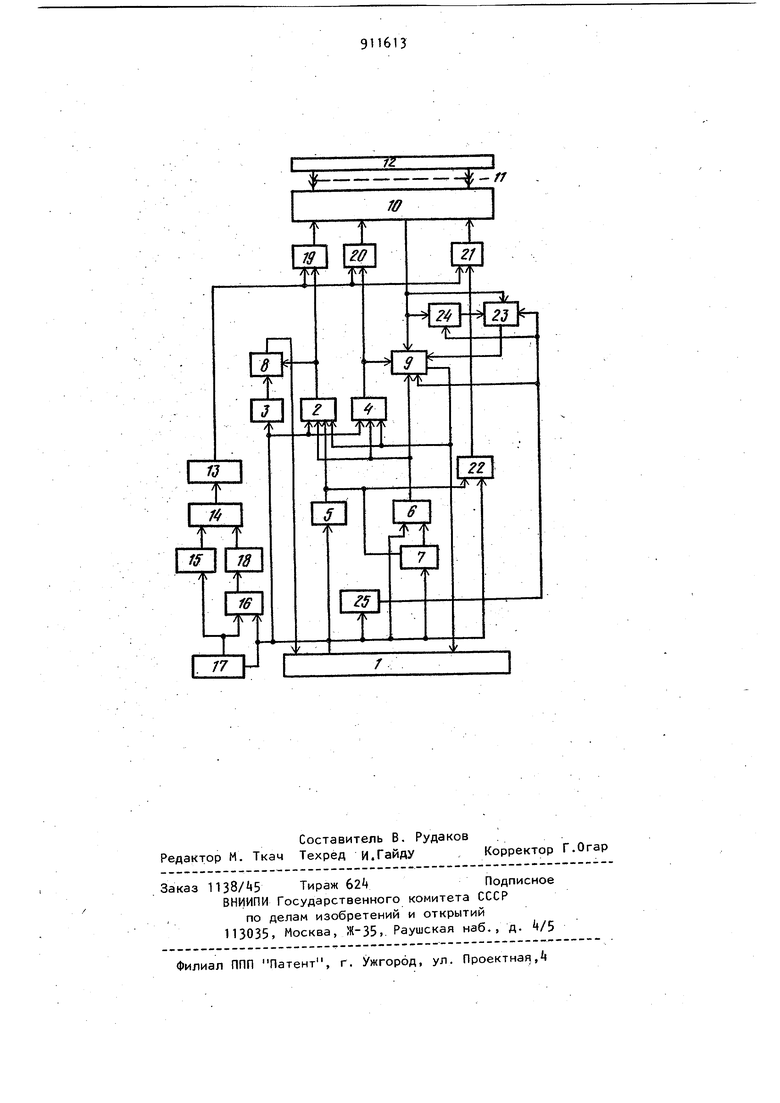

преобразователь, дешифратор, дополнительный блок оперативной памяти и счетчик, формирователь синхросиглалов и блок программируемых синхросигналов, причем входы блока аналоговой памяти соединены с выходами ключей, а выходы -.со вторыми входами формирователя адресных сигналов и формирователя сигналов данных и первым входом формирователя синхросигналов, второй вход которого подключен к выходу блока программируемых синхросигналов и другим входам регистра текущего адреса и регистра данных, а выход - к одному из выходов устройства, выходы дешифратора и цифроаналогового. преобразователя соединены со входами ключей, а входы - соответственно с выходами дополнительного счетчика и дополнительного блока оперативной памяти, первый вход которого подключен к выходу дополнительного счетчика, вы ход Злока управления соединен со 39 входом дополнительного счетчика,вторым входом дополнительного блока оперативной памяти и одним из входов блока программируемых синхроимпульсов, другой вход которого подключен К выходу задающего генератора Cl . Недостатком этого устройства является то, что в случае функционального контроля программируемых блоков постоянной памяти объемом l6-6i) тыс. и более слов, в составе устройства необходимо иметь блок оперативной памяти с большим объемом. Наличие же такого блока в составе устройства значительно усложняет оборудование и уменьшает надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем что устройство содержит регистр сдви га, формирователь управляющих сигналов и сумматор, причем первые входы регистра сдвига и сумматора подключе ны к одному из входов устройства,ВТО рые входы - к выходу формирователя . управляющих сигналов, вход которого соединен с одним из выходов блока уп равления, третий вход сумматора подключен к выходу регистра сдвига, а выход сумматора соединен с одним из входов компаратора данных, другой вход которого подключен к выходу фор мирователя управляющих сигналов. На чертеже изображена блок-схема устройства для записи и контроля про граммируемых блоков постоянной памяти. . Устройство содержит блок 1 управления, регистр 2 текущего адреса, регистр 3 конечного адреса, регистр данных, задающий генератор5 ,блок 6 оперативной памяти, счетчик 7, ком паратор 8 конечного адреса, компаратор 9 данных. Ко входам и выходам устройства подключается индивидуальный модуль 10, к которому через разъемы 11 подсоединяется программируемый блок 12 постоянной памяти. Устройство также содержит блок 13 аналоговой памяти, ключи I, дешифра тор15 дополнительный блок 16 опера тивной памяти, счетчик 17. цифроаналоговый преобразователь 18, формирователь 19 адресных сигналов, формирователь 20 сигналов данных, формирователь 21 синхросигналов, блок 22 программируемых синхросигналов, сум4. матор 23, регистр сдвига и формирователь 25 управляющих сигналов. Первые входы регистра сдвига и сумматора 23 подключены к одному из входов устройства, вторые входы к выходу формирователя 25, вход которого соединен с одним из выходов блока 1 управления. Третий вход сумматора 23 подключен к выходу регистра 24 сдвига, а выход сумматора 23 соединен с одним из входов компаратора 9 данных, другой вход которого подключен к выходу формирователя 25. Устройство работает следующим обра з.ом. В память блока 1 записываются программы первичного контроля, с помощью которых определяется качество блока 12. Из блока 1 в соответствии с программой входного контроля необходимая информация заносится в блок 16оперативной памяти для задания величины верхних и нижних границ импульсов формирователей 19 с целью определения начала и конца контроля; в блок 22 программируемых синхросигналов для выбора номера канала, задержки и длительности импульсов синхронизации; в задающий генератор 5 определяющий -частоту контроля. По команде из блока 1 в соответствии с временной диаграммой работы блока 12 блок 22 выдает сигналы на индивидуальный модуль 10 и на регистры 2 и 4. По первоначальному адресу, записанному в регистре 2, считывается информация из блока 12 на компаратор 9 где идет сравнение с содержимых регистра t. Положительный результат сравнения позволяет добавить единицу в регистр 2 с периодом, определяемым задающим генератором 5Отрицательный результат сравнения поступает в блок 1 и.запрещается добавление единицы в регистр 2. При сравнении содержимого регистра 2 с содержанием.регистра 3 в блок 1 приходит команда Годен. Формирование величины верхних и нижних границ импульсов в формирователях происходит после записи в блок 16 последнего слова. Счетчик 17тактируется собственным внутренним генератором. Каждое состояние счетчика 17 расшифровывается дешифратором 15 в позиционный код и ВЬ13Ывает считывание соответствующего слова в виде двоичного кода из блока 16. 5 Двоичный код каждого слова блока 16 преобразуется цифроаналоговым преобразователем 18 в аналоговый , сигнал. Этот сигнал через открытый соответствующим позиционным кодомдешифратора 15 один из ключей 1 4 пос тупает и запоминается элементами памяти блока 13 аналоговой памяти. С выходов блока 13 соответствующие cvir налы напряжения поступают на формирователи 19-21, подготавливая их к работе. После подготовки формирователей с регистра 2 на формирователь 19 последовательно поступают коды адресов ячеек блока 12. Они, преобразовываясь формирователями 19 в необходимую форму, поступают на адресные входы блока 12. С кодом каждого адреса блока 12 выдается управляющий сигнал блоком 22. Этот сигнал через формирователь 21 также поступает на соответствующие входы блока 12. По каждому адресу происходит считывание информации выбранной ячейки блока 12 и сравнение этой информации с пер воначальной записанной в per 1стре Ц компаратором 9. Так продолжается до тех пор, пока код регистра 2 не срав нивается с кодом регистра 3 компаратором 8, который выдает в блок 1 соответствующий сигнал. Цикл входного контроля работоспособности блока 12 заканчивается. Так выполняется цикл функционального контроля блоков 12 с объемом до -16 ть1с. бит информа-. ции. Если же объем блока 12 больше указанной величины, то их первичный функциональный контроль может быть выполнен по сокращенной программе с помощью сумматора 23, регистра 2k и формирователя 25- С этой целью аналогично описанному выше выполняется подготовка всех блоков и узлов устройства. Весь массив памяти блока 12 разбивается на несколько зон. Для каждой зоны определяется циклическая или обычная сумма чисел, входящих в эту зону. В блок 6 оперативной памяти заносятся значения указанных сумм. В том случае, когда блок 12 имеет один разряд,формирователь 25 блокирует компаратор 9 и сумматор 23 открывая регистр 2Ц для приема информации с блока 12. При этом заполняется регистр 2.. После чего формирователем 25 выдается сигнал для передачи информации из регистра 2 в сумматор 23. Происходит суммиро 3.6 вание числа, переданного из регистра 2+ с содержимым сумматора 23- Описанный цикл работы продолжается до тех пор, пока не будет считано пос- леднее число из контролируемой зоны памяти блока 12 и не получена сумма всех чисел зоны. После этого формирователь 25 передает полученную сумму в компаратор 9, куда ранее из блока 6-оперативной памяти было.занесено контрольное число и где происходит их сравнение и определяется результат контроля. Цикл контроля следующей зоны блока 12 происходит аналогично. 6 том случае, когда контролируется многоразрядный блок 12, информация может быть передана прямо в сумматор 23, минуя регистр 2. В сумматоре 23 накапливается сумма чисел контролируемой зоны блока 12, Дальнейший цикл контроля аналогичен описанному выше. После проведения входного функционального контроля выполняется программирование (запись) в соответствии с таблицей истинности, занесенной в память блока 1. С этой целью после занесения требуемой информации и подготовки к работе фopмиpoвaтeлeйlf 19 21 аналогично описанному выше с регистра k на формирователь 20 синхронно с каждым адресом поступает информация, в соответствии с которой происходит электрическое программирование блока 12. Отличия режима программирования от режима входного контроля следующие: добавление единицы в регистр 2 проводится по команде из блока 1, а . не из задающего генератора из каналов синхронизации выбирается для организации паузы после программирования, так как,например, биполярные схемы программируемых постоянных блоков памяти требуют знaчиteльную паузу после программирования каждого бита в режиме программирования в течение паузы проводится контроль правильности программирования в зависимости от типа схемы программируемого блока 12 после каждого бита или всего слова , задающий генератор необходим только для организации синхроимпульсов и паузы в блоке 22. Режим программирования выполняетя, как и в первом случае, до тех

7

пор, пока код регистра 2 не станет равным коду регистра 3.

После окончания режима программирования проводится режим выходного функционального контроля. Отличия режима выходного контроля от входного заключаются в том, что ожидаемая информация для сравнения при считывании из блока 12 на компаратор 9 поступает из блока 6 оперативной памяти, в которой предварительно была занесена из блока 1;добавление единицы в счетчик 7 и регистр 2 идет синхронно из задающего генератора 5 с частотой предельной для .конкретного типа блока 12; если объем памяти блока 6 меньше объема, памяти блока 12, то режим выходного функционального контроля повторяется несколько раз, при этом последовательно увеличивается сойержимое регистра 2. Окончание выходного функционального контроля Проводится по содержимому регистра Зп

Выходной функциональный контроль программируемых постоянных блоков памяти с большим объемом памяти может; быть также выполнен путем сравнения контролЬнь1Х сумм, как это было описано выше в разделе входного контроля.

Предлагаемое устройство позволяет выполнить функциональный контроль

16138

блоков постоянной памяти объемом бо-, лее 16-65 тыс. бит информации при ограниченном (2- тыс. бит) объеме блока оперативной памяти самого устс ройства.

Формула, изобретения

Устройство для записи и контроля программируемых блоков постоянной памяти по авт.евi 79690S. отличающееся тем, что, с целью повышения надежности устройства,

оно содержит регистр сдвига, формирователь управляющих сигналов и сумматор, причем первые входы регистра сдвига и сумматЬра подключены к бдному из входов устройства, вторые

входы - к выходу формирователя управляющих сигналов, вход которого соединен с одним из выходов блока управления , третий вход сумматора подключен к выходу регистра сдвига, а выход

сумматора соединен с одним из входов компаратора данных, другой вход которого подключен к выходу формирователя управляющих сигналов.

Источники информации,

принятые во внимание при экспертизе

Jz

. fi

-- -- - ff - //

Авторы

Даты

1982-03-07—Публикация

1978-12-21—Подача