1

Изобретение относится к вычислительной технике и может быть исполь зовано при построении схем считывания информации..

Известен блок памяти, котсчР): содержит обмотки считывания, разделенные на секции, при этом несколько секций соединяются с входсм усилителя считывания, например, через коммутируемые разделительные диоды fl.

Недостатком такого блока памяти является его низкая надежность.

Наиболее близким по технической сущности к предлагаемому изобретению является блок памяти запоминакицего устройства, содержащий ферритовые сердечники, прошитые адресными и разрядньми шинами, шиной считывания, разделенной на секции,усилители считывания, выходы которых;соединены с входами элемента ИЛИ .

Недостатком такого .блока памяти акже. является низкая надежность изз-а возникающих помех в процессе считывания инфо1нлации

Цель изобретеиия - повышение надежности блока памяти.

лгазаиная цель достигается тем, что шины считывания, проход 1щ.«е через ферритовые сердечники, прошитые.

разными адресньши и разрядным шинами, соединены параллельно и подключены ко входам соответствующих усилителей считывания.

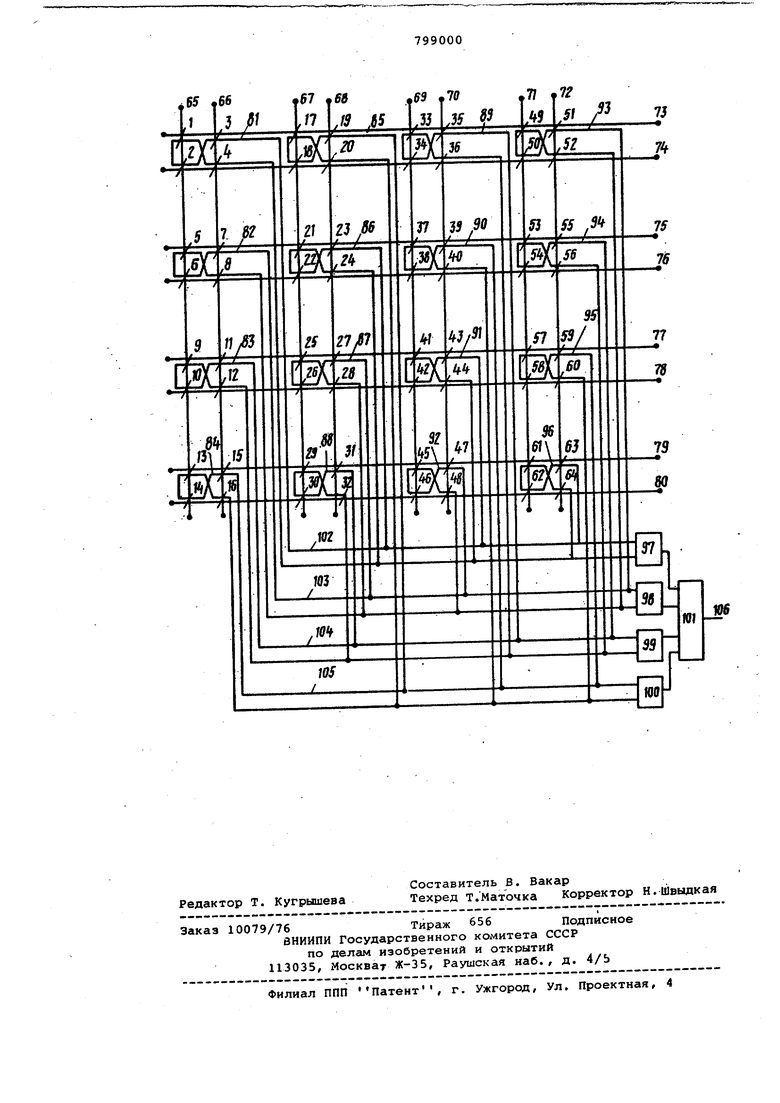

На чертеже представлена структурная схема блока памяти.

Блок памяти содержит ферритовые сердечники 1-64, адресные шины 65-72, разрядные шины 73-8Q, шины 81-96 считывания усилители 97-100 считывания, элемент ИЛИ 101, группы шин 102-105 считывания, выходную шину 106.

Шины 81, 86, 91, 96 считывания, охватывающие ферритовые сердечники 1-4, 21-24, 41-44, 61-64 соответственно, прошитые разнь и группами адресных и разрядных обмоток 65, 66 и 73, 74} ё7,68 и 75, 7бТ 69,70 и 77,78 71,72 и 79,80 соответственно, соединены параллельно в группу 102 и подключены ко входу усилителя 97 считывания.

Аналогичным образом соединены в группы 103,104,105 шины считывания 82,87,92,93; 83,88,89,94; 84,85,90, 95 соответственно и подключены к усилителям 93,99,100 считывания соотватственно. Выходы усилителей 97-100 считывания соединены со входами элеjsiejiTa или 101.

Устройство работает следующим образом.

При считывании информации подаются полутЬки выборки в одну иэ адресных шин 65-72 и в одну из разрядных шин 73-80. Один из сердечников 1-64, в котором суммируются полутоки выборки, выбирается и наводит рабочий сигнал в соответствующей шине считывния одной из групп шин 102-105 считывания, при этом в других шинах этой же группы сигналы помехи не наводятс так как полувыбранные вердечники не охватываются этими шинами, т.е. эти шины считывания выполняют функцию шунтирующей нагрузки по отношению к шине,в которой наводится считанный сигнал. Считанный сигнал состоит из рабочего сигнала, сигналов помех от полувыбранных сердечников и емкостных помех от полутоков выборки. Вследствие различной мсхдности рабочего сигнала и сигналов помех, псмехи шунтируются эффективнее рабочего сигнала, что приводит к увеличению отношения рабочего сигнала к сигнаЛс1м помех.

Считанный сигнал усиливается одни из усилителей 97-100 считывания и через элемент ИЛИ 101 подается на выходную шину 106. При этом коэффициент усиления должен быть больше, чем в том случае когда к одному усилителю подключена одна шина считывания.

Возможно параллельное соединение в группы и другого числа шин, начиная с двух.

Введение параллельного соединения шин считывания в группу по предлагаемому принципу позволяет за счет увеличения отношения рабочего сигнала к сигналам помех расширить область работоспособности блока памяти, а также соответственно уменьшить количество усилителей считывания в блоке памяти.

Формула изобретения

Блок памяти, содержащий элементы памяти на ферритовых сердечниках, прошитые адресными и разрядными шинами во взаимно перпендикулярных направлениях, шины считывания, каждая из которых пропущена через группы ферритовых сердечников крест-накрест и усилители считывания, выходы которых соединены с соответствующими входами элемента ИЛИ, отличают ий с я тем, что, с целbioi повышения его надежности, шины считывания, проходящи через Ферритовые сердечники, прошитые разньми адресными и разрядными шинами, соединены параллельно и подключены ко входам соответствующи усилителей считывания.

Истрчники информации, принятые во внимание при экспертизе

1.Патент США № 3487384, кл. 340-174, опублик. 1969.

2.Патент США 3518640,

кл. 340-174, опублик, 1970 (прототип

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель для магнитного запоминающего устройства | 1976 |

|

SU588834A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Способ выборки информации из магнитного запоминающего устройства | 1977 |

|

SU744721A1 |

| Запоминающее устройство с сохранением информации при аварийном отключении питания | 1977 |

|

SU693441A1 |

| Параллельный матричный сумматор- вычитатель | 1977 |

|

SU737950A1 |

| Магнитное оперативное запоминающее устройство | 1981 |

|

SU980161A1 |

| Устройство для контроля двухпроводных запоминающих матриц | 1978 |

|

SU752503A1 |

| ФЕРРИТОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЛИНЕЙНОЙ | 1973 |

|

SU377876A1 |

| Запоминающее устройство | 1971 |

|

SU479151A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

Авторы

Даты

1981-01-23—Публикация

1979-04-11—Подача