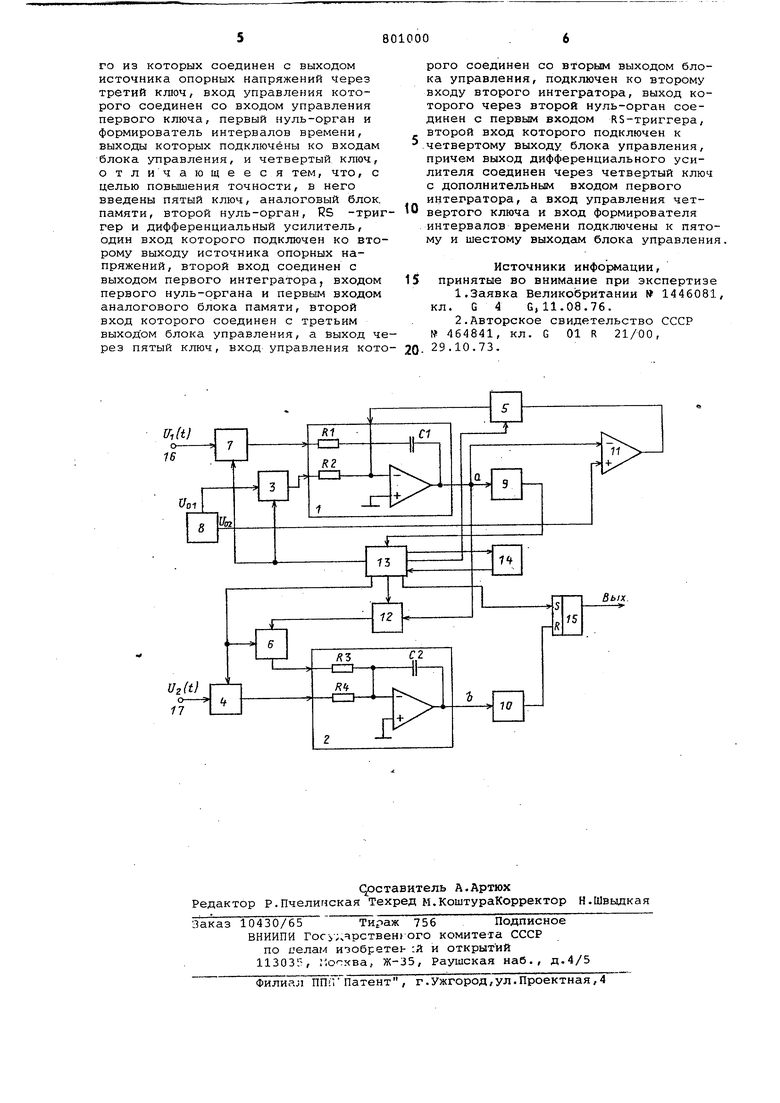

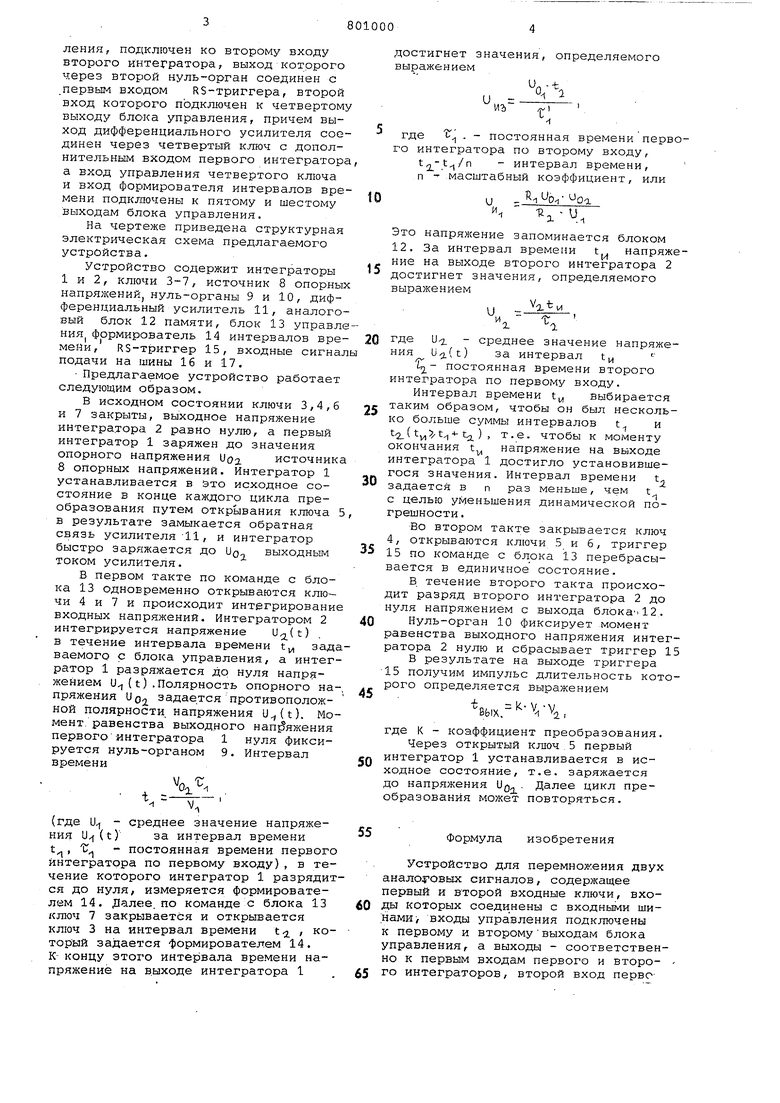

Изобретение относится к вычислительной технике. Известно устройство для аналогово го перемножения двух сигналов, содер жащер два канала, суммирующий элемен усилитель, полевой транзистор в цепи управления второго усилителя 1 Недостаток устройства заключается в малой точности умножения переменны сигналов. Наиболее близким к предлагаемому по технической сущности является уст ройство/содержащее два входных ключа, входы управления подключены к двум выходам блока управления, а выходы - соответственно к первым входа двух интеграторов, второй вход первого из которых соединен с выходом источника опорных напряжений через третий ключ, вход управления которого соединен.со входом управления первого ключа, нуль-орган и формирователь интервалов в реме ни, выходы которых подключены ко входам блока управления, и четвертый ключ 2. Данное устройство не обеспечивает достаточной, точности. Цель изобретения - повышение точности. Поставленная цель достигается тем, что в устройство-, содержащее первый и второй входные ключи, входы которых соединены с входными шинами, входы управления подключены к первому и второму выходам блока управления, а выходы - соответственно к первым входам первого и второго интеграторов с второй вход первого из которых соединен с выходом источника опорных напряжений через третий ключ, вход управления которого соединен со входом управления первого ключа, первый нуль-орган и формирователь интервалов времени, выходы которых подключены ко входам блока управления и четвертый ключ, введены пятый Kfuo4, аналоговый блок памяти, второй нуль-орган, RS-триггер и дифференциальный усилитель, один вход которого подключен ко второму выходу источника опорных напряжений, второй вход соединен с выходом первого интегратора, входом первого нуль-органа и nepstw входом аналогового блока памяти, второй вход которого соединен с третьим выходом блока управления, а выход через пятый ключ, вход управления которого соединен со вторьм выходом блока управления, подключен ко второму входу второго интегратора, выход которого через второй нуль-орган соединен с .первым входом RS-триггера, второй вход которого подключен к четвертом выходу блока управления, причем выход дифференциального усилителя сое динен через четвертый ключ с дополнительным входом первого интегратор а вход управления четвертого ключа и вход формирователя интервалов вре мени подключены к пятому и шестому выходам блока управления. На чертеже приведена структурная электрическая схема предлагаемого устройства. Устройство содержит интеграторы 1 и 2, ключи 3-7, источник 8 опорны напряжений, нуль-органы 9 и 10, дифференциальный усилитель 11, аналого вый блок 12 памяти, блок 13 управл ниЯ| формирователь 14 интервалов вре мени, RS-триггер 15, входные сигна подачи на шины 16 и 17. Предлагаемое устройство работает следующим образом. В исходном состоянии ключи 3,4,6 и 7 закрыты, выходное напряжение интегратора 2 равно нулю, а первый интегратор 1 заряжен до значения опорного напряжения Uoj. источник 8 опорных напряжений. Интегратор 1 устанавливг1ется в это исходное состояние в конце каждого цикла преобразования путем открывания ключа в результате замыкается обратная связь усилителя -Ц, и интегратор быстро заряжается до UQ выходным током усилителя. В первом такте по команде с блока 13 одновременно открываются ключи 4 и 7 и происходит интегрировани входных напряжений. Интегратором 2 интегрируется напряжение U,j(t) в течение интервала времени t, зад ваемого с блока управления, а интег ратор 1 разряжается до нуля напряжением ).Полярность опорного на пряжения OQ задае.тся противоположной полярности, напряжения ). Мо мент, равенства выходного напряжения первогоинтегратора 1 нуля фиксируется нуль-органом 9. Интервал времени -- V, (где и - среднее значение напряжения U(t) за интервал времени t , t - постоянная времени первого интегратора по первому входу), в течение которого интегратор 1 разрядит ся до нуля, измеряется формирователем 14. . по команде с блока 13 ключ 7 закрывается и открывается ключ 3 на интервал времени t-j. / который задается формирователем 14. К концу этого интервала времени напряжение на выходе интегратора 1 достигнет значения, определяемого выражением - постоянная времени первого интегратора по второму входу, t, - интервал времени, п - масштабный коэффициент, или RiUo,-Uoa Это напряжение запоминается блоком 12. За интервал времени t. напряжение на выходе второго интегратора 2 достигнет значения, определяемого выражением г а (S2. - среднее значение напряжеза интервал постоянная времени второго интегратора по первому входу. Интервал времени t, выбирается таким образом, чтобы он был несколько больше суммы интервалов t и ti(t,т.е. чтобы к моменту Ч окончания t напряжение на выходе интегратора 1 достигло установившегося значения. Интервал времени t задается в п раз меньше, чем t с целью уменьшения динамической погрешности . Во втором такте закрывается ключ 4, открываются ключи 5 и 6, триггер 15 по команде с блока 13 перебрасывается в единичное состояние. В течение второго такта происходит разряд второго интегратора 2 до нуля напряжением с выхода блОка 12. Нуль-орган 10 фиксирует момент равенства выходного напряжения интегратора 2 нулю и сбрасывает триггер 15 В результате на выходе триггера 15 получим импульс длительность которого определяется выражением 4ix. -.-Vi, где К - коэффициент преобразования. Через открытый ключ.5 первый интегратор 1 устанавливается в исходное состояние, т.е. заряжается до напряжения Q,- Далее цикл преобразования может повторяться. Формула изобретения Устройство для перемножения двух аналодровых сигналов, содержащее первый и второй входные ключи, входы которых соединены с входными ши;нами входы управления подключены к первому и второмувыходам блока управления, а выходы - соответственно к первым входам первого и второго интеграторов, второй вход первого из которых соединен с выходом источника опорных напряжений через третий ключ, вход управления которого соединен со входом управления первого ключа, первый нуль-орган и формирователь интервалов времени, выходы которых подключены ко входам блока управления, и четвертый ключ, отличающееся тем, что, с целью повышения точности, в него введены пятый ключ, аналоговый блок, памяти, второй нуль-орган, RS -триггер и дифференциальный усилитель, один вход которого подключен ко второму выходу источника опорных напряжений, второй вход соединен с выходом первого интегратора, входом первого нуль-органа и первым входом аналогового блока памяти, второй вход которого соединен с третьим выходом блока управления, а Выход через пятый ключ, вход управления которого соединен со вторым выходом блока управления, подключен ко второму входу второго интегратора, выход которого через второй нуль-орган соединен с первым входом RS-триггера, . второй вход которого подключен к .четвертому выходу блока управления, причем вьйход дифференциального усилителя соединен через четвертый ключ с дополнительным входом первого интегратора, а вход управления четвертого ключа и вход Формирователя интервалов времени подключены к пятому и шестому выходам блока управления,

Источники информации, принятые во внимание при экспертизе 1.Заявка Великобритании № 1446081, кл. G 4 G,11.08.76.

2.Авторское свидетельство СССР № 464841, кл. G 01 R 21/00, 29.10.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1345345A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1569590A1 |

| НИЗКОЧАСТОТНЫЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1992 |

|

RU2024028C1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

| ЦИФРОВОЙ НИЗКОЧАСТОТНЫЙ ФАЗОМЕТР-ЧАСТОТОМЕР МГНОВЕННОГО ЗНАЧЕНИЯ | 1990 |

|

RU2024027C1 |

| Цифровой низкочастотный фазометр мгновенного значения | 1989 |

|

SU1656472A1 |

Авторы

Даты

1981-01-30—Публикация

1979-02-02—Подача