,54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1982 |

|

SU1086427A1 |

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

Изобретение относится к вычислительной технике и может быть применено при разработке быстродействующих устройств деления, удобных для изготовления в составе больших инте гральных схем (БИС). Известно устройство для деления чисел, формирующее в каждом такте две цифры частного и содержащее регистры делителя и частного, суммато узел формирования утроенного делителя, шесть схем сравнения, узел формирования цифр частного, цепи од нотактного сдвига на два разряда в сумматоре и регистре частного, блок управления tl , Время деления п-раз рядных чисел в этом случае примерно равно .п/а)Л1:,р.Т,.г,.г, где tj.p - время сравнения чисел ; Х. - время сложения двух п-разрядных чисел; Cpj - время однотактного сдвига на два разряда; Сф - время формирования кратных делителя. Основными недостатками известного устройства являются сложность структуры и относитольно низкое быстродей ствие, так как п каждом такте формируются только две цифры частного, а длительность такта достаточно велика. Известно устройство для деления, содержащее регистры делимого и делителя, сумматор округления, шифратор цифр частного, n/k k-разрядных умножителей, п-разрядность регистров операндов, 2 i k4n/r, сумматорПроизведений, три вычитателя, компаратор остатка, счетчик коррекции частного, при этом первая группа входов шифратора цифр частного соединена с выходами сумматора округления, вход переноса которого соединен с шиной логической единицы, группа k выходов шифратора цифр частного соединена с входами первой группы j-ro умножителя (j 1,. ...,n/k), вторая группа входов, которого соединена с j-ой группой k выходов регистра делителя, выходы умножателей соединены с входами сумматора произведений, выходы которого соединены с входами вычитаемого вычитателя, входы уменьшаемого вычитателя соединены с выходом регистра делимого, выходы шифратора цифр частотного соединены с входами счетчика коррекции частного, выхо.цы (k+2) старших разрядов регистров делимого и делителя соединены соответственно второй группой входов шифратора частного и входами слагаемого сумматора округления Г21 .

К недостаткам данного устройства относится большая аппаратурная избыточность при получении многоразрядного частного.

Целью предлагаемого изобретения является сокращение аппаратурных затрат.

Достигается это тем, что устройство для деления чисел, содержащее п-разрядные регистры делимого и делителя, блок управления, сумматор округления, шифратор цифр частного, n/k -разрядных умножителей, сумматор произведений, вычитатель, причем первая группа входов шифратора цифр частного соединена с выходами сумматора округления, вход переноса кото рого соединен с шиной логической единицы, k выходов шифратора цифр частного соединены с входами первой группы j-ro умножителя (j l....n/k), вторая группа входов каждого из которых соединена с j-ой группой k выходов регистра делителя, выходы.умножителей соединены с входами сумматора произведений, выходы которого соединены с входами вычитаемого вычитателя, входы уменьшаемого вычитателя соединены с выходомрегистра делимого, содержит сумматор частного, причем входы младших разрядов сумматора частного соединены с k выходами шифратора цифр частного, вход управления сдвигом на k - 1 разрядов сумматора частного соединен с выходом блока управления, выходы вычитателя с k-ro по (п + k)-ый соединены с входами регистра делимого, выходы (k+3) старших разрядов регистров делимого и делителя соединены соответственно с второй группой входов шифратора цифр частного и с входами сумматора округления.

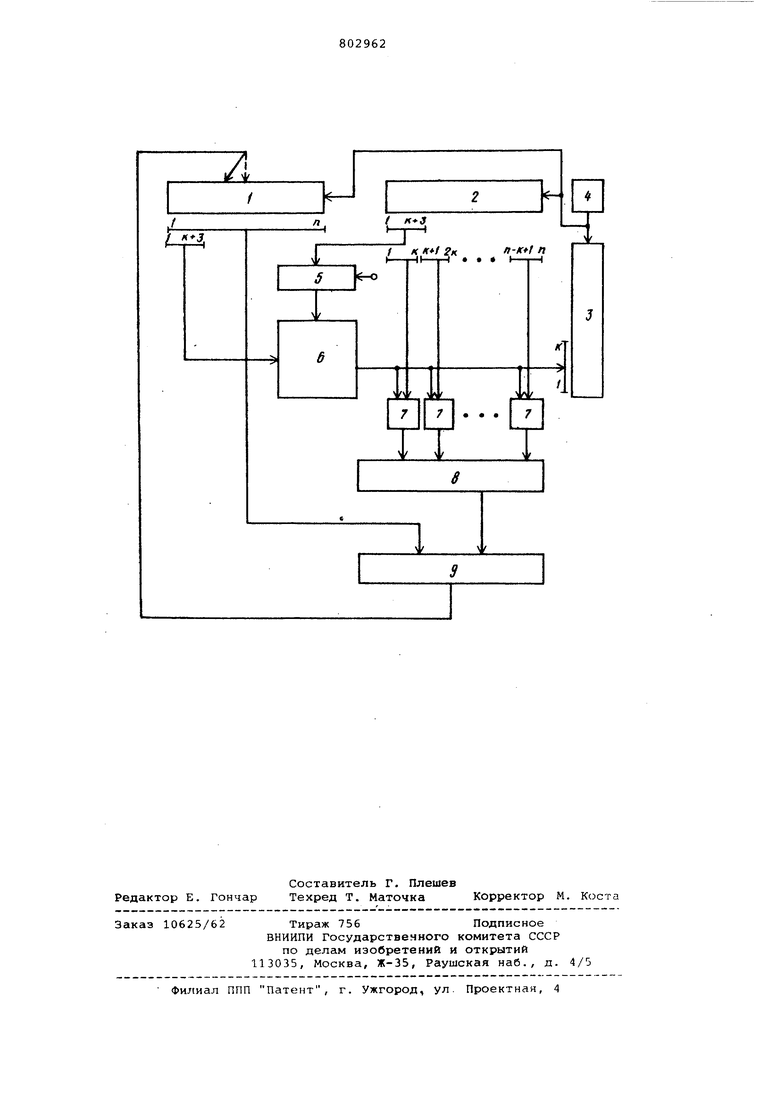

На чертеже представлена схема уст.ройства, содержащая п-разрядные регистры 1 и 2, соответственно делимого и делителя, сумматор 3 частного с цепью однотактного-сдвига на (k-1) разрядов (цепь сдвига на чертеже не показана), блок 4 управления, сумматор 5 округления, шифратор цифр частного б, n/k k-разрядных умножителей 7 для формирования 2 k-разрядных произведений, суг латор 8 произведений и вычитатель 9. Предполагается, что сумматор 5 округления, шифратор 6, умножители 7, сумматор 8 и вычитатель 9 выполнены в виде комбинационных схем.

В определенных случаях может оказаться целесообразным реализация шифратора 6 цифр частного в виде делителя с матричной структурой, состоящего из k(k + 3)-разрядных сумматоров .

Устройство работает следующим образом. В исходном достоянии в регистре 1 делимого хранится прямой п-разрядный код делимого, в регистре 2 делителя - прямой п-разрядный код делителя (здесь предполагается, что делимое и делитель положительные двоичные числа с нулевой целой частью). Сумматор 3 частного в исходном состоянии обнулен. В сумматоре 5 округления производится прибавление к (k + З) старшим разрядам делителя единицы в их младший разряд. Этим самым устраняется возможность получения в шифраторе б цифр частного, в котором производится деление (k -t- 3) старших разрядов делимого на (k + 3) старших разряда делителя, частного с избытком. Можно показать, что абсолютная погрешность (разность между значением частного, получаемым при делении п-разрядных чисел и значением частного, получаег слм при делении усеченных (k + 3)-разрядных чисел) при этом будет заключена в пределах 04 : При этом значении k-разрядного частного, получаемого при делении усеченных чисел, может быть либо равно значению старших k разрядов частного, получаемых при делении п-разрядных чисел, либо меньше его на единицу младшего разряда с весом 2 С-)(в дальнейшем будем говорить соответственно о точном и неточном значениях k-разрядного частного на выходе шифратора б цифр частного). С помощью умножителей 7 и сумматора 8 произведений формируется произведение п-разрядного делителя на и-разрядное частное, а с помощью вычитателя 9 формируется очередной остаток , определяемый как разность между содержимым регистра 1 делимого и содержимым сумматора 8. Таким образом, в каждом такте работы устройства для деления чисел формируется остаток и k-разрядное частное. Остаток, полученный на выходе вычитателя 9, со сдвигом на (k - 1) разрядов влево (в сторону старших разрядов) записывается в регистр 1 делимого и служит в следующем такте работы устройства в качестве делимого, k-разрядное частное, полученное на выходе шифратора 6 цифр частного, записывается в k-младших разрядов сумматора 3 частного, причем его старшая цифра является корректирующей для частного, сформированного к данному такту. Коррекция частного производится путем прибавления старшей цифры k-разрядного частного в младший разряд частного, полученный к данному такту. Время деления п-разрядных чн-

сел в этом случае будет примерно равно х; п

А k-T -ф где ф - время формирования остатка. Округление результата в данном устройстве в принципе может быть организовано точно таким же образом, как и в известных устройствах. Ниже рассматривается пример, поясняющий принцип работы и структурны особенности предлагаемого устройства для деления чисел (для определенности п и k выбраны соответственно равными 9 и 4 ) . Пусть X О,11111111;У 0,10100000 Значение частного z ,10011000 В предлагаемом устройстве вычисли тельный процесс по определению частного организован следующим образом. 1-й такт. В регистре делимого 1 хранится значение х 0,11111111, в регистре 2 делителя хранится значение у 0,10100000; в сумматоре 3 частного Z 0,000000000: в сумматоре 5 округления формируется результат а У-. + 2 0,101000+0,000001 0,101001; в шифраторе 6 цифр частного вырабатывается 4-х разрядное частное z а 0,111111:0,10100 1,100; с помощью умножителей 7 и сумматора 8 формируется произведение Ь у-г 0,10100000«1,100 0,11110000000, с помощью вычитателя 9 формируется очередной остаток С X - Ь 0,11111111-0,11110000000 0,00001111000. Сформированный оста ток С записывается в регистр 1 делимого со сдвигом на три разряда влево, а сформированное частное z - в сумматор 3 частного, после чего осуществляется сдвиг его информации на три разряда в сторону старших разрядов. . 2-й такт, в регистре 1 делимого X 0,01111000, в регистре 2 делителя у 0,10100000, в сумматоре 3 частного z О,001100000;а 0,101001; z 0,011110 : 0,101001 0,101; b у . z,j 0,01100100000; С х - b 0,00010100000. Сформированный оста ток записывается в регистр 1 делимого со сдвигом на три разряда влево, а сформированное частное - в сумматор 3 частного, где возможна коррекция его содержимого, после чего осуществляется сдвиг информации в сумматоре 3 частного на три разряда. 3-й такт. X 0,10100000/ у 0,10100000, z 1,100101000; а . 0,101001; z 0,101000: 0,101001 0,111; Ь у zj 0,10001100000; С X - Ь 0,00010100000. В суммато ре 3 частного после третьего такта z 1,100101111, а в регистре 1 дели мого X 0,1010000. На этом процесс деления заканчивается и производится округление частного. Окончательно получаем z 1,10011000. Таким образом структурные особенности устройства позволяют придти к меньшим апаратурным затратам по сравнению с известным устройством за счет исключения двух вычитателей и коммутатора. Формула изобретения Устройство для деления, содержащее регистры делимого и делителя, блок управления, сумматор округления, шифратор цифр частного, n/k k-разрядных умножителей (п-разрядность регистров операндов, 2 6 k б п/2), сумматор произведений, вычитатель, причем первая группа входов шифратора цифр частного соединена с выходами сумматора округления, вход переноса которого соединен с шиной логической единицы, k выходов шифратора цифр частного соединены с входами первой группы j-ro умножителя ,...,n/k), вторая группа входов которого соединена с j-ой группой k выходов регистра делителя, выходы умножителей соединены с входами сумматора произведений, выходы которого соединены с входами вычитаемого вычитателя, входы уменьшаемого вычитателя соединены с выходами регистра делимого, входы управления регистров делимого и делителя соединены с выходим блока управления, отличающееся тем, что, с целью сокращения аппаратурных затрат, устройство содержит сумматор частного, причем входы младших разрядов сумматора частного соединены с k выходами шифратора цифр частного, вход управления сдвигом на (k - 1) разряд сумматора частного соединен с выходом блока управления, выходы вычитателя с k-ro по (п + k)-й соединены с входами регистра делимого, выходы (k + 3) старших разрядов регистров делимого и делителя соединены соответственно с второй группой входов шифратора цифр частного и с входами сумматора округления. Источники информации, принятые во внимание при экспертизе 1.Папернов А.А. Логические основы ЦВТ.-М. : Сов. радио, 1972, с. 242-246. 2.Авторское свидетельство СССР по заявке № 2546280/18-24, кл. G 06 F 7/52, 1977 (прототип).

Авторы

Даты

1981-02-07—Публикация

1978-02-03—Подача