вого элемента И блока уточнения цифры частного, выходы первого и второго элементов И которого соединены соответственно с первым и вторым входами первого элемента ИЛИ, прямой и инверсный выходы которого соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых объединены и подключены к ()-му выходу преобразователя дополнительного кода в прямой код, ()-й выход которого соединен с третьим входом третьего элемента И блока уточнения цифры частного, первый и второй входы второго элемента ИЛИ которого соединены соответственно с выходами третьего и четвертого элементов И, выход второго элемента ИЛИ блока уточнения цифры частного, выходы, с первого по (1,+ 1)-й, преобразователя дополнительного кода в прямой код соединены соответственно с входами первой группы шифратора, входы, с второго по ()-й, шины делителя соединены соответственно с входа ми второй группы шифратора.,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1978 |

|

SU802962A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1984 |

|

SU1242935A1 |

| Устройство для деления | 1985 |

|

SU1332312A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее шифратор, сумматор произведений, п / 1с k-разрядных умножителей (k 2.. .л/2, а п- разрядность операндов) , причем выход шифратора соединен с первыми входами умножителей, вторые входы которых соединены с соответствующей группой 1 -разрядов шины делителя устройства, выходы умножителей соединены с соответствующими входами сумматора произведений, отличающееся тем, что, с целью повьшения быстродействия устройства, в него введены сумматорвычитатель, блок уточнения цифры частного, преобразователь дополнительного кода в прямой код, блок коррекции, содержащий сумматор по модулю два, вычитающий счетчик и группу сумматоров по модулю два, выходы которых подключены к шине частного устройства, первый вход сумматора по модулю два, первые входы сумматоров по модулю два группы подключены к шине знака устройстваj выход переноса сумматора-вычитателя соединен с вторым входом сумматора по модулю два, инверсный выход сумматора по модулю два соединен со счетным входом вычитающего счетчика. информационный вход которого соединен с выходом шифратора устройства, выходы вычитающего счетчика блока коррекции соединены соответственно с вторыми входами сумматора по модулю два группы, выходы сумматора произведений соединены соответственно с входами первой группы сумматоравычитателя, входы второй группы сумматора-вычитателя соединены соответственно с шиной делимого устройства, управляющий вход сумматоравычитателя соединен с шиной знака устройства, а выходы - с шиной остатка устройства, вход преобразователя дополнительного кода в прямой код соединен с шиной делимого устройства, (Л управляющий вход преобразователя дополнительного кода в прямой код соединен с шиной знака устройства, , а блок уточнения цифры частного содержит первый 21 -входовый элемент И, второй

Изобретение относится к вычислительной технике и может быть применено при разработке быстродействуюuoix устройств деления, обеспечивающих формирование К -разрядных двоич ных цифр частного на каждом шаге деления.. Известно устройство для деления чисел, формирующее в каждом такте разрядов частного и содержащее П-разрядные регистры операндов, сум матор округления, шифратор цифр частного, 1 -разрядных умножителей () сумматор произведений, вычитатель, сумматор частного, блок управления Недостатком известного устройств является относительно низкое быстро действие. Наиболее близким к предлагаемому является устройство для деления п-разрядных чисел, содержащее шифра тор, сумматор произведений, п/1 1,-разрядных умножителей (k 2...и/ а п- разрядность операндов), приче выход шифратора соединен с первыми входами умножителей, вторые входы которых соединены с соответствующей группой k разрядов шины делителя устройства, выходы умножителей соединены с соответствующими входами сумматора произведений С 22. Недостатком этого устройства является большой объем оборудования и низкое быстродействие.

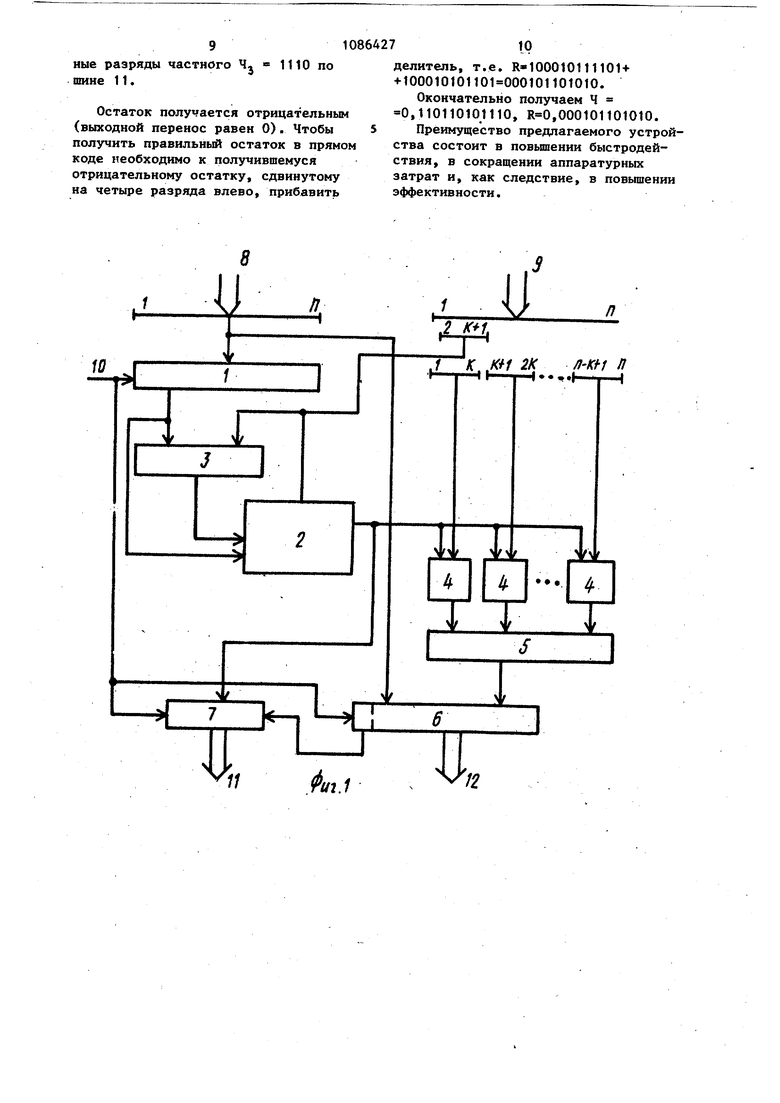

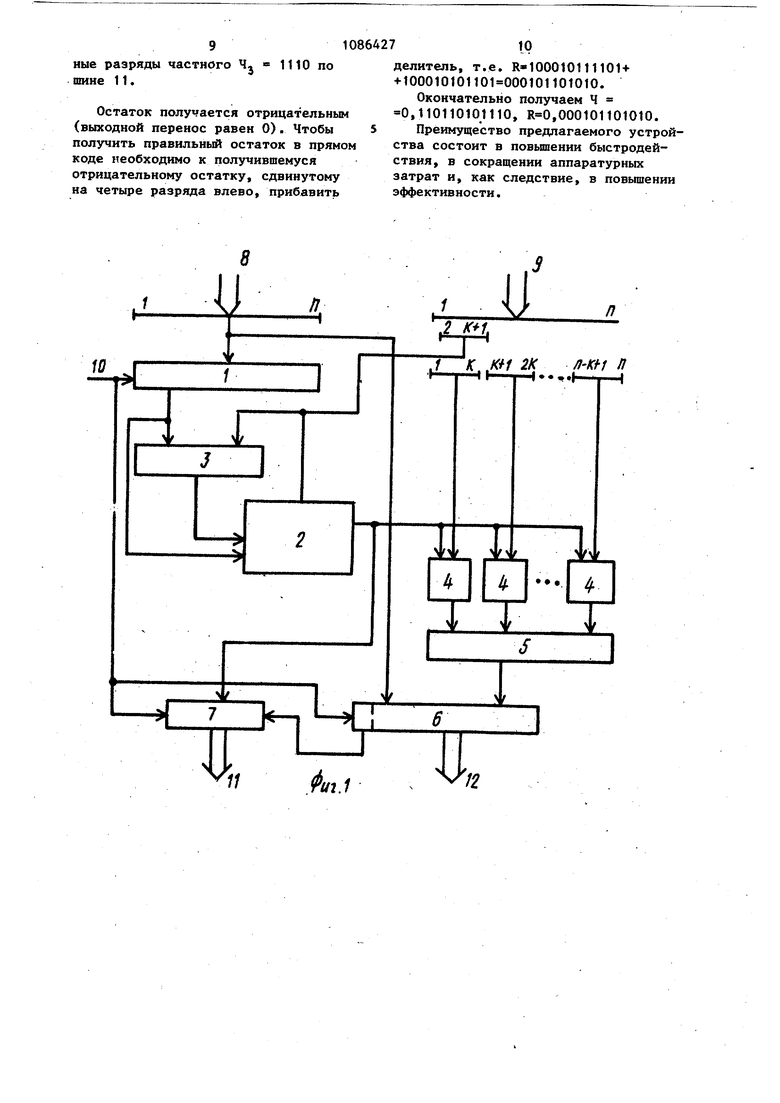

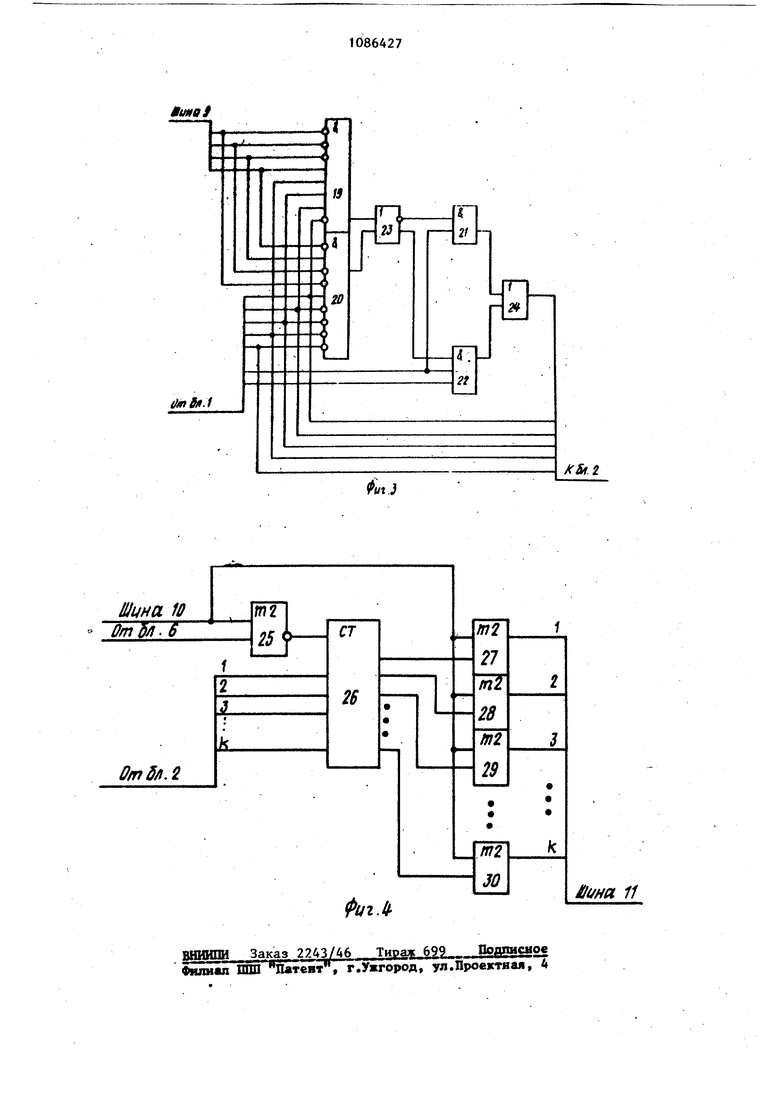

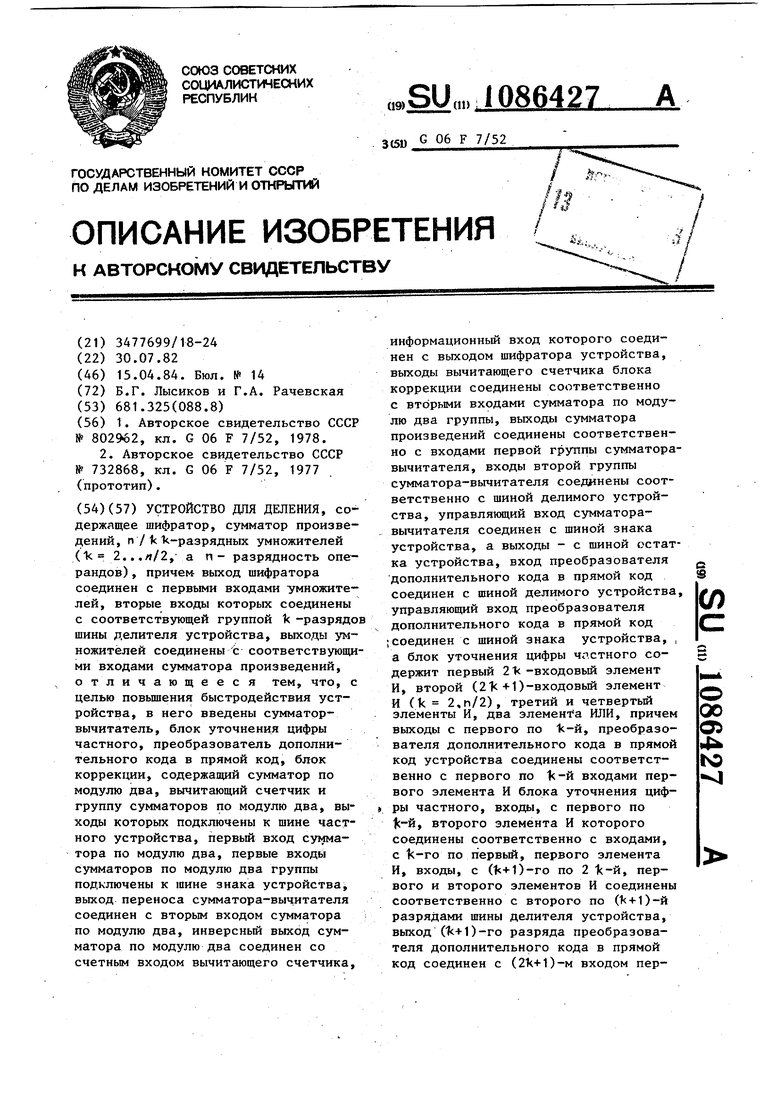

2 Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для деления, содержащее шифратор, сумматор произведений, h /V tc-разрядных умножителей (1 2...П/2, а «-разрядность операндов), причем выход шифратора соединен с первыми входами умножителей, вторые входы которых соединены с соответствующей группой 1 -разрядов шины делителя устройства, выходы умножителей соединены с соответствующими входами сумматора произведений, введены сумматор-вычитатель, блок уточнения цифры частного, преобразователь дополнительного кода в прямой код, блок коррекции, содержащий сумматор по модулю два, вычитающий счетчик и группу сумматоров по модулю два, выходы которых подключены к шине частного устройства, первый вход сумматора по модулю два, первые входы сумматоров по модулю два группы подключены к шине знака устройства, выход переноса сумматора-вычитателя соединен с вторым входом сумматора по модулю два.инверсньй выход сумматора по модулю два соеди-;; иен со счетным входом вычитающего счетчика, информационный вход которого соединен с выходом шифратора устройства, выходы вычитающего счетчика блока коррекции соединены соответственно с вторыми входами сумматоров по модулю два группы, выходы сумматора произведений соединены соответственно с входами первой гру пы сумматора-вычитателя, входы второй группы сумматора-вычитателя сое динены соответственно с шиной делимого устройства, управляющий вход сумматора-вычитателя соединен с шиной знака устройства, а выходы - с шиной остатка устройства, вход преобразователя дополнительного кода в прямой код соединен с шиной делимого устройства, управляющий вход преобразователядополнительного код в прямой код соединен с шиной знака устройства, а блок уточнения цифры частного содержит первый 2)(-входовый элемент И, второй (21;+1)-входовый элемент И (Ic 2,п/2), третий, четвертый элементы И, два элемента ИЛИ, причем выходы, с первого по , преобразователя дополнительног кода в прямой код устройства соединены соответственно с первого по 1.-й взводами первого элемента И блок уточнения цифры частного, входы, с первого по , второго элемента И которого соединены соответственно с входами с tc-ro по первый, первого элемента И, входы, с ()-го по , первого и второго элементов И соединены соответственно с второго по (1.+ 1)-й разрядами шины делителя устройства, выход (1 + 1)-го разряда преобразователя дополнительного код в прямой код которого соединен с ()-м входом первого элемента И блока уточнения цифры частного, вьйс ды первого и второго элементов И которого соединены соответственно с первым и вторым входами первого элемента ИЛИ, прямой и инверсный выходы которого соединены соответстве но с первыми входами третьего и четвертого элементов И, вторые входы которых объединены и подключены к (k+2)-My выходу преобразователя дополнительного кода в прямой код, ()-и выход которого соединен с третьим входом третьего элемента И блока уточнения цифры частного,, первый иВторой входы второго элемента ИЛИ которого соединены соответственн с выходами третьего и четвертого элементов И, выход второго элемента ИЛИ блока уточнения цифры частного, выходы с первого по (К+О-й, преобразователя дополнительного кода в прямой код соединены соответственно с входами первой группы шифратора, входы, с второго по (1с+1)-й, шины делителя соединены соответственно с входами второй группышифратора. На фиг.1 представлена структурная схема устройства для деления; на фиг.2 - структурная схема преобразователя дополнительного кода в прямой код; на фиг.З - структурная схема блока уточнения цифры частного на .фиг.4 - структурная схема блока коррекции. Устройство для деления содержит преобразователь 1 дополнительного кода в прямой код, шифратор 2, блок 3 уточнения цифры частного, умножители 4, сумматор 5 произведений, сумматор-вьгчитатель 6, блок 7 коррекции, шину 8 делимого устройства, шину 9 делителя устройства, шину 10 знака устройства, шину 11 частного устройства, шину 12 остатка устройства. Преобразователь 1 дополнительного кода в прямой код содержит группу сумматоров 13, 14 и 15 по модулю два, сумматор 16 по модулю два, элемент 17 И, суммирующий сметчик 18. Блок 3 уточнения цифры час -ного содержит элементы И 19-22, элементы ИЛИ 23 и 24. Блок 7 коррекции содержит сумма- тор 25 по модулю два, счетчик-вычитатель 26, группу сумматоров 27-30 по модулю два. Преобразователь 1 дополнительного кода в прямой предназначен для преобразования делимого (остатка) из дополнительного кода в прямой код. Блок 3 уточнения цифры частного предназначен для преобразования делимого (остатка) в особых.случаях. Блок 7 коррекции предназначен для исправления текущих k разрядов частного, если они определены неточно. Устройство для деления работает следующим образом. По шинам делимого 8 и делителя 9 в устройство поступают соответственно делимое и делитель в прямом коде без знака. Для определенности полагаем, что в устройстве используется воичная система счисления на кажом такте деления определяется k-4 воичных цифр частногоJ операнды меют вид правильных дробей и нормаизованы (деление целых чисел также озможно при помощи данного устройства при незначительном изменении порядка деления), причем делитель должен fTbiTb больше делимого. По шине 10 знака в устройство подается знак остатка (в исходном состоянии подается логический О) В преобразователе 1 дополнительного кода в прямой код производится преобразование остатка из дополнительного в прямой код, если остаток получился отрицательным (по шине 10 знака пришла логическая 1). С помощью шифратора 2 по 1с+2 раз рядам делимого и по 1 разрядам делителя формируется 1. разрядов частного, причем эта группа разрядов должна получиться либо точно, либо превьш1ать истинную группу на одну единицу младшего разряда (относител но этой группы). с помощью блока 3 уточнения цифры частного осуществляется анализ k+Z разрядов делимого (остатка) и 1 раз рядов делителя, после чего производится их преобразование и передача на шифратор 2. Принцип работы этого блока следующий. В особых случаях Для получения необходимой точности цифры частного необходимо 1(+3 разряда делимого. Чтобы уменьшить объем оборудования, необходимого для шифратора 2, блок 3 уточнения цифры частного преобразует ()-и разряд делимого с учетом (k+3)-ro разряда делимого и 1с разря дов делителя в соответствии со след щей логической функцией, выведенной для . 4, где 2 5 цифры второго - пятого разрядов делителя; 7 - P-J - цифры первого - седьмого разрядов делимого (остат ка) . г - преобразованная цифра шестого разряда делимого (остатка). Цифры остальных разрядов делимого (остатка) передаются на второй вход шифратора 2 без изменения. На фиг.З - приведен пример блока 3 уточнения цифры частного для 1; 4 С помощью умножителей 4 и суммаТора 5 произведений формируется (п+1)-разрядное произведение п -разрядного делителя и 1 цифр частного, полученных с выхода шифратора 2. Сумматор-вычитатель 6 формирует остаток, вычитая из делимого (остатка) произведение делителя на 1с цифр частного, если знак на шине 10 знака положительный, или суммируя эти значения, если знак на шине 10 знака отрицательный. В зависимости от знака предьщущего остатка (шина 10 знака) и выходного переноса, поступающего с второго выхода сумматора-вычитателя 6 на вход блока 7 коррекции, последний осуществляет исправление 1 разрядов частного в соответствии со следующей корректировочной таблицей. Корректировки нет Преобразование цифр частного в прямой код из дополнительногоПреобразование цифр частного в прямой код из обратного На выходные шины 11 частного и 12 остатка подаются соответственно k цифр частного с выхода блока 7 коррекции и остаток с выходным переносом (для формирования знака остатка) с выхода сумматора-вычитателя 6. П р и м е- р. Устройство при ,„ работает следующим образом. Пусть делитель D О,100010101101j делимое Кф О, 0,011101101011; значение частного Ч 0,110110101110. 1-й такт. В преобразователе 1 Дополнительного кода в прямой к-од производится передача цифр старших разрядов делимого (0111011. на вход блока 3 уточнения цифры частного.. Блок 3 уточнения цифры частного по семи цифрам старших разрядов делимого

(0111011) и четырем цифрам второго пятого разрядов делителя (первый разряд всегда равен 1 фиг.З) форми рует шесть преобразованных цифр делимого (011101), которые совместно с цифрами 0001 второго - пятого разрядов делителя подаются на вход шифратора 2, .

На выходе шифратора 2 формируется четыре цифры частного.Ч: 1110.

С помощью умножителей 4 и сумматора 5 произведений формируется произведение П 0,1110 х X О,100010101101 0„0111100101110110.

С помощью сумматора-вычитателя 6 Фоомиоуется очеоедной оста.ток R RQ- П, 0111011010110000 + .+ 1000011010001010 1111110100111010 (выходной перенос равен 0).

Блок 7 коррекции в соответствии с корректировочной таблицей функционирования блока коррекции производит вычитание единицы .из младшего разряда цифры частного Ч Ч-1 1110-0001 1101.

Таким образом, на выход устройства для деления подается остаток R 1111110100111010 и выходной перенос, равный О, по шине 12 остатка, ja также цифры частного 1101 (по -шине 11 частного) .

2-й такт. На шину 9 делителя подается делитель Д 100010101101.

На шину 8 делимого подается остаток, сдвинутый влево на четыре разряда R 110100111010.

На шину 10 знака подается знак остатка, равный 1 (инвертированное значение выходного переноса с второго выхода сумматора-вьгчитателя 6) .

В преобразователе 1 дополнительного кода в прямой код производится преобразование остатка из дополнительного кода в прямой код (на шйне 10 знак равен 1). На его выходе формируется семь цифр остатка (00101 to).

Блок 3 уточнения цифры частного формирует шест цифр остатка (001011

С помощью шифратора 2 по шести цифрам остатка (OOJ011) и четырем цифрам делителя, кроме самого старшего (0001), формируются очередные цифры частного Ч 0101. С помощью умножителей 4 и сумматора 5 произведений формируется произведение П Ч.Д 010x100010101101 0010101101100001. С помощью сумматора-вычитателя 6 формируется очереной остаток Rj R,+n 110100 П10100000+ +0010101101100001 1111111100000001 (выходной перенос равен 0).

Блок 7 коррекции в соответствии с корректировочной таблицей производит преобразование группы цифр частного 42 из обратного кода в прмой код:

Таким образом, на выход устрой; ства подается остаток R2 1111111100000001 и выходной перенос, равный О, по шине 12 остатка и очередные разряды частного Ч- 1010 по шине 11.

3-й такт.

На шину 9 делителя подается делитель Д 100010101101.

На шину 8 делимого подается остаток, сдвинутый влево на четыре разряда R2 11-1100000001.

На шину 10 знака подается знак остатка, равный 1 (инвертированное значение выходного переноса с второго выхода сумматора-вычитателя 6).

В преобразователе 1 дополнительного кода в прямой код производится преобразование остатка из дополнительного кода в прямой код.

На выходе формируется семь цифр остатка (0000111).

БлокЗ уточнения цифры частного формирует шесть цифр остатка (000011).

С помощью шифратора 2 по шести цифрам остатка (000011) и четырем цифрам делителя (0001) формируются очередные цифры 4acTHqifo Ч 0001. С помощью умножителей 4 и сумматора 5 произведений формируется произведение П Д 0001x100010101101 0000100010101101. С помощью сумматора-вычитателя 6 формируется очередной остаток RJ R2+ П 1111000000010000+0000100010101101 1111100010111101 (выходной перенос равен 0).Блок 7 коррекции в соответствии с корректировочной таблицей произведений преобразовывает группу цифр частного Ч из обратного кода в прямой код: Ч,

( 000Up 1110Таким образом, на выход устройства подается остаток Rg 1111100010111101 и выходной перенос, равный О, по шине 12 и очерепные разряды частного 4j 1110 по шине 11.

Остаток получается отрицательным (выходной перенос равен 0). Чтобы получить правильный остаток в прямом коде необходимо к получившемуся отрицательному остатку, сдвинутому на четыре разряда влево, прибавить

и

Фиг.1

делитель, т.е. R-1000101 IIIOH IOOOIOIO1101 000101101010.

Окончательно получаем Ч 0,110110101110, ,000101101010.

Преимущество предлагаемого устройства состоит в повышении быстродействия , в сокращении аппаратурных затрат и, как следствие, в повьштении эффективности.

. и

п

П

Шина 10

KjSnJ

tunef

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Изолирующее кольцо для патрона Эдисона, предохраняющее электрическую лампу накаливания от вывертывания | 1922 |

|

SU802A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-15—Публикация

1982-07-30—Подача