(54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| НОНИУСНЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1997 |

|

RU2128853C1 |

| Устройство для восстановления информации | 1990 |

|

SU1707620A1 |

| Устройство для измерения искажений синхронных телеграфных сигналов | 1978 |

|

SU720772A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Синтезатор частот | 1985 |

|

SU1358092A1 |

i

Изобретение относится к технике связи и может использоваться в устройствах передачи данных.

Известно устройство тактовой синхронизации, содержащее задающий генератор, соединенный с входом блока подстройки частоты, выход которого подключен к входам блока фазовой автоподстройки частоты (ФАПЧ) и блока измерения расстройки, другой вход которого объединен с другим входом блока ФАПЧ 1.

Однако такое устройство имеет невысокую точность.

Цель изобретения - повыщение точности и расширение полосы захвата.

Для этого в устройство тактовой синхронизации, содержащее задающий генератор, соединенный с входом блока подстройки частоты, выход которого подключен к входам блока фазовой автоподстройки частоты (ФАПЧ) и блока измерения расстройки, другой вход которого объединен с другим входом блока ФАПЧ, введены блок определения знака и блок коррекции расстройки, выходы которого подключены к другим входам блока подстройки частоты, причем выходы блока измерения расстройки подключены к блоку коррекции расстройки непосредственно и через блок определения знака.

При этом блок измерения расстройки состоит из двух цепей, каждая из которых содержит последовательно соединенные ключ, счетчик, триггер, при этом выходы триггеров подключены соответственно к первым входам первого, второго, третьего и ч етвертого элементов И и второму входу второго элемента И, выход которого подключен к другому входу счетчика первой цепи и входу элемента ИЛИ, другой вход которого соединен с выходом первого элемента И, другой вход которого соединен с выходом ключа первой цепи, выходы счетчиков подключены соответственно к другим входам третьего и четвертого элементов И, а один из выходов триггера второй цепи подключен к входам ключей, причем другие входы ключей, установочные входы счетчиков и триггеров, третий вход второго элемента И и выходы элемента ИЛИ и третьего и четвертого элементов И являются соответственно входами и выходами блока измерения расстройки.

Кроме того, блок определения знака состоит из триггера, выход которого через первый и второй элементы И подключен к входам элемента ИЛИ, выход которого подключен к входу триггера, при этом другой вход триггера, другие входы элементов И, а также другой выход триггера и выходы элементов И являются соответственно входами и выходами блока определения знака. Блок коррекции расстройки состоит из первого триггера, выходы которого подключены соответственно к первым входам первого, второго, третьего и четвертого элементов И, выходы которых через соответствующие первый и второй элементы ИЛИ подключены к входам триггера, выходы которого подключены к реверсивному счетчику, выход которого подключен к дополнительным входам второго элемента ИЛИ и триггера, при этом входы триггера, вторые входы всех элементов И, третьи входы первого и второго элементов И, второй дополнительный вход элемента ИЛИ, другие входы, а также выходы реверсивного счетчика и выходы триггеров являются соответственно входами и выходами блока коррекции расстройки.

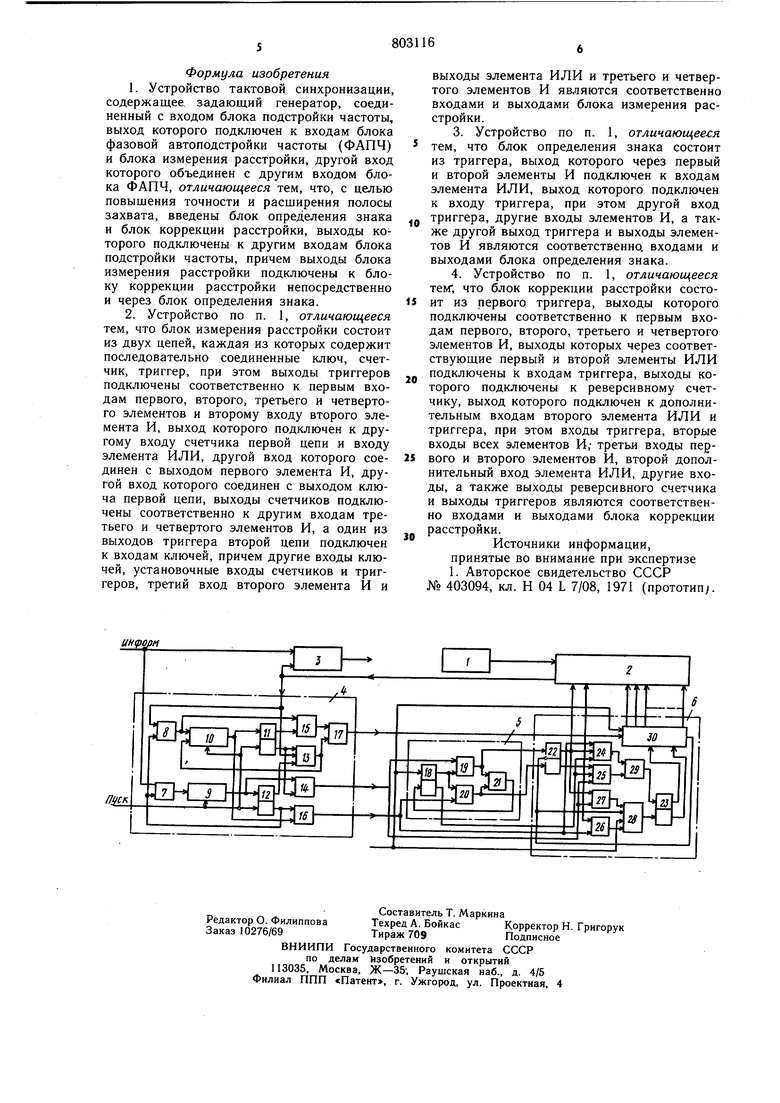

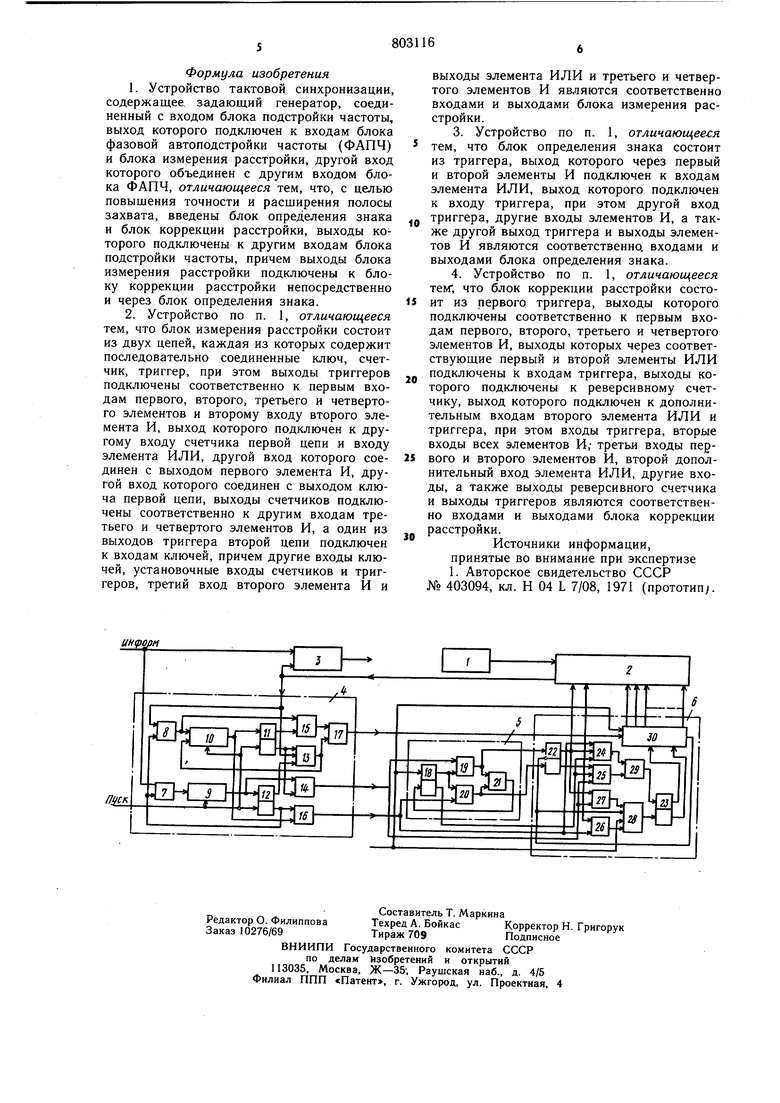

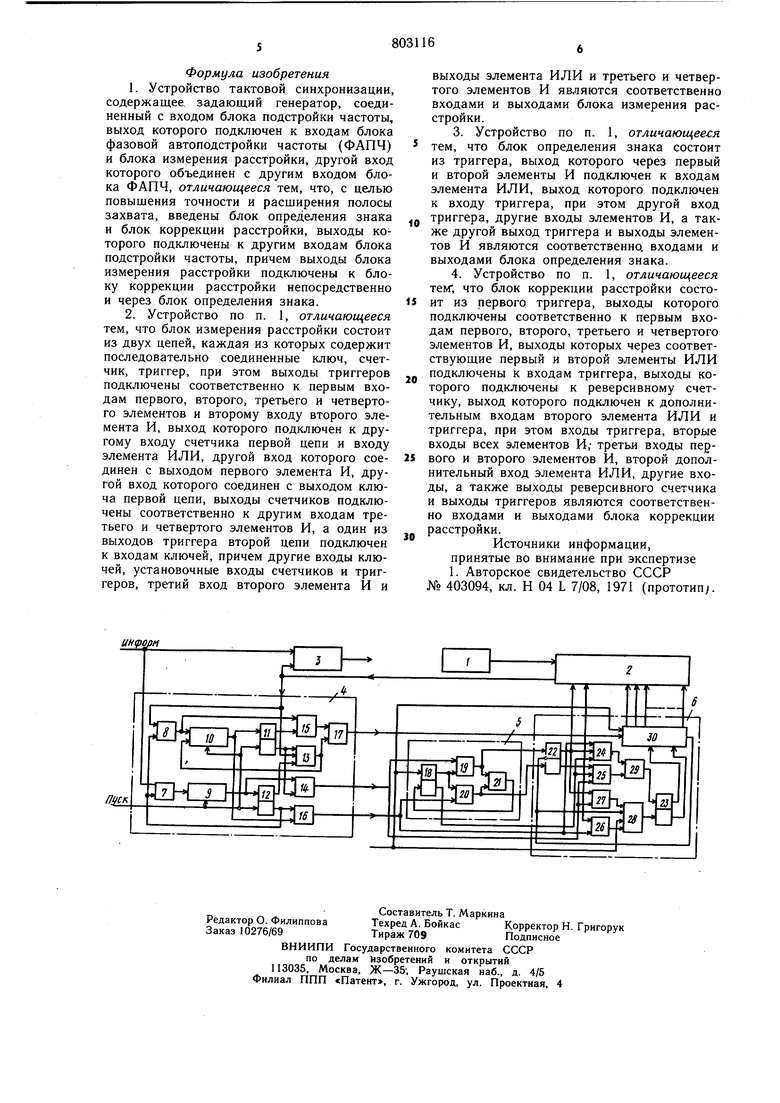

На чертеже дана структурная электрическая схема предложенного устройства.

Устройство содержит задающий генератор 1, блок 2 подстройки частоты, блок 3 фазовой автоподстройки частоты (-ФДПЧ), блок 4 измерения расстройки, блок 5 определения знака и блок 6 коррекции расстройки. Блок 4 измерения расстройки состоит из ключей 7 и 8, счетчиков 9 и 10, триггеров 11 и 12, элементов И 13, 14, 15 и 16 и элемента ИЛИ 17. Блок 5 определения знака состоит из триггера 18, элементов И 19 и 20 и элемента ИЛИ 21. Блок 6 коррекции расстройки содержит триггеры 22 и 23, элементы И 24, 25, 26 и 27, элементы ИЛИ 28 и 29 и реверсивный счетчик 30.

Устройство работает следующим образом.

Блок 5 предназначен для первоначального определения знака расстройки, в дальнейшем блок 5 отключается и знак определяется блоком 6. Наличие блока 5 позволяет ускорить процесс первоначальной подстройки частоты при вхождении в связь. Блок 2 устраняет большие расхождения по частоте на входе блока 3 ФАПЧ. После того блок 3 обеспечивает коррекцию фазы импульсов задающего генератора 1 под фазу входного сигнала с точностью, определяемой шагом коррекции блока 3 ФАПЧ.

Блок 6 с входящим в его состав реверсивным счетчиком 30 является узлом, осуществляющим коррекцию величины расстройки по результатам текущих измерений (измеренная величина расстройки частоты корректируется в реверсивном счетчике 30 по результатам текущих измерений расстройки).

В реверсивном счетчике 30 записано в цифровом коде число, соответствующее ве личине расстройки, измеренной блоком 4.

Вначале генератор 1 имел частоты на К i процентов ниже частоты приходящей информации. При этом в счетчик 30 записано число KI (по результатам измерения блока 4), а блок 5 переводит триггер 22 в состояние, при котором триггер 22 будет выдавать на блок 2 сигнал «добавление. При этом частота опорного сигнала, поступающего на блок 3 и блок 4, увеличится на К i процентов, а следовательно, частота опорного сигнала станет равной частоте приходящего сигнала. Если затем частота приходящего сигнала уменьшится на Ка процентов, а , то блок 4 выдает величину расстройки Кг и знак расстройки «-. В блоке 6 осуществляется коррекция величины расстройки, которая находилась в памяти реверсивного счетчика 30. Так как знак расстройки «-, то новое число Кг записывается в счетчик 30 в режиме обратного счета реверсивного счетчика.В счетчике 30 оказывается записанным новое число Кз К|-Ка, но так как , то в блок 2 поступает сигнал управления « + , определяемый состоянием триггера 22, и частота на выходе блока 2 будет на Кз процентов выше частоты задающего генератора 1.

Так как знак расстройки приходящего сигнала «-, то в реверсивный счетчик 30 новое число начинает записываться в режиме обратного счета. Когда в счетчик 30 будет записано (вычтено) Кз единиц, то он выдаст сигнал по нулевому выходу (число, записанное в реверсивный счетчик 30, становится равным 0). По этому сигналу триггер 22 переводит счетчик 30 в режим прямого счета и в нем будет записано число К5 Одновременно с этим в блок 2 будет выдан сигнал «вычитание. При этом частота на выходе блока 2 будет на К процентов ниже частоты генератора 1.

Таким образом, блок 6 выполняет функции вычисления величин и знака подстройки.

Существенным достоинством измерения разности между уже подстроенной частотой (дифференциального метода измерения и подстройки) является то, что дифференциальный метод измерений и подстройки связан с измерением малых значений, поэтому можно после первоначальной, «грубой подстройки подключить вход блока 4 не к информационному входу устройства, а к выходу блока 3. При этом исключается влияние флуктуации фронтов входного сигнала и еще более повысится точность подстройки, так как блок 3 ФАПЧ будет являться усреднителем фазы фронтов для блока 4.

Возможность работы схемы при больщих, чем в известном устройстве величинах расстройки, расширяет полосу захвата блока 3 ФАПЧ,

Авторы

Даты

1981-02-07—Публикация

1978-10-18—Подача