сд

fts:)

Изобретение относится.к электросвязи, вычислительной технике v- может быть использовано в системах передачи информации с дублированием сообщений.

Целью изобретения является повышение быстродействия устройства.

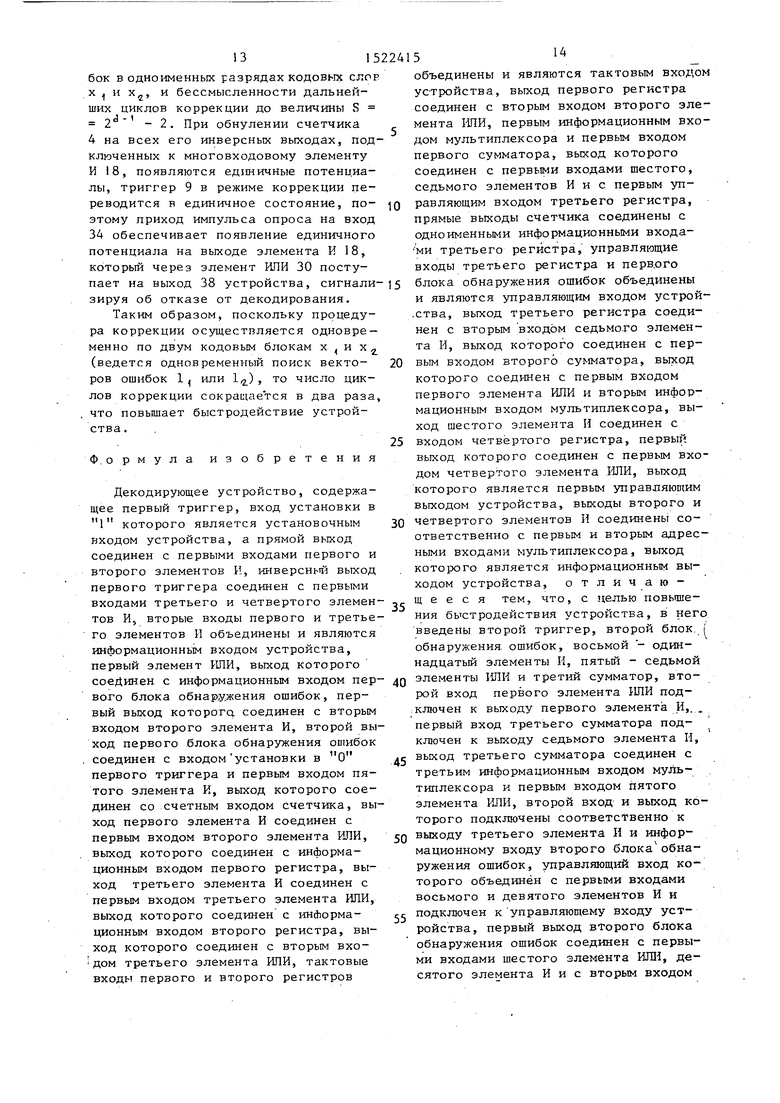

На чертеже представлена функциональная схема устройства..

Устройство содержит первый-третий регистры 1-3 сдвига, счетчик 4 импульсов, четвертый регистр 5 сдвига, первый 6 и второй 7 блоки обнаружения ошибок, первый 8, второй 9 триг- геры, первый-третий сумматоры 10-12 по модулю два, мультиплексор 13, первый 14, третий 15, восьмой 16, пятьтй 17, девятый 18, седьмой 19, шестой 20, второй 21, одиннадцатьй 22, чет- 20 вертый 23 и десятый 24 элементы И, первый 25, пятьй 26, второй 27, третий 28, шестой 29, четвертый 30 и седьмой 31 элементы ИЛИ, установочный 32, информационный 33, управляю- 25 щий 34 и тактовый 35- входы, информа- ционньй выход 36,.второй .37, первый .38 и третий 39 управляющие выходы.

Сущность изобретения состоит в том,зо что перед началом исправления определяется предельное число циклов коррекции, на которых возможно ис-. правление ошибок, процедура исправления осуществляется одновременно в -зс двух кодовых блоках. Если в течение предельного числа циклов коррекции ошибка не найдена, то Устройство выдает сигнал отказа от декодирования. В устройстве осуществляется корректи- до ровка (исправление) методом перебора значений разрядов каждого из двух повторов (п, и)-кода только на тех позициях, где произошло несовпадение двух повторений. При этом корректи- 45 ровка с последующей проверкой на достоверность осуществляется на тактовой частоте, определяемой быстродействием логических элементов и значительно превышающей тактовую частоту ,Q приема кода. При этом суммарное число ощибок в первом и втором повторении

V + 1.

V + 1.

;, - - Л

где V - (п, и)-код;

1, векторы ошибок соответству щих повторов (блоков х и х.) .

в случае необнаружения ошибок (п, и)-кодом в первом .повторении х информация вьщается получателю. Ес в первом повторении ошибка обнаруж на, то принимается второй повтор х которьй также проверяется на налич ошибок, В случае необнаружения оши во втором повторе х информация та же выдается получате.лю. Если и во втором повторе х ошибка обнаружен то выделяется вектор надежности пу сложения по модулю два первого х второго х повторов, т.е.

--1

+ Х V + 1, © V + 1 1,

+ 1,, Е,

причем вектор надежности Е формиру ся одновременно с поступлением вто го повтора х. Если векторы 1 и 1 не содержат единиц в одноименных п ЗИ11ИЯХ, то все ошибки кодовых блок X ( и XQ покрываются вектором Е 1., + Ig.. Если вес вектора Е не п вышает гарантированно обнаруживаем ошибок (п, k)-кoдa, т.е. если - 1 , то осуществЛя т-сА одновременн поиск векторов ошибок 1д для перв го кодового блока х/и 1 для вто го кодового блока х. Так как ошиб могут иметь место только на тех по зициях блоков х и х где у векто ра Е стоят единицы, то поиск векто ошибок 1 и 1 сводится к перебор символов только этих позиций. Всег возможно 2 - 2 двоичных числа (кр ме 0...00 и 1 ... 11) на позициях, гд у вектора Е стоят единицы. Каждое Т: чисел ( - 2) представля собой тест, который одновременно су мируется по модулю два с векторами X , и х.

+ TJ

и х, + Tj

Результаты суммирования х проверяются на нали ошибок (п, k)-кодом. Если в одном результатов ошибка не обнаруживает то это. свидетельствует о том, что найден один из векторов ошибок 1,

ё: d - 1, где d - минимальное кодо- 1„, т.е. 1 V l,j Т и дальнейшее t

вое расстояние (п, k)-кoдa.

Содержание алгоритма декодирования состоит Б следующем. Кодовые блоки х, и х, прршимаемые из канала связи, представляются следующим образом:

декодирование прекращается, так ка

(х, + Тр V (х + Т) (V + Ц ® ® 1, )( (v + 1 © Ij) V.

Отказ от декодирования происход в том случае, если вектор ошибок н

V + 1.

V + 1.

;, - - Л

где V - (п, и)-код;

1, векторы ошибок соответствующих повторов (блоков х и х.) .

в случае необнаружения ошибок (п, и)-кодом в первом .повторении х, информация вьщается получателю. Если в первом повторении ошибка обнаружена, то принимается второй повтор х, которьй также проверяется на наличие ошибок, В случае необнаружения ошибо во втором повторе х информация также выдается получате.лю. Если и во втором повторе х ошибка обнаружена, то выделяется вектор надежности путе сложения по модулю два первого х и второго х повторов, т.е.

--1

+ Х V + 1, © V + 1 1,

+ 1,, Е,

причем вектор надежности Е формируется одновременно с поступлением второго повтора х. Если векторы 1 и 1 не содержат единиц в одноименных по- ЗИ11ИЯХ, то все ошибки кодовых блоков X ( и XQ покрываются вектором Е . 1., + Ig.. Если вес вектора Е не превышает гарантированно обнаруживаемых ошибок (п, k)-кoдa, т.е. если - - 1 , то осуществЛя т-сА одновременный поиск векторов ошибок 1д для первого кодового блока х/и 1 для второго кодового блока х. Так как ошибки могут иметь место только на тех позициях блоков х и х где у вектора Е стоят единицы, то поиск векторов ошибок 1 и 1 сводится к перебору символов только этих позиций. Всего возможно 2 - 2 двоичных числа (кроме 0...00 и 1 ... 11) на позициях, где у вектора Е стоят единицы. Каждое из Т: чисел ( - 2) представляет собой тест, который одновременно суммируется по модулю два с векторами X , и х.

+ TJ

и х, + Tj

Результаты суммирования х, + проверяются на наличие ошибок (п, k)-кодом. Если в одном из результатов ошибка не обнаруживается, то это. свидетельствует о том, что найден один из векторов ошибок 1, или

1„, т.е. 1 V l,j Т и дальнейшее

1„, т.е. 1 V l,j Т и дальнейшее

декодирование прекращается, так как:

(х, + Тр V (х + Т) (V + Ц ® ® 1, )( (v + 1 © Ij) V.

Отказ от декодирования происходит в том случае, если вектор ошибок не

515

найден до j 2 - 2, где w - ве вектора ошибок. Это сввдетельствует о том, что ошибка произошла в одноименных разрядах х и х (неисправимая ошибка) и дальнейшее тестировани кодовых блоков К;, и x,j до величины j 2 - 2 бесполезно. Кроме того, отказ от декодирования происходит и в том случае, если вес вектора ошибо Е превьшает кратность гарантированно обнаруживаемых ошибок (п, k)-кодом, т.е. если Ь d - 1. Отказ от декодирования, равнозначен запросу следующего кодового блока х и т.д.

Разрядность приемньпс регистров 1 , 2 определяется длиной кодовых блоков X , и х,2.. Объем регистра 5 сдвига оп- ределяется обнаруживающей способнос- .тью (п, и)-кода, т.е. величиной d-1, В регистр 5 через элемент И 20 запи- сьшается вес вектора ошибок Е, который образуется на выходе сумматора 10 по модулю два. Регистр 5 может быть выполнен на D-триггерах, причем счетный его вход образуется путем соединения D-входа и тактового входа нулевого разряда, а прямые выходы предыдущих разрядов соединяются с D-вкодами последующих разрядов. Так- товые входы всех разрядов объединены. Р1нформационные выходы регистра 5, начиная с первого разряда, подключены к информационным входам счетчика 4. Таким образом, количество единиц, записываемых в регистр 5, равно весу вектора ошибок Е, а в счетчик 4 записьюается на одну единицу меньше (нулевой разряд регистра сдвига 5 не подключен к информационному входу

счётчика А). Если вес вектора ошибок превышает обнаруживающую способность (п, и)-кода, т.е. величину d - I, то с выхода переполнения регистра 5 через элемент ИЛИ 30 снимается импульс переполнения, который свидетельству- ет об отказе от декодирования. -Счетчик 4 импульсов определят номер контрольного теста, объем счетчика 4 определяется минимально допустимым числом контрольных тестов Т;, не приводящих к размножению необнаруживаемых ошибок.

Сдвиговый регистр 3 контрольного теста совместно с элементом И 19 предназначен для формирования конт- рольных тестов Т. , служащих для идентификации вектора ошибок 1 для кодового слова х или вектора ошибок l

5

0 5 о

5

для кодового слова х. Разрядность регистра 3 определяется из соотношения

llog,(2 - 2)Г- I п, + п„,

округление до целого числа

в сторону увеличения; d - минимальное кодовое расстояние (п, и)-кода; п - количество разрядов, равное разрядности счетчика импульсов 4;

п - дополнительный нулевой разряд., Программу сдвига в регистре 3 задает вектор надежности (х + х ) 1, t Ij,, который образуется на -выходе сумматора 10 по модулю два. Для этого первый синхровход С, регистра 3 связан с выходом сумматора 10. Результат сдвига записьшается в нулевой разряд, являющийся выходом регистра 3, который подключен к второму входу элемента И 19. Значение нулевого разряда регистра 3 совместно с вектором надежности Е 1( + Ij, определяет для каждого теста Т; лози- ции, на которых необходимо корректировать fинвертировать) значения векторов X , и х. С этой целью другой вход элемента И 19 подключен к выходу сумматора 10. Этот вход выполнен задержанным на время, обеспечивающее окончание переходных процессов при сдвиге информации в регистре 3. Таким образом.

Т g,E4

где Т- - значение контрольного теста н а i-M такте;

п и Е - значения соответственно нулевого разряда Пд и вектора Е на i-M такте каяадого

цикла коррекции.

Второй синхровход С регистра 3 обеспечивает считывание содержимого счетчика 4 в разряды с первого по т-й.

Сумматоры 11 и 12 по модулю два осуществляют коррекцию векторов х и х на позициях, которым соответствуют значения единиц в контрольном тесте Т.

Мультиплексор 13 осуществляет коммутацию каналов в зависимости от того, на каком цикле работы устройства блоки обнаружения ошибок 6 или 7 выработают сигнал об отсутствии ошибок

Если ошибка отсутствует при приеме первого кодового .блока х,, то информация получателю вьдается по первому каналу, если при приеме второго кодового блока х, - то по второму каналу. Если при коррекции ошибки отсутствуют в блоке X ;, + Т то информация выдается по третьему каналу, если ошибки отсутствуют в блоке х, Т,, то информация вьщается по четвертому каналу.

Элемент ИЛИ 30 объединяет сигналы отказа от декодирования, снимаемые с выхода переполнения регистра 5 и с выходов обнуления счетчика 4 (через элемент И 18) на выход 38 устройства. Элемент ИЛИ 31 объединяет сигналы коррекции, снимаемые с выходов элементов И 16 и 17 на выход 39 устройства,

В исходном состоянии триггеры 8 и 9, регистры 1, 2, 3 и 5 и счетчик 4 обнулены.

Устройство может работать в еле- дующих режимах.

Режим ретрансляции кодовых блоков X и x,j возможен в случае необнаруже- ния ошибок блоками 6 и 7 обнаружения ошибок в словах х или х.

В режим/ коррекции ошибок устройство переходит лишь в случйе обнарут жения ошибок блоками 6 и 7 в первом Xj и во втором -Xii кодовых словах.

Информация, поступающая по окончаНИИ циклового фазирования на вход 33 устройства, записьтается в регистры 1 или 2 на тактовой частоте f, (вход 35 устройства). Вьодача информации из регистров 1 или 2 осуществляется на тактовой частоте ,. Смена частоты следования синхроимпульсов на входе 35 устройства определяется наличием сигнала на выходе 37 устройства либо переходом устройства в режим коррекции в случае наличия сигнала на выходе 39.

Устройство работает следующим образрм.

На вход 32 поступает импульс, ко- торьй переводит триггер 8 в единичное состояние. Это свидетельствует о том, что устройство готово к приему первого кодового блока х, в регистр 1, По окончании циклового фазирования (поиска маркера блока х)

с входа 33 первый кодовый блок х через элемент И 14, открытый единичным потенциалом, снимаемым с прямого вы5

х

5

0

35

40

45

50

55

хода триггера 8, и элемент ИЛИ 27 по- ступает на информационный вход регистра 1, на синхровход которого с входа 35 поступают п синхроимпульсов с частотой f.

Одновременно кодовый блок х, через элемент ИЛИ 25 поступает на информационный вход блока 6 обнаружения ошибок, где осуществляется проверка на достоверность блока х, (п, k)-кодом (например, для разделимого циклического кода деления на образующий полином). По окончании записи блока Xj в регистр 1 с входа 34

----.., - ,

устройства поступает импульс опроса состояния блока 6. Если блок 6 ошибки не обнаруживает, то на первом его выходе (выходе отсутствия ошибки) появляется сигнал, который через элемент И 21 (на .второй вход которого поступает единичный потенциал с прямого выхода триггера 8), поступая на первый адресньй вход мультиплексора 13, подготавливает последний к вьща- че информации на выход 36 устройства по первому каналу, т.е. с выхода регистра 1 . Этот же сигнал, поступая через элемент ИЛИ 29 на выход 37 устройства, обеспечивает поступление на вход 35 устройства п синхроимпульсов частоты f,j,, под действием которых достоверно принятый блок х,. через мультиплексор 13 считьшается на выход 36 устройства (при использовании разделимого (п, k)-кoдa считываются только первые k разрядов, т,е. на вход 35 устройства поступают k синхроимпульсов частоты fji). В этом режиме регистр 5 находится в нулевом состоянии, так как подключенный к его информационному входу элемент И 20 закрыт нулевым потенциалом, снимаемым с инверсного выхода триггера 8. Поэтому счетчик 4 и регистр 3 обнулены, на вькоде элемента И 19 постоянно присутствует нулевой потенциал и сумматор 11 по модулю два влияния на работу устройства не ока- .зьшает.

Если блок 6 обнаруживает ошибку,- то на его втором выходе (выходе на-. личия ошибки) появляется импульс, который обнуляет блок 6 (на схеме не показано, но может быть реализовано как сброс элементов памяти декодера циклического кода) и переводит триггер 8 в нулевое состояние. ;Через

элемент И 17 этот импульс не проходит, так как на втором выходе блока 7 присутствует нулевой потенциал. Таким образом, устройство подготовлено для приема второго кодового блока х.

Второй кодовый блок по окончании его u iклoвoгo фазирования, поступая на вход 33 устройства на тактовой частоте f, через открытые элементы И 15 и ИЛИ 28 записьгоается в регистр 2, а через элемент ИЛИ 26 проверяется на достоверность блоком 7. Одновременно под действием синхроимпуль

циал с инверсного выхода триггера 9, на первом - импульс опроса, а на втором - сигнал ошибки блока 7. Элемент И 17 не срабатывает, так как на третьем его входе присутствует нулевой потенциал, снимаемый с прямого выхода триггера 9. Импульс с выхода элемента И 16, поступая на вход счетчика 4, обеспечивает запись в него содержимого регистра 5, начиная с первого разряда, а поступая на вьтход 39 через элемент lUlK 31 , свидетельствует о переходе устройства в режим коррек

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1446695A1 |

| Устройство для приема многократно передаваемой информации | 1989 |

|

SU1647914A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

Изобретение относится к электросвязи, вычислительной технике и может использоваться в системах передачи информации с дублированием сообщений. Устройство в случае необнаружения ошибок в первом или втором повторении принимаемого сообщения выдает его получателю. В противном случае осуществляется коррекция одновременно двух принятых сообщений, что повышает быстродействие устройства. Устройство содержит регистры 1-3, 5 сдвига, счетчик 4 импульсов, блоки 6, 7 обнаружения ошибок, триггеры 8, 9, сумматоры 10-12 по модулю два, мультиплексор 13, элементы И 14-24, элементы ИЛИ 25-31, установочный 32, информационный 33, управляющий 34 и тактовый 35 входы, информационный 36 и управляющие 37-39 выходы. 1 ил.

сов f через элемент ИЛИ 27 осуществ- t5 дии. Таким образом, -в режим коррекции

устройство переходит в случае обнаружения ошибок блоком 6 в первом х, и блоком 7 во втором х кодовых блоках.

Коррекция сводится к инвертированию разрядов кодовых блоков х и х, которые определяются единичными разрядами вектора ошибок Е 1 + 1. Позиции кодовых блоков х ИХ-, подлежащие инвертированию, определяются методом перебора и задаются контрольным тестом Т.

Номер (J) теста Т; задается состоянием счетчика 4 импульсов. Поэтому перед началом очередного цикла , коррекции содержимое счетчика 4 - пере - письшается в- разряды регистра 3, начиная с первого разряда регистра 3. Мультиплексор J3 заблокирован отсутствием сигналов на его адресных вхо- дах АО-АЗ. Сдвиг информации в регистрах I и 2 осуществляется под действием синхроимпульсов частоты f. .

Таким образом, если, например, при записи второго кодового блока х сумматором 10 по модулю два вьщелено три импульса несовпадения, то регистр 5 сдвига находится в состоянии 0. .. 111 , импульсом с выхода элемента И 16 в счетчик 4 с регистра 5 запн- сьшается состояние O...I1 (нулевой разряд регистра 5 не подключен к информационным входам счетчика 4), а задним фронтом сигнала опроса, поступающего на вход С- регистра 3, в последний записьшается состояние 0...110 (выходы счетчика 4 подключены к информационным входам регистра 3, начиная с первого, а выходом.регистра 3 является выход его нулевого

ляется перезапись содержимого регистра I , а на сумматоре 10 по модулю два осуществляется сложение кодовых блоков х и X . Так как на первых двух входах элемента И 20 присутствует 20 единичный потенциал, снимаемый с инверсных вькодов триггеров 8 и 9, находящихся в нулевом состоянии, то импульсы несовпадения кодовых блоков х и X2 (вектор ошибок Е) через элемент 25 И 20 последовательно заполняют регистр 5 сдвига. Через элемент И 19 импульсы несовпадения не проходят, так как счетчик 4 и регистр 3 нахо- дятся в нулевом состоянии. По окон- ЗО чании записи второго кодового блока х в регистр 2 на вход 34 устройства

; поступает второй импульс опроса. При этом блок 6 снова подтверждает наличие ошибки. Если блоком 7 ошибка не обнаружена, то на его первом вьгходе появляется сигнал отсутствия ошибки, который через элемент ИЛИ 29 поступает на выход 37 устройства, а через элемент И 23, на другом входе которого присутствует единичный потенциал с инверсного выхода триггера 8, поступает на адресньй вход А1 мультиплексора 13, подготавливая его для . вьщачи информации на выход 36 устрой- 5 ства по второму каналу, т.е. с выхода регистра 2. Считьюание достоверно принятого в регистр 2 кодового блока Xj осуществляется также под действием синхроимпульсов частоты f.

Если и после приема второго кодового блока Xj. обнаружена ошибка в

« блоке 7, то под действием импульса, - поступающего на вход 34, на вторьк

35

40

50

выходах блоков 6 и 7 обнаружения оши-

бок одновременно появляются единичные потенциалы. При этом срабатьшает элемент И 16, так как на его третьем входе присутствует единичный потен

5

35

5

40

5

50

Так как вектор надежности Е задает, программу сдвига в регистре 3, то на первом цикле коррекции, т.е. для первого теста Т,, сдвиг информации

в регистре 3 осуществляется по перед- нему фронту первого импульса на вьтхо- де сумматора 10. Если, например, несовпадение в третьих разрядах первого и второго кодовьк слов к и х, то первый импульс появляется на вьгходе сумматора 10 только на третьем такте () в первом цикле (j 1) коррекции. По этому сигналу осуществляется сдвиг в регистре 3, и он перехо- дит в состояние О...Oil. Наличие единицы в нулевом разряде (п) регистра 3, с выходом которого связан вход элемента И 19, обеспечивает про- хождение единичного сигнала с выхода сумматора 10 через задержанный на время срабатывания регистра 3 вход элемента И 19 ка входы сумматоров 11 и 12 только на третьем такте работы устройства в первом цикле коррекции. Это соответствует инвертированию сумматорами 11 и 12 содержимого третьих разрядов кодовых слов х и х. Следующий единичньш сигнал с выхода сум- матора 10 осуществляет второй сдвиг в регистре 3 и переводит его в состояние 0...001, а также инвертирует содержимое соответствующих разрядов кодовых слов х и х,2. Приход третье- 1.го. импульса с сумматооа 10 переводит регистр 3 в состояние 0...000. Такое состояние регистра 3 свидетельствует о том, что больше ни на одном такте работы устройства в первом цикле коррекции с выхода элемента И 19 единич ный сигнал сниматься не будет. Если первый тест совпадает с -вектором ошибки в первом х ипи во втором х. кодовом слове, то происходит коррек- ция fисправлениеJ этой ошибки. Результат суммиров ания по модулю два кодового слова х с первым тестом Т, с выхода сумматора 11 через элемент ИЛИ 25 поступает на вход блока 6, где проверяется на достоверность, а результат суммирования по модулю два кодового слова х с первым тестом Т с выхода сумматора 12 через элемент ИЛИ 26 поступает на вход блока 7, где проверяется на достоверность. Если ошибка не обнаружена блоком 6, то состояние счетчика 4 не меняется, в регистр 3 задержанным импульсом опроса записывается снова номер первого теста, и мультиплексор 13 через элемент И 22 подготавливается для вьщач информации на выход 36 устройства по третьему каналу. Если блок 7 ошибку

О Q с

5

0

5

не обнаруживает, то также в регистр 3 записывается номер первого теста, мультиплексор 13 через элемент И 24 подготавливается для выдачи информации на выход 36 устройства по четвертому каналу. Таким образом, с выхода 36 устройства по окончании первого цшсла коррекции в случае необнаружения ошибок блоком 6 считьгоается кодовое слово X, + Т - V, так как в этом случае Т, 1, , а в случае необнаружения ошибок блоком 7 считьтается кодовое слово X 2 + Т V, так как в этом случае т, 1. Если.оба блока 6 и 7 обнаруживают ошибку, то устройство переходит на второй цикл коррекции. По импульсу опроса блоки 6 и 7 выдают сигналы наличия ошибки, за счет чего срабатьшает элемент И 17 и сигнал с его выхода вычитает единицу из счетчика 4 (0...10), состояние которого записьшаетЬя в регистр 3 (0...100).

В дальнейшем работа устройства аналогична работе на первом цикле коррекции. Отличие состоит лишь в том, что при первом сдвиге (т.е. на первой единичной позиции вектора надежности Е) в ре.гистре 3 его нулевой разряд не пpшiимaeт ед ничного значения, так как состояние регистра 3 0...010. Нулевой разряд п регистра 3 на втором цикле коррекции (j 2) принимает единичное значение только на такте, соответствующем номеру второго единичного разряда вектора на- дежности Е.-Это означает, что коррекция ошибки в кодовых словах х и х, происходит только на позиции, соот- ветствующей номеру второго единичного разряда вектора надежности Е.

В случае необнаружения ошибки блоком 6 на выходе 36 считьюается кодовое слово х + Т 2, так как в этом случае Т 1, , при необнаружении ошибки блоком 7 на выходе 36 считывается кодовое слово х, + Т, так как при этом Т 1. Если блоки 6 и 7 в этих -кодовых словах обнаруживают . ошибку, то устройство переходит на третий цикл коррекции.

Режим коррекции продолжается до тех пор, пока не будет найден вектор ошибок 1 Тj или 1 TJ .либо пока состояние счетчика 4 в процессе вычитания не станет равньп нулю, что свидетельствует о наличии неиспрайимь х ошибок в кодовых словах х и «,т. е. ошибок в одноименных разрядах кодовмх сло X . и X,

и бессмысленности дальней- коррекции до величины S

1 z ших циклов

, ,- - 2 2. При обнулении счетчика 4 на всех его инверсных выходах, подключенных к многовходовому элементу И 18, появляются ед1шичные потенциалы, триггер 9 в режиме коррекции переводится в единичное состояние, поэтому приход импульса опроса на вход 34 обеспечивает появление единичного потенциала на выходе элемента И 18, который через элемент ИЛИ 30 поступает на выход 38 устройства, сигнали зируя об отказе от декодирования.

Таким образом, поскольку процедура коррекции осуществляется одновременно по двум кодовым блокам : и х (ведется одновременный поиск векто- ров ошибок 1 или .) то число циклов коррекции сокращается в два раза что повышает быстродействие устройства.

Ф.ормула изобретения

Декодирующее устройство, содержащее первый триггер, вход установки в 1 которого является установочным входом устройства, а прямой выход соединен с первыми входами первого и второго элементов И., инверсньй выход первого триггера соединен с первыми входами третьего и четвертого элементов И, вторые входы первого и третьего элементов И объединены и являются информационным входом устройства, первый элемент ИЛИ, выход которого соединен с информационным входом первого блока обнарУ;Жения ошибок, первый выход которого, соединен с вторым входом второго элемента И, второй выход первого блока обнаружения ошибок соединен с входом установки в О первого триггера и первым входом пятого элемента И, выход которого соединен со счетным входом счетчика, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с информационным входом первого регистра, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен с информационным входом второго регистра, выход которого соединен с вторым вхо- iдом третьего элемента ИЛИ, тактовые входи первого и второго регистров

0

5

0

5

0

5

5

объединены и являются тактовым входом устройства, выход первого регистра соединен с вторым входом второго элемента ШИ, первым информационным входом мультиплексора и первым входом первого сумматора, выход которого соединен с первыми входами шестого, седьмого элементов И и с первым управляющим входом третьего регистра, прямые выходы счетчика соединены с одноименными информационными входа- ми третьего регистра, управляющие входы третьего регистра и перв.ого блока обнаружения ошибок объединены и являются управляющим входом устрой- -ства, выход третьего регистра соединен с вторым входом седьмого элемента И, выход которого соединен с первым входом второго сумматора, выход которого соединен с первым входом первого элемента ИЛИ и вторым информационным входом мультиплексора, выход шестого элемента И соединен с входом четвёртого регистра, первый выход которого соединен с первым входом четвертого элемента ИЛИ, выход которого является первым управляюпщм выходом устройства, выходы второго и четвертого элементов И соединены соответственно с первым и вторым адресными входами мультиплексора, выход которого является информационным выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него, введены второй триггер, второй блок. (

5

обнаружения ошибок, восьмой - одиннадцатый элементы И, пятый - седьмой Q элементы IfflH и третий сумматор, второй вход первого элемента ИЛИ под- :ключен к выходу первого элемента И,. первый вход третьего сумматора подключен к выходу седьмого элемента И, выход третьего сумматора соединен с третьим информационным входом мультиплексора и первым входом пятого элемента ИЛИ, второй вход- и выход которого подключены соответственно к выходу третьего элемента И и информационному входу второго блока обнаружения ошибок, управляющий вход которого объединён с первьтми входами восьмого и девятого элементов И и подключен к управляющему входу устройства, первый выход второго блока обнаружения ошибок соединен с первыми входами шестого элемента ИЛИ, десятого элемента И и с вторым входом

0

15

четвертого элемента И, второй выход блока обнаружения ошибок соединен с вторыми входами пятого, восьмого элементов И и входом установки в 1 второго триггера,- прямой выход которого соединен с третьим входом пятого элемента И, вторыми входами девятого, десятого и первым входом одиннадцатого элементов И, инверсный вы- ход второго триггера соединен с третьим входом восьмого элемента И и вторым входом шестого элемента И, третий вход которого подключен к инверсному выходу первого триггера, вы ход восьмого элемента И соединен с тактовым входом счетчика и первым входом седьмо.го элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, вторые выходы чет- вертого регистра .соединены с .одноименными информационными входами счетчика, инверсные выводы которого

16

соединены с одноименными третьими входами девятого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, вторые входы первого и второго сумматоров подключены к выходам соответственно третьего элемента ИЛИ и первого регистра, вторые входы .одиннадцатого элемента И и шестого элемента ИЛИ объединены и , подключены к первому выходу первого блока обнаружения ошибок, выходы десятого и оданнадцатого элементов И соединены соответственно с третьим и четвертым адресными входами мультиплексора, четвертый информационный вход КОТОРОГО Объединен с вторым входом третьего сумматора и подключен к выходу второго регистра, выходы шестого и седьмого элементов ИЛИ являются соответственно вторым и третьим управляющими выходами устройства.

| Устройство для исправления ошибок в кодовой комбинации | 1976 |

|

SU599267A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-23—Подача