00 00

ю

Изобретение относится к вычислительной технике и технике связи и может быть использовано в устройствах защиты от ошибок систем передачи и обработки дискретной информации, а также в системах дальне связи с дублированием сообщений (например, в системах с решающей обратной связью).

Цель изобретения - повышение достоверности и информативности устройства .

Поставленная цель достигается тем, что в устройстве, благодаря введению специальных технических средств, oc цecтвляeтcя корректировка (исправление) методом перебора значений разрядов одного из двух повторений (п,и)-кода только на тех позициях, где произошло несовпадение двух повторений. При этом, корректировка с последующей проверкой на достоверность осуществляется на тактовой частоте, определяемой быстродействием логических элементов и значительно превьапающей тактовую час тоту приема повторений (п,К)-кода.

Это обеспечивает без дополнительного введения информационной избыточ ности, по OTHOitjeHHKj к известному уст ройству,корректировку (d-2) ошибок во втором повторении, и на этой осно ве прием сообщения, соответствующего истинному, с вероятностью, не ниже чем в известном устройстве и за значительно меньшее время, чем при повт торном приеме двухкратного или однократного повторения (п.К)-кода.

Содержание реализованного в предлагаемом устройстве нового алгоритма декодирования состоит в следующем. Кодовые блоки Х, и Х, принимае мые из канала, связи представляются следующим образом.

XI

@ 1,; Х2 S ® 1;

где Ь - (п,и)-код; 1, и 1. вектора опшбок соответствующих повторов fблоков X, и X,). В случае необнаружения ошибок (п,k)-кoдoв .в первом повторении X , информация выдается получателю. Если в первом повторении ошибка обнаружена, то принимается второй повтор Х, который также повторяется на наличие ошибок. В случае необнар жения ошибок во втором повторе Х информация также выдается получателю. Если во втором повторе Х ошибка обнаружена, то выделяется вектор надежности путем сложения по модулю два первого X, и второго Х гтовторов, т.е.

Х1®Х2 ©1.. 1,©Ц Е,

10 Если векторы 1, и 1 не содержат единиц в одноименнь(х позициях, то все ошибки вектора Х или Х покрываются вектором (liQlj) Е. Одновременно подсчитывается число еди15 ниц в векторе Е. Если вес вектора Е не превьпиает кратность гарантированно обнаруживаемых ошибок (n,k)-KO- да, т.е. b : d-1, то осуществляется поиск вектора ошибок 1 для вто20 рого вектора Х. Так как ошибки могут иметь место только на тех позициях блока Xj, где у вектора Е стоят единицы, то поиск вектора ошибок 1 сводится к перебору симво25 лов только этих позиций. Всего возможно (2 -2) двоичных чисел (кроме 00...0 и 1 I . . . 1 на позициях, где у вектора Е стоят единицы. Каждое из Т; чисел (О « j 2 ) представля- 30 ет собой тест, которьй суммируется по модулю два с вектором Х. Результат суммирования проверяется по наличию ошибок (п.k)-кодом. Если ошибка не обнаруживается. это свидетельствует о том, что вектор ошибок lj найден, т.е. 12 -Т , и дальнейшее декодирование прекра- щается, т.е.

40 Х,®Т 8©1,©1 .

35

Отказ от декодирования происходит в случае, если вектор ошибок не найден до j 2 -2. Это свидетельствует о том, что ошибка произогша

в одноименных разрядах X, и Х, т.е. неисправная ошибка. Кроме того, отказ от декодирования происходит и в случае, если вес вектора Е превьш1ает кратность гарантированно обнаруживаемых ошибок (n,k)-кодом, т.е. если . Отказ от декодирования равнозначен запросу следующего блока X } т.д.

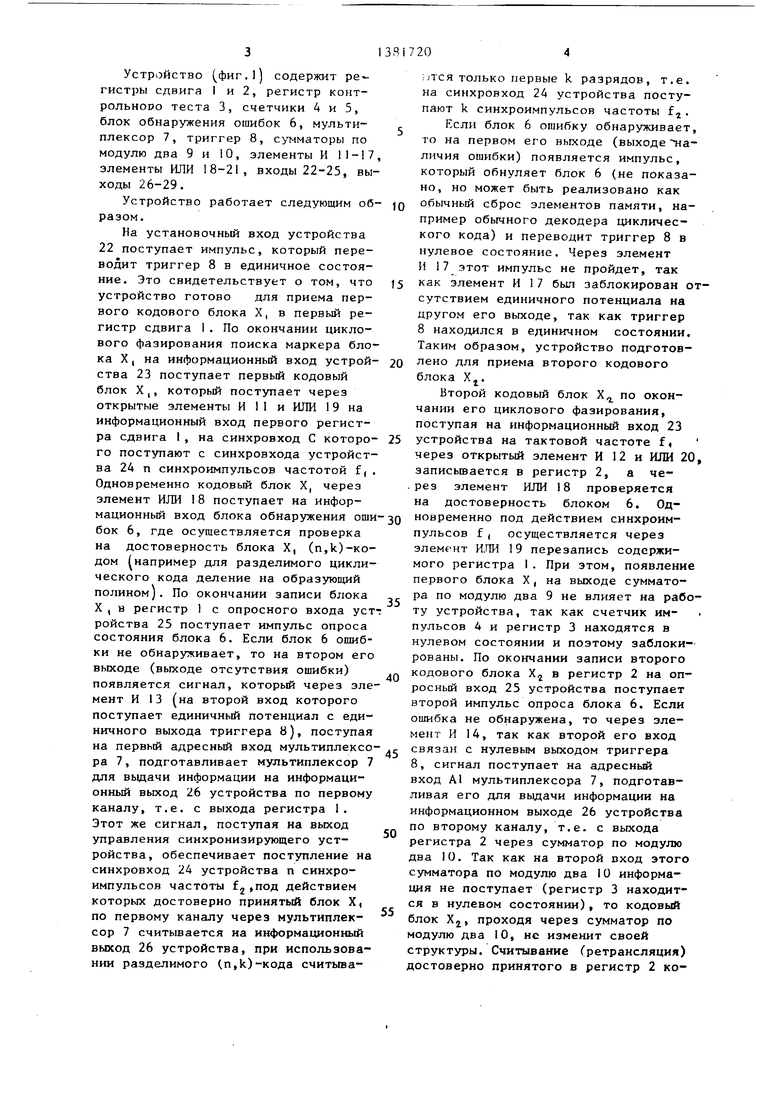

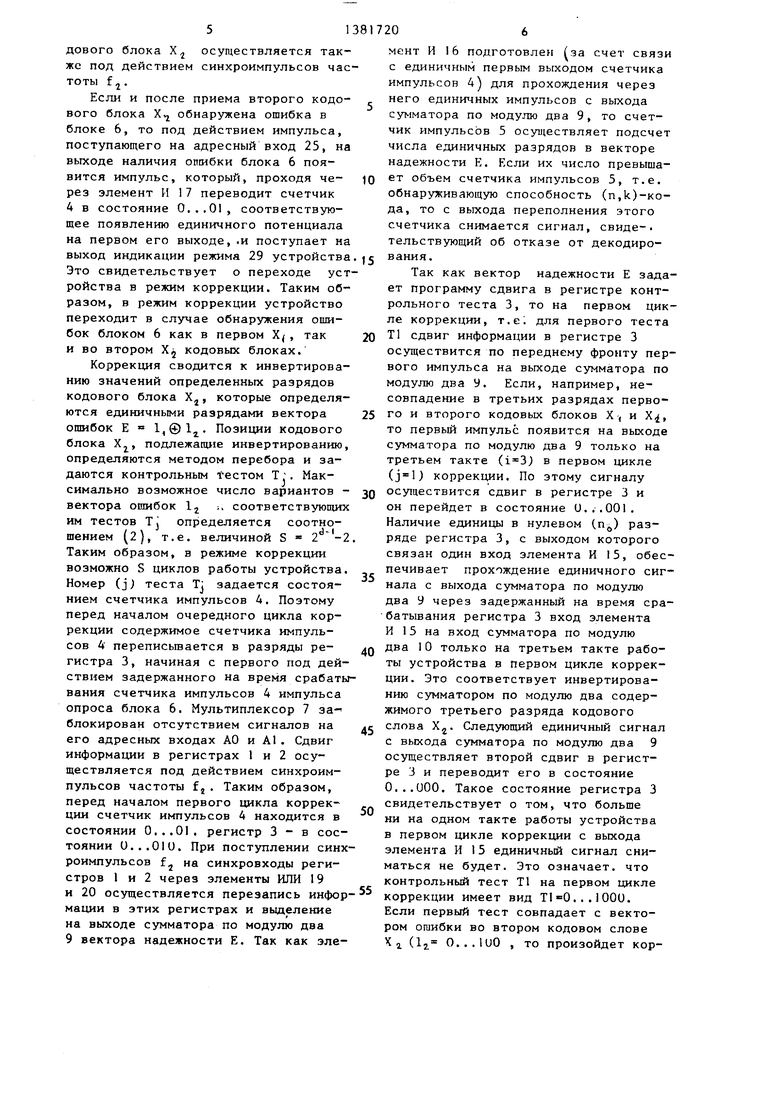

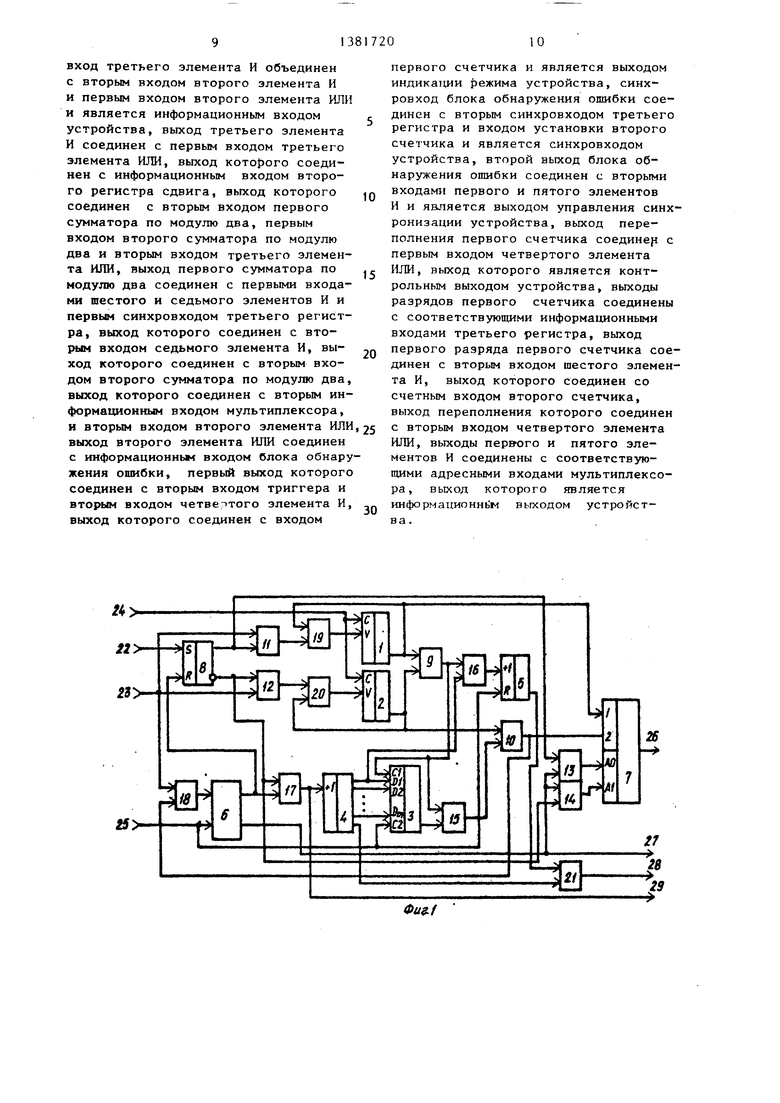

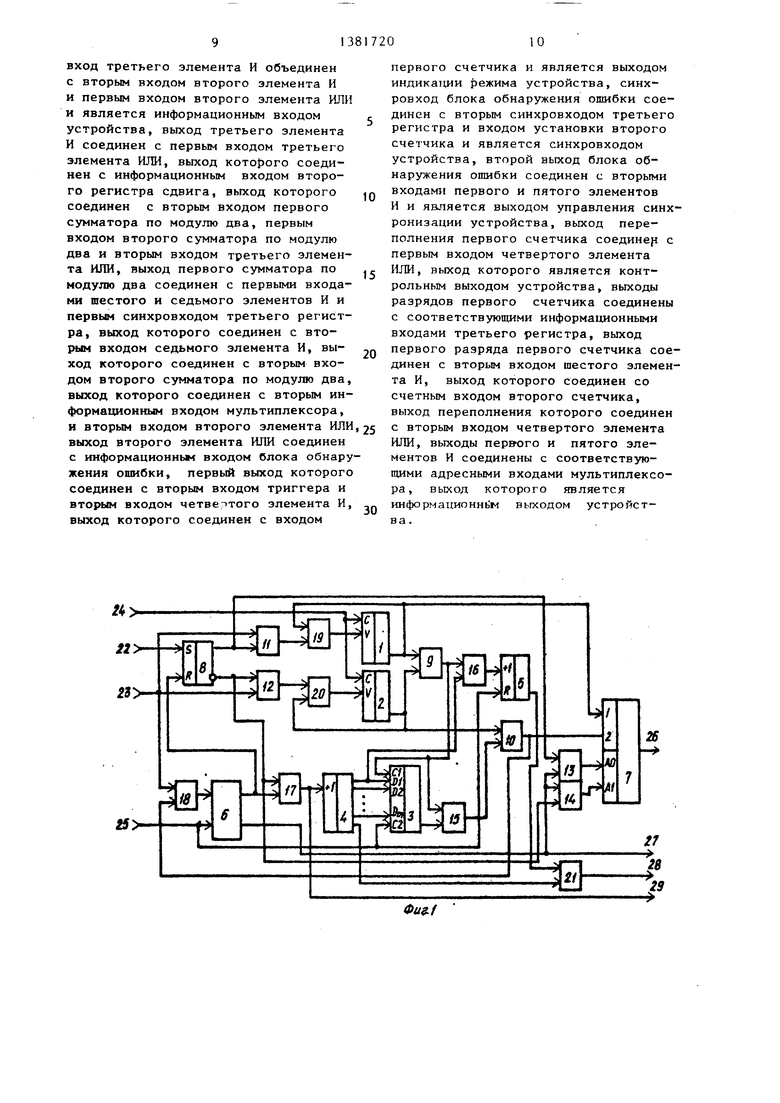

На фиг.1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы управляющих сигналов .

Устройство (фиг.1) содержит регистры сдвига I и 2, регистр коит- рольноро теста 3, счетчики 4 и 5, блок обнаружения ошибок 6, мультиплексор 7, триггер 8, с т маторы по модулю два 9 и 10, элементы И 11-17 элементы ИЛИ 18-21, входы 22-25, выходы 26-29.

Устройство работает следующим образом.

На установочный вход устройства 22 поступает импульс, который переводит триггер 8 в единичное состояние. Это свидетельствует о том, что устройство готово для приема первого кодового блока X, в первый регистр сдвига 1. По окончании циклового фазирования поиска маркера блока X , на информационный вход устройства 23 поступает первый кодовый блок X,, который поступает через открытые элементы И 11 и ИЛИ 19 на информационный вход первого регистра сдвига 1, на синхровход С которого поступают с синхровхода устройства 2Д п синхроимпульсов частотой f, . Одновременно кодовый блок X, через элемент ИЛИ I8 поступает на информационный вход блока обнаружения ошибок 6, где осуществляется проверка на достоверность блока X, (n,k)-кодом например для разделимого циклического кода деление на образующий полином). По окончании записи блока X , в регистр 1 с опросного входа уст ройства 25 поступает импульс опроса состояния блока 6. Если блок 6 ошибки не обнаруживает, то на втором его выходе (выходе отсутствия ошибки) появляется сигнал, который через элемент И 13 (на второй вход которого поступает единичный потенциал с единичного выхода триггера 8), поступая на первьй адресный вход мультиплексора 7, подготавливает мультиплексор 7 для выдачи информации на информационный выход 26 устройства по первому каналу, т.е. с выхода регистра 1. Этот же сигнал, поступая на выход управления синхронизирующего устройства, обеспечивает поступление на синхровход 24 устройства п синхроимпульсов частоты fjjnoA действием которых достоверно принятый блок Х( по первому каналу через мультиплексор 7 считывается на информационный выход 26 устройства, при использовании разделимого (n,k)-кoдa считьгоа0

5

0

5

0

5

0

5

0

5

::тся только первые k разрядов, т.е. на синхровход 24 устройства поступают k синхроимпульсов частоты f.

Если блок 6 ошибку обнаруживает, то на первом его выходе (выходе наличия ошибки) появляется импульс, который обнуляет блок 6 (не показано, но может быть реализовано как обычный сброс элементов памяти, например обычного декодера циклического кода) и переводит триггер 8 в нулевое состояние. Через элемент И 17 этот импульс не пройдет, так как элемент И 17 бьш заблокирован отсутствием единичного потенциала на другом его выходе, так как триггер 8 находился в единичном состоянии. Таким образом, устройство подготовлено для приема второго кодового блока Xj.

Второй кодовый блок Х по окончании его циклового фазирования, поступая на информационный вход 23 устройства на тактовой частоте f через открытый элемент И 12 и ИЛИ 20, записьюается в регистр 2, а че- .рез элемент ИЛИ 18 проверяется на достоверность блоком 6. Одновременно под действием синхроимпульсов f, осуществляется через элемент И.ГТИ 19 перезапись содержимого регистра I. При этом, появление первого блока X, на выходе сумматора по модулю два 9 не влияет на работу устройства, так как счетчик импульсов 4 и регистр 3 находятся в нулевом состоянии и поэтому заблоки-- рованы. По окончании записи второго кодового блока Х в регистр 2 на опросный вход 25 устройства поступает второй импульс опроса блока 6. Если ошибка не обнаружена, то через элемент И 14, так как второй его вход связан с нулевым выходом триггера 8, сигнал поступает на адресный вход А1 мультиплексора 7, подготавливая его для выдачи информации на информационном выходе 26 устройства по второму каналу, т.е. с выхода регистра 2 через сумматор по модулю два 10. Так как на второй пход этого сумматора по модулю два 10 информация не поступает (регистр 3 находится в нулевом состоянии), то кодовый блок Xj, проходя через сумматор по модулю два 10, не изменит своей структуры. Считывание (ретрансляция) достоверно принятого в регистр 2 кодового блока Х осуществляется также под действием синхроимпульсов частоты fj.

Если и после приема второго кодового блока Х обнаружена ошибка в блоке 6, то под действием импульса, поступающего на адресный вход 25, на выходе наличия ошибки блока 6 появится импульс, который, проходя через элемент И 17 переводит счетчик 4 в состояние О,.,01, соответствующее появлению единичного потенциала на первом его выходе, .и поступает на

13817206

мент И 16 подготовлен Гза счет связи с единичным первым выходом счетчика импульсов 4) для прохождения через него единичных импульсов с выхода сумматора по модулю два 9, то счетчик импульсов 5 осуществляет подсчет числа единичных разрядов в векторе надежности Е. Если их число превыша- 0 бт объем счетчика импульсов 5, т.е. обнаруживающую способность (n,k)-KO- да, то с выхода переполнения этого счетчика снимается сигнал, свиде- тельствующий об отказе от декодиро

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Пороговый декодер сверточного кода | 1985 |

|

SU1252944A1 |

Изобретение относится к вычислительной технике и технике связи и может быть использовано в устройствах защиты от ошибок систем передачи и обработки дискретной информации, а также в системах дальней связи с дублированием сообщений. Цель изобретения - повышение пропускной способности и достоверности устройства. Достижение цели изобретения обеспечивается введением в устройство второго и третьего регистров, мультиплексора, триггера, элементов И и элементов ИЛИ. Сущность изобретения состоит в том, что в устройстве осуществляется коррекция методом перебора значений разрядов одного из двух повторений избыточного кодового слова только на тех позициях, где произоншо несовпадение двух повторений. При этом коррекция с последующей проверкой на достоверность осуществляется на тактовой частоте срабатьшания логических элементов, значительно превьппающей тактовую частоту приема кодового слова. 2 ил. а в (Л

ыход индикации режима 29 устройства. 15 вания. то свидетельствует о переходе устойства в режим коррекции. Таким обазом, в режим коррекции устройство ереходит в случае обнаружения ошиок блоком 6 как в первом Х, так

20

Так ет прог рольног ле корр Т1 сдви осущест вого им модулю совпаде го и вт то перв суммато третьем () к осущест он пере Наличие ряде ре связан печивае нала с два У ч батыван И 15 на два 10 ты устр ции. Эт нию сум жимого дс слова X с выход осущест ре 3 и O...UOO свидете ни на о в перво элемен маться контрол

и во втором Xj кодовых блоках.

Коррекция сводится к инвертированию значений определенных разрядов кодового блока Х, которые определяются единичными разрядами вектора ошибок Е l,®lj. Позиции кодового блока Х, подлежащ 1е инвертированию, определяются методом перебора и задаются контрольным tecTOM Т . Максимально возможное число вариантов - вектора ошибок Ij - соответствующих им тестов TJ определяется соотношением (2), т.е. величиной S , Таким образом, в режиме коррекции возможно S циклов работы устройства. Номер (J) теста Tj задается состоянием счетчика импульсов 4. Поэтому перед началом очередного цикла коррекции содержимое счетчика импульсов 4 переписьшается в разряды регистра 3, начиная с первого под действием задержанного на время срабатывания счетчика импульсов 4 импульса опроса блока 6. Мультиплексор 7 за-- блокирован отсутствием сигналов на его адресных входах АО и А1. Сдвиг информации в регистрах 1 и 2 осуществляется под действием синхроимпульсов частоты fJ. Таким образом, перед началом первого цикла коррекции счетчик импульсов 4 находится в состоянии O...OI. регистр 3 - в состоянии U...OIU. При поступлении синхроимпульсов fj на синхровходы регистров 1 и 2 через элементы ИЛИ 19

25

30

Так как вектор надежности Е ет программу сдвига в регистре к рольного теста 3, то на первом ле коррекции, т.е . для первого т Т1 сдвиг информации в регистре 3 осуществится по переднему фронту вого импульса на выходе сумматор модулю два У. Если, например, н совпадение в третьих разрядах пе го и второго кодовых блоков Х-, и то первый импульс появится на вы сумматора по модулю два 9 только третьем такте () в первом цик () коррекции. По этому сигнал осуществится сдвиг в регистре 3 он перейдет в состояние 0...001. Наличие единицы в нулевом (п) р ряде регистра 3, с выходом котор связан один вход элемента И 15, печивает прохождение единичного нала с выхода сумматора по модул два У через задержанный на время батывания регистра 3 вход элемен И 15 на вход сумматора по модулю два 10 только на третьем такте р ты устройства в Первом цикле кор ции. Это соответствует инвертиро нию сумматором по модулю два сод жимого третьего разряда кодового дс слова Xj. Следующий единичный си с выхода сумматора по модулю два осуществляет второй сдвиг в реги ре 3 и переводит его в состояние O...UOO. Такое состояние регистр свидетельствует о том, что больш ни на одном такте работы устройс в первом цикле коррекции с выход элемента И 15 единичный сигнал с маться не будет. Это означает, ч контрольный тест Т1 на первом ци

35

40

50

и 20 осуществляется перезапись инфор- коррекции имеет вид ...1000.

мации в этих регистрах и выделение на выходе сумматора по модулю два 9 вектора надежности Е. Так как элевания.

Так как вектор надежности Е задает программу сдвига в регистре контрольного теста 3, то на первом цикле коррекции, т.е . для первого теста Т1 сдвиг информации в регистре 3 осуществится по переднему фронту первого импульса на выходе сумматора по модулю два У. Если, например, несовпадение в третьих разрядах первого и второго кодовых блоков Х-, и Х, то первый импульс появится на выходе сумматора по модулю два 9 только на третьем такте () в первом цикле () коррекции. По этому сигналу осуществится сдвиг в регистре 3 и он перейдет в состояние 0...001. Наличие единицы в нулевом (п) разряде регистра 3, с выходом которого связан один вход элемента И 15, обеспечивает прохождение единичного сигнала с выхода сумматора по модулю два У через задержанный на время сра- батывания регистра 3 вход элемента И 15 на вход сумматора по модулю два 10 только на третьем такте работы устройства в Первом цикле коррекции. Это соответствует инвертированию сумматором по модулю два содержимого третьего разряда кодового слова Xj. Следующий единичный сигнал с выхода сумматора по модулю два 9 осуществляет второй сдвиг в регистре 3 и переводит его в состояние O...UOO. Такое состояние регистра 3 свидетельствует о том, что больше ни на одном такте работы устройства в первом цикле коррекции с выхода элемента И 15 единичный сигнал сниматься не будет. Это означает, что контрольный тест Т1 на первом цикле

коррекции имеет вид ...1000.

Если первый тест совпадает с вектором ошибки во втором кодовом слове X 5 (17 0...1UO , то произойдет коррекция (исправление) этой ошибки Результат суммирования по модулю два кодового слова Х, с первым тестом Т, с выхода сумматора по модулю два 10 через элемент ИЛИ 18 поступает на вход блока 6, где проверяется на достоверность. Если ошибка не обнаружена, то состояние счетчика импульсов 4 не меняется, в регистр контрольного теста 3 задержанным импульсом опроса блока 6 записывается снова номер первого теста, и мультиплексор через элемент И 14 подготавливается для выдачи информации на информационный выход 2k устройства по второму каналу. В процессе вьщачи информации на информационный выход 26 устройства через второй канал мультиплексора 7 в устройстве происходят процессы, аналогичные тем, что и в первом цикле коррекции, т.е. осуществляется инвертирование позиции кодового слова Х2 в соответствии с единичным разрядом первого контрольного теста t , , т.е. с информационного выхода 26 устройства по окончании первого цикла коррекции в случае необнаружения ошибок блоком 6 будет считываться кодовое слово Х2® Т, S , так как в этом случае Т, 1. Если в кодовом слове (.,) блок 6 обнаружит, то устройство перейдет на второй цикл коррекции. По импульсу опроса блока 6 произойдет обнуление счетчика импульсов 5 и через элемент И 17 изменится состояние счетчика импульсов 4 (О...10), которое перепишется в регистр 3 и переведет его в состояние U...10U.

В дальнейшем работа устройства аналогична работе на первом цикле. Отличие состоит лишь в том, что при первом сдвиге (т.е. на первой единичной позиции вектора надежности Е) в регистре 3 его разряд п не примет единичного значения, так как состояние регистра 3 будет 0.,.010, Нулевой разряд п регистра 3 на втором цикле коррекции () примет единичное значение только на такте, соответствующем номеру второго единичного разряда,вектора надежности Е. Это означает, что коррекция огаибки в кодовом слове Х произойдет только на позиции, соответствующей номеру второго единичного разряда вектора надежности Е. В остальном работа устройства аналогична работе

0

5

0

5

0

4

0

5

0

5

на первом цикле коррекции. В случае необнаружения ошибки блока 6 на ин- фсэрмационном выходе 26 устройства будет считьшаться кодовое слов Х,© (±) Tj, так как в этом случае Т 1,. Если блок 6 в этом кодовом слове ошибку обнаружит, устройство перейдет на третий цикл коррекции.

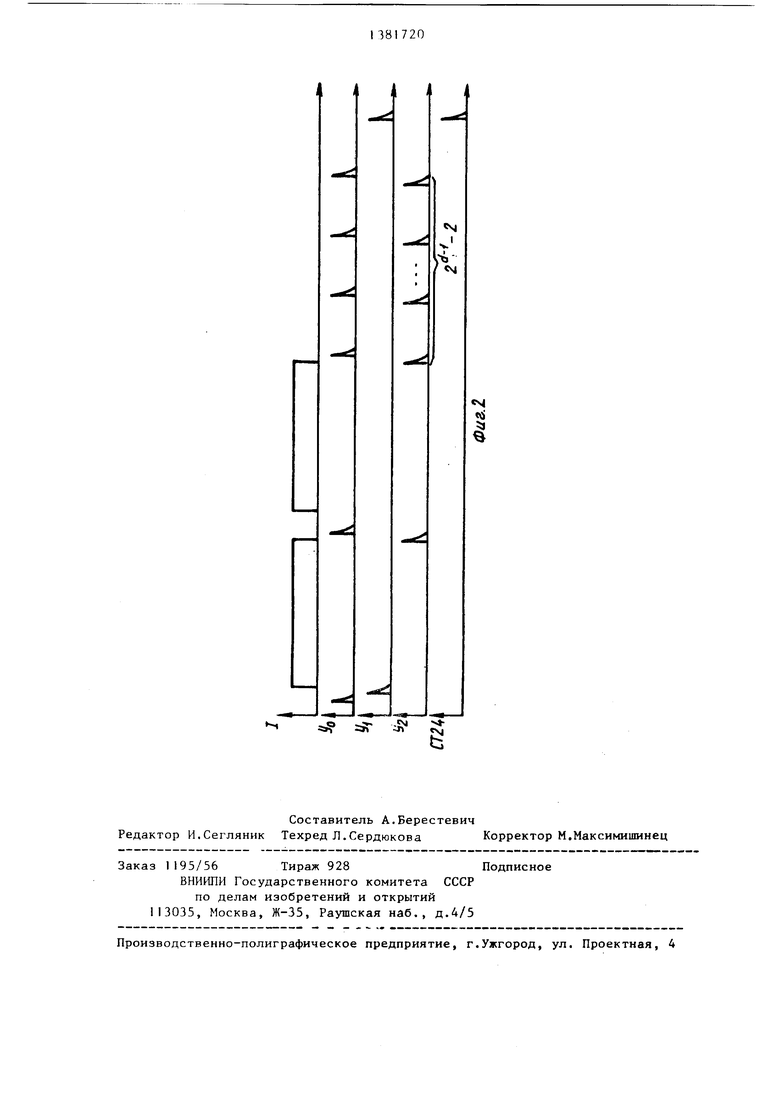

Режим коррекции будет продолжаться до тех пор, пока не будет найден вектор ошибки 1 Т-,либо не появится сигнал переполнения на выходе переполнения счетчика импульсов 4, свидетельствующий о наличии неисправимых ошибок в кодовом слове Х, т.е. ошибок в одноименных разрядах кодовых слов X, и Xj. На фиг.2 приведены временные диаграммы, поясняющие моменты поступления основных управляющих сигналов. Здесь приняты следующие обозначения: I - информационный вход 23; YO - моменты обнуления блока 6 (на фиг.1 не показано); Y, - установочный вход 22; Y - опросный вход 25 (сигналы опроса блока 6 и сброса 5); 4 - импульс переполнения счетчика 4.

Формула изобретения

Декодирующее устройство, содержащее блок обнаружения ошибки, сумматоры по модулю два, счетчики и первый регистр сдвига, выход которого соединен с первым входом первого сумматора по модулю два, о т л и ч а ю- щ е е с я тем, что, с целью повышения достоверности и информативности устройства, в него введены второй и третий регистры сдвига, мультиплексор, элементы И, элементы ИЛИ и триггер, S-вход которого является установочным входом устройства, прямой выход соединен с первыми входами первого и второго элементов И, выход втопого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с информационным входом первого регистра сдвига, выход которого соединен с первым информационным входом мультиплексора и вторым входом первого элемента ИЛИ, синхровходы первого и второго регистров сдвига объединены и являются первым синхровходом устройства, инверсный выход триггера соединен с первыми входами третьего, четвертого и пятого элементов И, второй

вход третьего элемента И объединен с вторым входом второго элемента И и первым входом второго элемента ИЛИ и является информационным входом устройства, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выход кото{)ого соединен с информационным входом второго регистра сдвига, выход которого соединен с вторым входом первого сумматора по модулю два, первым входом второго сумматора по модулю два и вторым входом третьего элемента ИЛИ, выход первого сумматора по модулю два соединен с первыми входами шестого и седьмого элементов И и первым синхровходом третьего регистра, выход которого соединен с вторым входом седьмого элемента И, выход которого соединен с вторым входом второго сумматора по модулю два, выход которого соединен с вторым информационным входом мультиплексора, и вторым входом второго элемента ИЛИ выход второго элемента ИЛИ соединен с информационньм входом блока обнаружения ошибки, первый выход которого соединен с вторым входом триггера и вторым входом четвертого элемента И, выход которого соединен с входом

первого счетчика и является выходом индика1щи режима устройства, синх- ровход блока обнаружения ошибки соединен с вторым синхровходом третьего регистра и входом установки второго счетчика и является синхровходом устройства, второй выход блока обнаружения ошибки соединен с вторыми входами первого и пятого элементов И и является выходом управления синхронизации устройства, выход переполнения первого счетчика соединер с первым входом четвертого элемента ИЛИ, выход которого является контрольным выходом устройства, выходы разрядов первого счетчика соединены с соответствующими информационными входами третьего регистра, выход первого разряда первого счетчика соединен с вторым входом шестого элемента И, выход которого соединен со счетным входом второго счетчика, выход переполнения которого соединен с вторым входом четвертого элемента ИЛИ, выходы первого и пятого элементов И соединены с соответствующими адресными входами мультиплексора, выход которого является информационнь м выходом устройства.

26

Фиг.

dr Ji- ;;

«SI

«V4

| Станок для изготовления плетней | 1976 |

|

SU582964A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-15—Публикация

1986-09-26—Подача