Изобретение относится к автоматике и вычислительной технике и может быть использовано для повышения надежности резервированных вычислитель ных комплексов. Известно устройство для организации структуры вычислительного комплекса, содержащее коммутаторы, соединенные с выходами предыдущих и вхо дами последующих резервных блоков системы, соединенные с управляющими входами соответствующих коммутаторов элементы 1 Его недостатки - сложность и нед статочная надежность. Вследствие ос бенности алгоритма его работы не пр изводится полного перебора всех вар антов включения резервных блоков в каналы, так как найденные исправные каналы их процесса переключения иск лючаются. Это приводит к снижению надежности системы в целом и исключает возможность полной диагностической проверки системы. Наиболее, близким к изобретению техническим решением является устройство для организации структуры, вычислительного комплекса; содержащее коммутатор, подключенный одними выходами к выходам устройства, элементы И и ИЛИ, счетчик, соединенный первым и вторым входами соответственно с первым входом устройства и выходом первого элемента ИЛИ,а выходамис дешифратором, подключенным первым выходом через селектор к одному входу первого элемента ИЛИ. Данное устройство при неисправности- одного резервного блока обеспечивает замену поступающей с него информации . на информацию исправного соседнего блока, а с самого неисправного блока снимается питание, кроме того, резервные блоки, не используемые при построении выбранной структуры, также отключаются от тин питания, что обеспечивает режим холодного резервирования 2 . Недостатками данного устройства является сложность схемы и недостаточная надежность, так как в схеме предусмотрено попарное включение резервных элементов, приводящее к тому, что устройство не обеспечивает работоспособную организацию двухканального комплекса при возникновении в нем отказов. Кроме того, оно имеет ограниченное число возможных вариантов организации структуры резервированной системы.

так как увеличение числа вариантов организации структуры приводит к значительному увеличению аппаратных затрат. Это ограничивает област применения и снижает надежность устройства.

Цель изобретения - расширение области применения и повышение надежности устройства..

Эта цель достигается тем, что в устройство для организации структуры вычислительного комплекса, содержащее первый коммутатор, подключенный одними выходами к выходам устройства, элементы И и ИЛИ, счетчик , соединенный первым и вторым входами соответственно с первым входом устройства и выходом первого элемента ИЛИ, а выходами - с дешифратором, подключенным первым выходо через селектор к одному входу первого элемента ИЛИ, введены регистр , компаратор, подключенный первыми вхдами к.выходам регистра, и вторые коммутатор и счетчик, соединенный выходами со вторыми входами компаратора и через второй коммутатор с певыми входами первого коммутатора, второйвход которого подключен к одному выходу койпаратора, а другие входы второго коммутатора соединены со вторым входом устройства, другими выходами первого коммутатора и вторым выходом дешифратора, подключенным ко второму входу первого элемента ИЛИ, причем, третий виход дешифратора через элемент И, соединенный другим входом с третьим входом устройства, подключен к одному вхоiiy второго элемейта ИЛИ, другой вход и выход которого соединены соответственно с другим выходом селектора, подключенного другим входом с четвертым входом устройства,и третьему входу компаратора, другой выход которого подключен к третьему входу первого счетчика и первому входу второго счетчика соединенного вторым входом с первым входом устройства и третьими входами с другими выходами второго коммутатора.

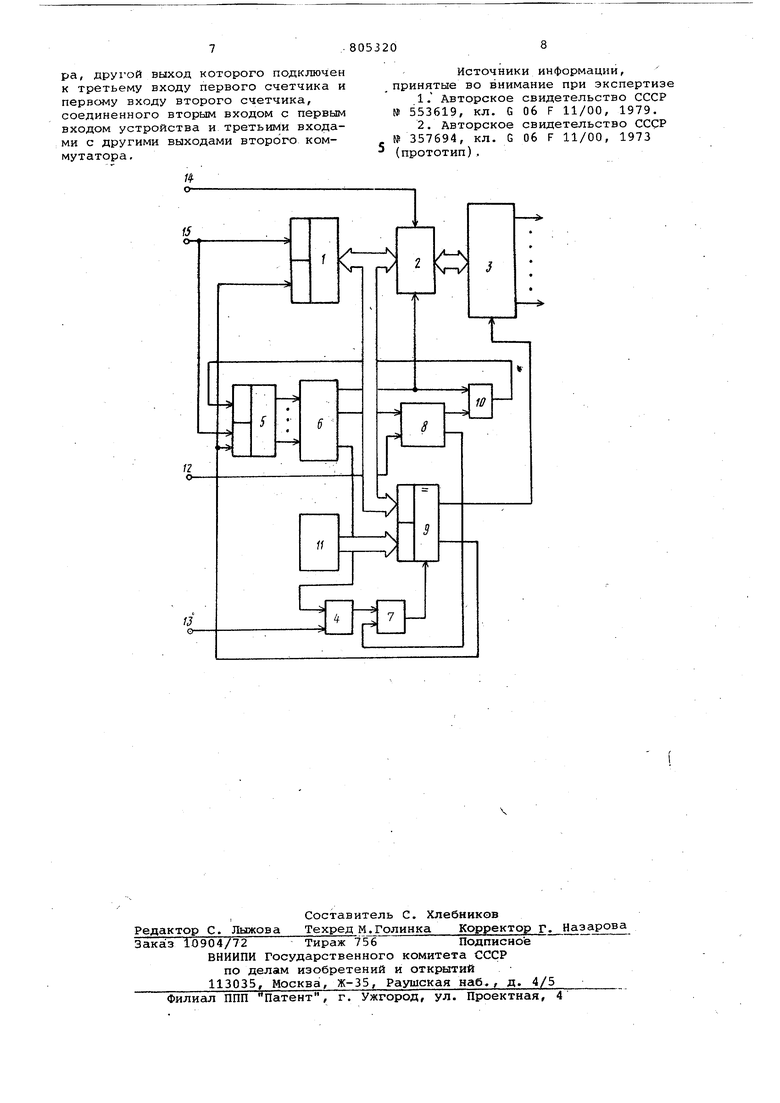

На чертеже показана функциональная схема устройства. Устройство содержит счетчик 1 (счетчик структур) , коммутаторы 2 и 3 (соответственно - блок управления связями и блок переключения питания устройств вычислительного комплекса) , элемент И 4, счетчик 5 (счетчик шагов), дешифратор б, элемент ИЛИ 7, селектор 8 (блок анализа сигнала Готовность ЦВМ), компаратор 9, элемент ИЛИ 10, регистр 11 (регистр кода максимальной структуры) и входные шины 12 (цепь сигнала Готовность ЦВМ), 13 (цепь сигнала Регламент 14 (цепь разрешения записи) и 15

/ цепь сигнала Сброс).

Устройство работает следующим образом.

После начального сброса схемы сигналом по цепи 15 Сброс на блок 2 управления связями по цепи 14 разрешения записи поступает сигнал, который обеспечивает занесение в счет,чик 1 структур кода, соответствующего первой исправной структуре, работоспособность которой выявлена на предыдущей регламентной проверке и которая зафиксирована в блоке переключателей питания устройств вычислительного комплекса 3. При этом обнуляется счетчик 5 шагов, что вбесс печивает, перевод в возбужденное состояние первого выхода дешифратора 6 и приводит к выдаче сигнала пуска комплекса в блок 2 управления связями. В соответствии с кодом на счетчике 1 структур достигается подключение питания k устройствам комплекса, используемым при организации данной структуры. Устройство осуществляет выбор работоспособной структуры двухканального вычислительного комплекса, представляющего из себя двойной набор приборов (ОЗУ, ПЗУ и т.д.), связанный между собой двумя магистралями. Перебор и включение структур вычислительного комплекса осуществляется путем изменения содержаний счетчика 1 структур и выдачи с него управляющих сигналов через блок 2 управления связями на блок 3 переключателей питания .соответствующих устройств вычислительного комплекса. Каждый разряд сЧетчика 1 структур обуславливает выбор определенного прибора вычислительного комплекса, при этом нулевое состояние данного разряда соответствует включению в ЦБК прибора первого комплекта, а единичное значение приводит К вводу в структуру комплекса резервного прибора из второго комплекта. Тем самым изменением содержания счетчика структур обеспечивается перестройка конфигурации вычислительного комплекса. Поиск работоспособной структуры начинается при нулевом значении счетчика 1 структур (в регламентном режиме, а в штатном режиме, как уже описывсшось выше, с первой исправной структуры) и перебор структур осуществляется путем последовательного увеличения его содержимого на единицу. После включения структуры комплекс начинает выполнять программу самопроверки. Сигнал о пуске комплекса через элемент ИЛИ 10 поступает на счетчик 5 шагов; тем самым к его содержимому прибавляется единица, что 5влечет,за собой включение через дешифратор б блока 8 анализа сигнала Готовность ЦВМ, и переводит в возбужденное состояние другой вы$сод дешифратора б, каждый раз

при включении очередного блока в соответствии с принятым алгоритмом работы устройства, т,е; счетчик 5 шагов, дешифратор б и элемент ИЛИ 10 выполняют роль схемы управления пред, ложенного устройства. Блок 8 анализа сигнала Готовность ЦВМ осуществля- 5 ет анализ результатов самопроверки комплекса. При нормальной работе комплекса вырабатывается сигн&л Готовность ЦВМ, поступающий в устройство по цепи 12 сигнала Готов- Ю ностьЦВМ, временную селекцию момента прихода которого и выполняет блок

0анализа сигнала Готовность ЦВМ, При отрицательном результате анализа со второго выхода.блока 8 выдает- 5

01сигнал на элемент ИЛИ 7, по которому последний выдает сигнал разрешения сравнения на компаратор 9. Компаратор 9 выполняет сравнение кодов, поступающих с регистра 11 кода мак- 20 симальной последней) структуры и текущей структуры со счетчика-1 струит ктур. Компаратор 9 при несравнении кодов по сигналу разрешения сравнения срабатывает счетчик 5 шагов и 25 прибавляет к содержимому счетчика 1 структур, чем обеспечивается включение следующей структуры вычислительного комплекса и выполнения комплекса программы самопроверки. При JQ сравнении кодов компаратор 9 выдает . сигнсш о снятии питания с устройств комплекса в блок 3 переключателей питания устройств комплекса, означающий что в данном вычислительном ком- , плексе не сталось ни одной работоспособной структуры (в регламентном режиме снятие питания говорит об окончании регламентной проверки), При нормальной работе включенной структуры блок 8 анализа Готовность .ЦВМ через элемент ИЛИ 10 увейичивает содержание счетчика 5 шагов на единицу, что переводит в возбужденное состоян-ие третий выход дешифратора 6 и при наличиц в цепи 13 сиг- 45 нала Регламент через элементы И 4. и ИЛИ 7 выдачу сигнала разрешения / сравнения на компаратор 9. Это и обеспечивает реализацию режима регла ментной проверки вычислительного 50 комплекса,так как производится посг ледовательное включение вычислительного комплекса при всех возможных : способах организации его структуры и независимо от результатов анали- ее за работоспособности каждой отдельной структуры. При отсутствии сигнала Регламент в цепи 13 блок 8 анализа Готовность ЦВМ продолжает вести контроль работоспособности выбранной структуры путем временной 0 селекции сигнала Готовность ЦВМ в каждом машинном цикле. Снятие готовности при этом проводит перестроит ку вычислительного комплекса в целях

поиска работоспособной структуры по описанной выше методике.

Таким образом, техническая эффективность, полученная в результате реализации предложенного устройства, заключается в том, что осуществляется выбор работоспособной структуры в Ёычислительном комплексе, содержащем двойной набор устройств, связь которыми осуществляется по двум магистралям и позволяет организовать два способа организации данного вычислительного комплекса.

Кроме этого, предложенное устрой-- ство осуществляет контроль сформированных структур ЦВМ. Этим достигается повышение надежности комплекса в целом путем увеличения числа возможных способов организации вычислительного комплекса без значительного увеличения оборудования и обеспечивается оперативная перестройка комплекса на работоспособную структуру при возникновении в нем отказов, тем самым расширяется область применения и повышается надежность устройства.

Формула изобретения

Устройство для организации структуры вычислительного комплекса, содержащее первый коммутатор, подключенный одними выходами к выходам устройства, элементы И и ИЛИ, счетчик, соединенный первым и вторым входами соответственно с первым входом устройства и выходом первого элемента ИЛИ,а выходами - с дешифратором, подключенным первым выходом через селектор к одному входу первого элемента ИЛИ, отличающееся тем, что, с целью расширения области применения и повышения надежности устройства, оно содержит регистр, компаратор, подключенный первыми входами к выходам регистра, и вторые коммутатор и счетчик , соединенный выходами со вторы ми входами компаратора и через второй коммутатор с первыми входами первого коммутатора, второй вход которого подключен к одному выходу компаратора, а другие входы второго коммутатора соединены cof вторым входом устройства, другими выходами первогО коммутатора и вторым выходом дешифратора, подключенным ко второму входу первого элемента ИЛИ,, приче третий выход дешифратора через элемент И, соедине1 ный другим входом с третьим входом устройства, подключен к одному входу второго элемента ИЛИ, другой вход и выход которого соединены соответственно с другим выходом селектора, подключенного другим входом с четвертым входом устройства, и третьему входу компарат

pa, дру1ой выход которого подключен к третьему входу первого счетчика и первому входу второго счетчика, соединенного вторым входом с первым входом устройства и третьими входами с другими выходами второго коммутатора.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР № 553619, кл. G 06 F 11/00, 1979,

2. Авторское свидетельство СССР №357694, кл, G Об F 11/00, 1973 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора работоспособной структуры вычислительного комплекса | 1980 |

|

SU1037256A1 |

| Устройство для контроля и управления структурой вычислительного комплекса | 1985 |

|

SU1247878A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Адаптер канал-канал | 1982 |

|

SU1067492A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для ввода информации | 1982 |

|

SU1130854A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

Авторы

Даты

1981-02-15—Публикация

1978-12-01—Подача