четвертые входы входного дешифратора соединены с шестыми выходами выходного дешифратора, с выходами триггеров-ОКОНЧАНИЕ и ОЖИДАНИЕ и подключены к входам-выходам узла, выходы входного дешифратора подключены к соответствующим динамическим входам триггеров состояний, вход синхронизации каждого из которвлх соединен с выходом генератора синхросигналов, а выхода - с соответствующими входами дешифратора состояний, выходы которого подключены к пятым входам входного дешифратора и ко вторым входам выходного дешифратора, соединенного первыми входами с первыми, третьими и четвертыми входами входного дешифратора, а третьими входами - с шестыми входами входного дешифратора и с выходами триггеров ОЖИДАНИЕ и ОКОНЧАНИЕ, подключенных входами установки соответственно к седьгллм и восьмым выходам выходного д аиифратора, причем вход сброса триггера ОКОНЧАНИЕ подключен к девятому выходу выходного дешифратора, а вход сброса триггера ОЖИДАНИЕ - ко входу-выходу узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптер канал-канал | 1981 |

|

SU1037235A1 |

| Адаптер канал-канал | 1979 |

|

SU851391A1 |

| Адаптер канал-канал | 1983 |

|

SU1112361A2 |

| Адаптер канал-канал | 1983 |

|

SU1144114A1 |

| Адаптер канал-канал | 1988 |

|

SU1509861A2 |

| Адаптер канал - канал | 1988 |

|

SU1608677A2 |

| Адаптер канал-канал | 1982 |

|

SU1049895A2 |

| Адаптер канал-канал | 1978 |

|

SU734661A1 |

| Адаптер канал-канал | 1985 |

|

SU1305697A2 |

| Адаптер канал-канал | 1985 |

|

SU1259276A1 |

1. АДАПТЕР КАНАЛ-КАНАЛ, СОСТОЯЩИЙ из двух полуадаптеров, в каждсм из которых выходы регистра команд через дешифратор команд соединены с первыми входами узла управления, второй вход которого подключен к выходу узла сравнения адресов, первые выходы узла управления непосредственно, а вторые выходы через регистр байта состояния соединены соответственно с первыми и вторыми входами группы элементов ИЛИ, третьи входы которой подключены к выходам буферного регистра другого полуадаптера, первые входы буферного регистра соединены с третьими выходами узла управления, а выходы - с третьими входами группы элементов ИЛИ другого полуадаптера, входы-выходы узла управления coejmнены с входами-выходами узла управ.ления другого полуадаптера, четвертый выход узла управления подключен ко второму входу регистра команд, отличающийся тем, что, с целью повышения контролепригодности за счет обеспечения контроля адаптера канал-канал с помощью одной ЦВМ и/или переключения на резервную ЦВМ, в каждый из полуадаптеров дополни ельно введены входной и выходной коммутаторы интерфейса, второй регистр адреса, коммутатор 1 1(:.А ЧЙ адресов, причем первые и вторые входы входного коммутатора интерфейса подключены соответственно к первым и вторьм входам полуадаптера, первые выходы - к третьим входам узла управления, а вторые выходы ко вторым входам регистра команд, узла сравнения адресов и буферного регистра, первые и вторые входы выходного коммутатора интерфейса соединены соответственно с пятьми выходами узла управления и с выходами группы элементов ИЛИ, а первые и вторые выходы - соответственно с первыми и ВТ01КЛ4И выходами полуадаптера, первые и вторые входы коммутатора адреса подключены соответственно к выходам первого и второ(Л го регистров адресов, а выходы к первы входам узла сравнения ащресов и четвертым входам группы элементов ИЛИ, управляющие входы вход- ного и выходного коммутаторов интерфейса совместно с управляющими входом коммутатора адреса соединены с вторьм выходом регистра команд второго полуадаптера, а второй выход регистра команд подключен к управляицим входам входного и выходного коммутаторов интерфейса и коммутатора адреса другого полуадаптера . 2. Адаптер поп.1, отличающийся тем, что узел управления содержит входной дешифратор, триггеры состояний, дешифс атор состояний, выходной дешифратор, генератор синхросигналов, триггер ОКОНЧАНИЕ и триггер ОЖИДАНИЕ, причем первые, вторые и третьи входы входного дешифратора и первые, вторые, третьи, четвертые, пятые выходы выходного дешифратора являются соответственно первьми, вторыми, третьими входами и первыми, вторыми, третьими, четвертыми и пятьми выходами узла, а

Изобретение относится к вычислительной технике и может использоваться для связи цифровых вычислительных машин (ЦВМ) в многомашинном вычислительном комплексе. Известны устройства, содержание регистры, формирователи, триггеры, элементы ИЛИ, блоки коммутации, предназначенные для сопряжения ЦВМ многомашинных комплексов Cl и 21. Недостатком этих устройств является-то, что обмен информацией между ЦВМ производится под непосред ственньом управлением процессоров сопрягаемых ЦВМ, что значительно снижает производительность вьачислительного комплекса. Наиболее близким к предлагаемому является адаптер канал-канал, содержащий буферный регистр, входам и выходом, подключенный к двум иден тичным блокам связи с каналом, каждый из которых обслуживает канал, подключенный к нему через интерфейс ввода-вывода, и содержит узел входных сигналов, регистр команд, дешифратор команд, регистр адреса, узел сравнения адресов, узел управления, узел выходных сигнало в и регистр байта состояния СЗ. Тестовые и диагностические программы проверки известного адаптера приходится размещать в двух ЦВ)1, которые он сопрягает. Эти программы сильно связаны, что приводит к чрез мерному их усложнению. Существует возможность при тестировании подклю чать адаптер к двум каналам одной ЦВМ и производить диагностику с помощью программы этой ЦВМ. Но в этом случае проверка адаптера связана с механической перекоммутацией разъем и, как следствие, увеличением времени ремонта. При обнаружении f eисправности в одной из ЦВМ переключение на резервную ЦВМ также связано с механической перексяимутацией разъемов. Таким образом, недостатком известных устройств являются большие потери времени при поиске неисправностей и переключении на резервную ЦВМ. Цель изобретения - расширение функциональных возможностей путем обеспечения контроля адаптера канал-канал с помощью диагностических программ; только одной из ЦВМ, входящих в вычислительный комплекс и/или обеспечения переключения на 1:)езервную ЦВМ без механической перекоммутации разъемов. Поставленная цель достигается тем, что в адаптер канал-канал, состоящий из двух полуадаптеров, в каждом и;з которых выходы регистра команд через дешифратор команд соединены с первыми входами узла управления, второй вход которого подключен к выходу узла сравнения адресов, первые выходы узла управления непосредственно, а вторые выходы через регистр байта состояния соединены соответственно с перВ111МИ и вторыми входами группы элементов ИЛИ, третьи входы которой подключены к выходам буферного регистра другого полуадаптера, первые входы буферного регистра соединены с третьими выходами узла управления, а выходы - с третьими входами группы элементов ИЛИ другого полуадаптера, входы-выходы узла управления соединены с входами-выходами узла управления другого полуадаптера, четвертый выход узла управления подключен ко второму входу регистра команд, в каяодый из полуадаптеров дополнительно введены входной и выходной кo 1yтaтopы интерфейса, второй регистр адреса, коммутатор адресов, причем первые и вторые входы входного коммутатора интерфейса подключены соответственно к первым и вторым входам полуадаптера, первые выходы - к треим входам узла управления, а вторые ВЕлходы - ко вторым входам регистра команд, узла сравнения адресов и буферного регистра, первые и вторые входы выходного коммутатора интерфейса соединены соответственно С пятыми выходами узла управления и с выходами группы элементов ИЛИ, а первые и вторые выходы - соответственно с первыми и вторьми выходами полуадаптера, первые и вторые входы коюлутатора адреса подключены соответственно к выходам первого и второго регистров адресов, а выходы - к первым входам узла сравнения адресов и четвертым входам группы элементов ИЛИ, управляющие входы входного и выходного коммутаторов интерфейса совместно с управлякяцими входом коммутатора адреса соединены с вторым выходом регистра команд второго полуадаптера, а второй выход регистра команд подключен к управляющим входам вход ного и выходного коммутаторов интерфейса и коммутатора адреса другого полуадаптера.

Кроме того, узел управления полуадаптера содержит входной дешифратор, триггеры состояний, дншифратор состояний, выходной дешифратор, генратор синхросигналов, триггер ОКОНЧАНИЕ и триггер ОЖИДАНИЕ, причем первые, вторые и третьи входы входного дешифратора и первые, вторые, третьи, четвертые, пятые выходы выхного дешифратора являются соответственно первыми, вторыми, третьими входами и первыми, вторыми, третьим четве)ртыми, пятыми выходами узла, а четвертые входы входного дешифратора соединены с шестыми выходами выходного дешифратора, с выходами триггеров ОКОНЧАНИЕ и ОЖИДАНИЕ и поключены к входагм-выходам узла, выходы входного дешифратора подключены к соответствующим динамическим входам триггеров состояний, вход синхронизации каждого из которых соединен с выходом генератора синхросигналов, а выходы - с соответствующими входами дешифратора состояний, выходы которого подключены к пятым входам входного дешифратора и ко вторым входам выходного дешифратора, соединенного первыми входами с первыми, третьими и четвертыми входами входного дешифратора, а третьими входами - с шестьми входами входного дешифратора и с выходами триггеров ОЖИДАНИЕ и ОКОНЧАНИЕ, подключенньЕС входами установки соответственно к седьмым и восьмым выходам дешифратора, причем вход сброса триггера ОКОНЧАНИЕ подключен к девятому выходу выходного дешифратора, а вход сброса триггера ОЖИДАНИЕ - ко входувыходу узла.

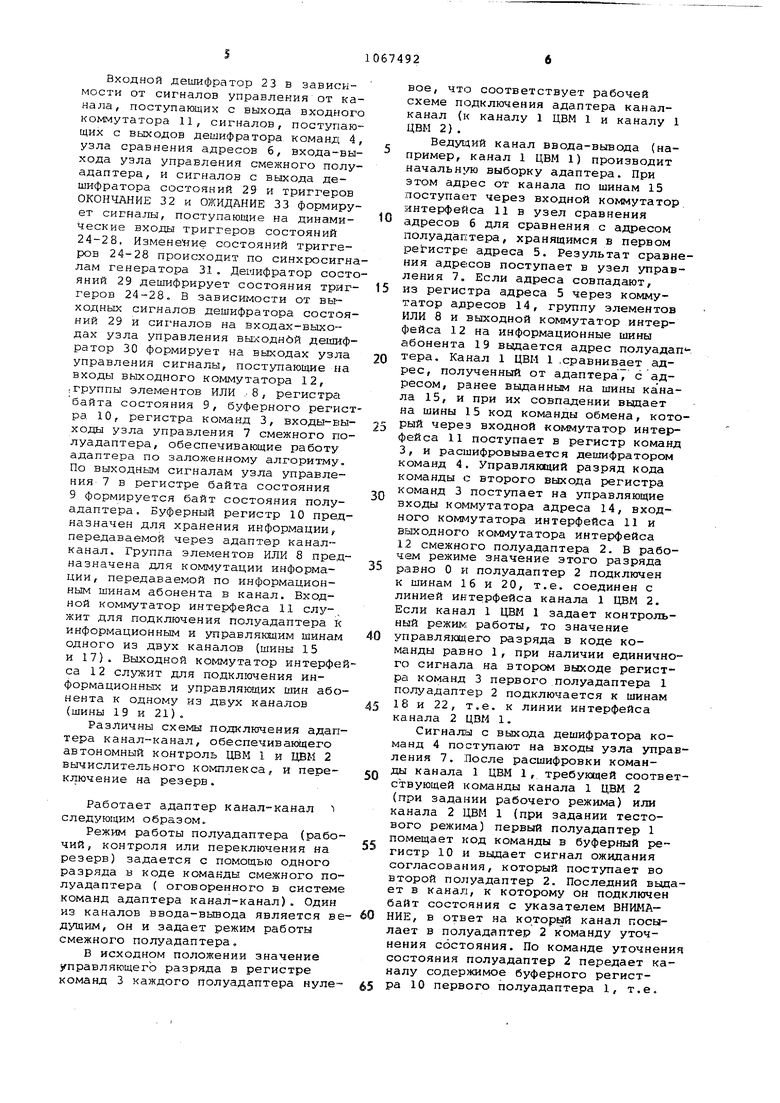

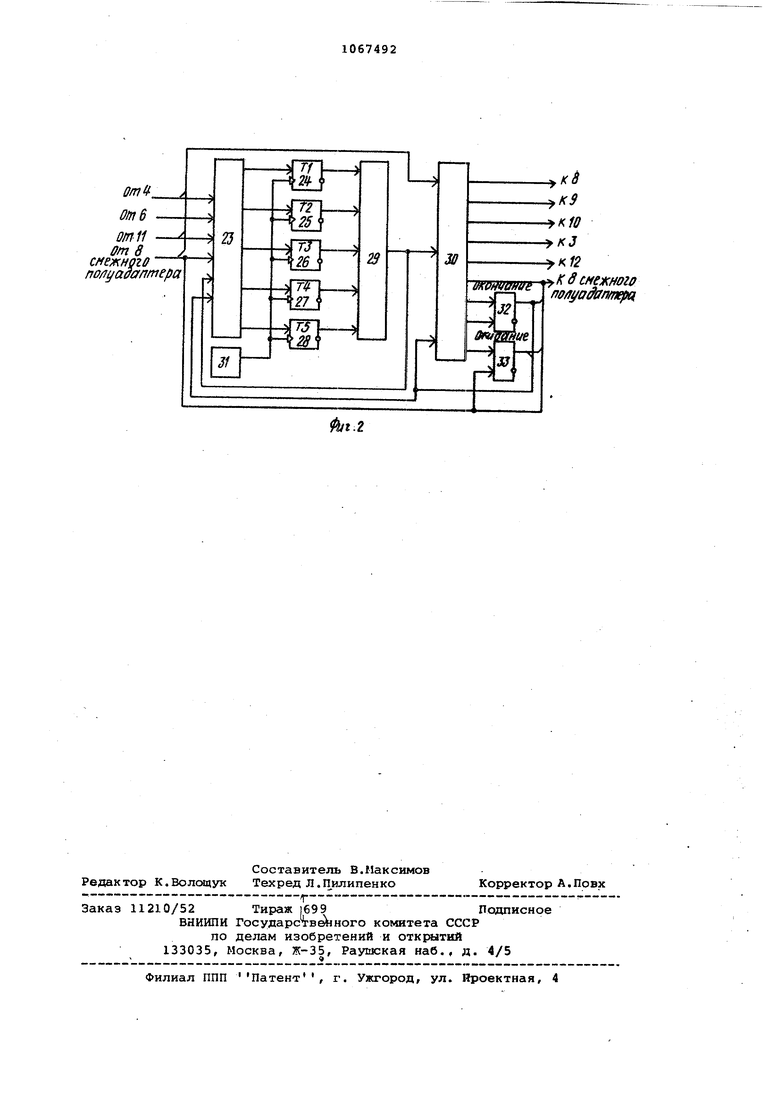

На фиг.1 приведена функциональная схема адаптера канал-канал; на фиг.2 - функциональная схема узла упр авления адаптера канал-канал.

Адаптер канал-канал состоит из

|двух полуадаптеров 1 и 2, каждый из которых содержит регистр команд 3, дешифратор команд 4, первый регистр адреса 5, узел сравнения адресов б, узел управления 7, группу элементов ИЛИ 8, регистр байта состояния 9, буферный регистр Ю, входной 11 и выходной 12 KONwyTaTOры интерфейса, второй регистр адреса 13, коммутатор адресов 14, первые и вторые входы полуадаптера (для полуадаптера 1 соответственно шины 15 и 17, для полуадаптера 2 16 и 18), первые и вторые выходы полуадаптера (для полуадаптера 1 шины 19 и 21, для полуадаптера 2 шины 20 и 22). Полуадаптеры связаны между собой сигналами управления. Адаптер канал-канал связан с сопрягаемьвли каналами ввода-вывода с помощью шин каналов 15 и 16 и/или

17 и 16 и/или 15 и 18 и шин абонентов

19 и 20 и/или 21 и 20 и/или 19 и 22.

Регистр команд 3 и дешифратор команд 4 предназначены соответственно для хранения и расшифровки кода команды канала. Первый регистр гщреса 5 хранит адрес полуадаптера, присвоенный ему в системе (рабочий режим работы), второй регистр адреса 13 хранит адрес полуадаптера, присвоенный ему в тестовом режиме или в канале ввода-вывода резервной ЭВМ Регистры адресов 5 и 13 могут быть выполнены в виде тумблерного регистра. Коммутатор адресов 14 в зависимости от сигнала на его управляющем входе передает на первые входы узла сравнения адресов 6 адре полуадаптера, хранящийся в первом регистре адреса 5 или во втором регистре адреса 13. Узел сравнения адресов 6 производит сравнение ад.реса, полученного от канала, с адрессш полуадаптера.

Узел управления полуадаптера состоит из входного дешифратора 23, триггеров состояний 24-28, дешифратора состояний 29, выходного дешифратора 30, генератора синхросигналов 31, триггера ОКОНЧАНИЕ 32, триггера ОЖИДАНИЕ 33. Входной дешифратор 23 в зависимости от сигналов управления от ка нала, поступающих с выхода входног коммутатора 11, сигналов, поступаю щих с выходов дешифратора команд 4 узла сравнения адресов 6, входа-вы хода узла управления смежного полу адаптера, и сигналов с выхода дешифратора состояний 29 и триггеров ОКОНЧАНИЕ 32 и ОЖИДАНИЕ 33 формиру ет сигналы, поступающие на динамические входы триггеров состояний 24-28, Изменение состояний триггеров 24-28 происходит по синхросигна лам генератора 31, Дешифратор состо яний 29 дешифрирует состояния триггеров 24-28. В зависимости от выходных сигналов дешифратора состояний 29 и сигналов на входах-выходах узла управления выходнйй дешифратор 30 формирует на вьлкодах узла управления сигналы, поступающие на входы выходного коммутатора 12, .группы элементов ИЛИ ..8, регистрс1 байта состояния 9, буферного регист ра 10, регистра команд 3, входы-выходы узла управления 7 смежного полуадаптера, обеспечивающие работу адаптера по заложенному алгоритму. По выходным сигналам узла управления 7 в регистре байта состояния 9 формируется байт состояния полуадаптера. Буферный регистр 10 предназначен для хранения информации, передаваемой через адаптер канал-канал. Группа элементов ИЛИ 8 предназначена для коммутации информации, передаваемой по информационным шинам абонента в канал. Входной коммутатор интерфейса 11 служит для подключения полуадаптера К информационным и управляющим шинам одного из двух каналов (шины 15 и 17). Выходной коммутатор интерфей са 12 служит для подключения информационных и управляющих шин абонента к одному из двух каналов (шины 19 и 21) . Различны схемы подключения адаптера канал-канал, обеспечивакедего автономный контроль ЦВМ 1 и ЦВМ 2 вЕлчислительного комплекса, и переключение на резерв. Работает адаптер канал-канал i следующим образом. Режим работы полуадаптера (рабочий, контроля или переключения на резерв) задается с помощью одного разряда в коде команды смежного полуадаптера ( оговоренного в системе команд адаптера канал-канал). Один из каналов ввода-вывода является в дущим, он и задает режим работы смежного полуадаптера в исходном положении значение управляющего разряда в регистре команд 3 каждого полуадаптера нуле вое, что соответствует рабочей схеме подключения адаптера каналканал (к каналу 1 ЦВМ 1 и каналу 1 ЦВМ 2) . ВедуЕаий канал ввода-вывода (например, канал 1 ЦВМ 1) производит начальн;ло выборку адаптера. При этом адрес от канала по шинам 15 поступает через входной коммутатор интерфейса 11 в узел сравнения адресов 6 для сравнения с адресом полуадаптера, хранящимся в первом регистре адреса 5. Результат сравнения адресов поступает в узел управления 7. Бели адреса совпадают, из регистра адреса 5 через коммутатор адресов 14, группу элементов ИЛИ 8 и выходной коммутатор интерфейса 12 на информационные шины абонента 19 выдается адрес полуадап тера. Канал 1 ЦВМ 1 .сравнивает адрес, полученный от адаптера7 с адресом, ранее выданным на шины канала 15, и при их совпадении вьщает на шины 15 код команды обмена, который через входной коммутатор интерфейса 11 поступает в регистр команд 3, и расшифрювывается дешифратором команд 4. Управлякщий разряд кода команды с второго выхода регистра команд 3 поступает на управляющие входы коммутатора адреса 14, входного коммутатора интерфейса 11 и В)Ыходного коммутатора интерфейса 12 смежного полуадаптера 2. В рабочем режиме значение этого разряда равно О и полуадаптер 2 подключен к шинам 16 и 20, т.е. соединен с линией интерфейса канала 1 ЦВМ 2. Если канал 1 ЦВМ 1 задает контрольный режил:: работы, то значение управляющего разряда в коде команды равно 1, при наличии единичного сигнала на втором выходе регистра команд 3 первого полуадаптера 1 полуадаптер 2 подключается к шинам 18 и 22, т.е. к линии интерфейса канала 2 ЦВМ 1. Сигнал1а с выхода дешифратора команд 4 поступают на входы узла управления 7. После расшифровки команды канала 1 ЦВМ 1, требующей соответствующей команды канала 1 ЦВМ 2 (при задании рабочего режима) или канала 2 liBM 1 (при задании тестового режима) первый полуадаптер 1 помещает код команды в буферный регистр 10 и выдает сигнал ожидания согласования, который поступает во второй полуадаптер 2. Последний выдает в канал, к которому он подключен байт состояния с указателем ВНИМАНИЕ, в ответ на который канал посылает в полуадаптер 2 команду уточнения состояния. По команде уточнения состояния полуадаптер 2 передает каналу содержимое буферного регистра 10 первого полуадаптера 1, т.е. команду, присланную каналом ЦВМ 1. Программа канала 1 ЦВМ 2 (в рабоче режиме) или канала 2 ЦВМ 1 (в конт рольном режиме) определяет, какая манда должна быть послана в полу,адаптер 2 и посылает ее. Если команды согласованы (команда записи согласуется с командой считывания и наоборот), полуадаптер 2 посылае в узел управления 7 первого полуадаптера 1 сигнал подтверждения согласования, после чего оба полуадаптера совместно выполняют команды обмена. При этом байт инфо|рмации, полученный от канала вводавывода, производящего запись, поме щается в буферный регистр 10 подкл ченного к нему полуадаптера, в смежный полуадаптер посыпается сиг нал готовности, по которому тот производит передачу в сопряженный с ним канал этого байта инфо яхацию через группу злементов ИЛИ 8 и выходной коммутатор 12, в первый полуадаптер выдается сигнал подтверж дения приема инфоЕ ации. При проверке адаптера с псмОщью ЦВМ 2 ведущим каналом является канал I ЦВМ 2, подключенный через шины 16 и 20 к полуадаптеру 2. А по единичному значению управляющего разряда в коде команды канал управляетвходньм коммутатором интерфейса 11, выходишь кс «мутатором интерфейса 12 и коммутаторе адгМ.

I . г П- .| И1|«в

13 21

:1

Jl г

:rj L

ГфW 22

Фиг.1 раса 14 полуадаптера 1, подключая полуадаптер 1 к шинам 17 и 21,,т.е; к каналу 2 ЦВМ 2. При переключении на резерв к каналу 1 ЦВМ 3 при неисправности канала 1 ЦВМ 1, первый 5 и второй 13 регистры адресов хранят адрес полуадаптера для ЦВМ 1 и ЦВМ 3 для полуадаптера 1, для ЦВМ 2 и ЦВМ 3 для полуадапт ра 2. При обнаружении не- исправности в ЦВМ 1 канал 1 цЬ11 2 вводит в адаптер команду с единичным значением управляющего разряда в коде команды, который осуществляет подключение полуадаптера 1 к каналу 1 ЦВМ 3. Аналогичные действия производятся со стороны канала 1 ЦВМ 1 при .обнаружении неисправности по ЦВМ 2. Таким образом предложенный адаптер канал-канал в отличие от известных устройств обладает более широкими функциональными возможностями: обеспечивает возможность контроля адаптера канал-канал с помощью одной 1ЩМ, входящей в вычислительный комплекс без механической перекоммутацйи разъемов и/или переключения на резервную ЦВМ без механической перекоммутации разъемов, построение вычислительного ксилплекса из четырех lB3f4, каждая из которых способна производить обмен с двумя другими.

TI 24Г

}-

72

fffn6 25

Ofnii -

2J

h М

TJ 26

-

ffm 8

нежного oflyaffanmepa

Tf 27

-

31

К9 J

30

К денежного

fffPHyeffffe no/iyo infn

-Ч

J2

вкШцие

- 33

Ё

| Устройство управления передачей информации между вычислительными машинами | 1973 |

|

SU525078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| и др | |||

| РЕЛЕ | 1924 |

|

SU1050A1 |

| Статистика , 1976, с | |||

| Способ укрепления под покрышкой пневматической шины предохранительного слоя или манжеты | 1917 |

|

SU185A1 |

Авторы

Даты

1984-01-15—Публикация

1982-01-08—Подача