I

Изобретение относится к вычисли тельной технике, в частности к уст- ройствам для деления двух величин, заданных электрическими напряжениями постоянного тока, и может быть использовано в автоматике и измери,тельной технике.

Известно множительно-делительное устройстййо время-импульсного типа, содержащее две зарядные RC-цепочки, первая своим входом подключена к источнику напряжения делителя, а вторая - к источнику стабилизированного напряжения;два ключа, упрйвляю;-;: щие зарядом-разрядом RC-цепи; компаратор, тригге р, амплитудный детек-. тор и генератор импульсов тактовой частоты. Причем одйН из входов компа ратора подключен к источнику напряжения делимого, а второй ето вход к выходу первой КС-цепочки; триггер одним входом подключен к генератору импульсов тактовой частоты, вторым своим входом соединен с выходом

паратора, а выходом соединен с упраВ ляющими входами обоих ключей; а амп-i литудный детектор подключен к выходу второй ВС-цепочки l.

Недостатком этого устройства является наличие погрешности измерения отношения, возникающей из-за наличия порогового напряжения амплитудного детектора. Компенсацию порогового напряжения можно осуществить только при максимальных величинах входного сигнала, что приводит, в свою очередь, к снижению динамического диапазона входных сигналов и изме-i ряемого отношения. Другим источником погрешности измерения отношения является нестабильность частоты повторения импульсов генератора и в1ульсов тактовой частоты.

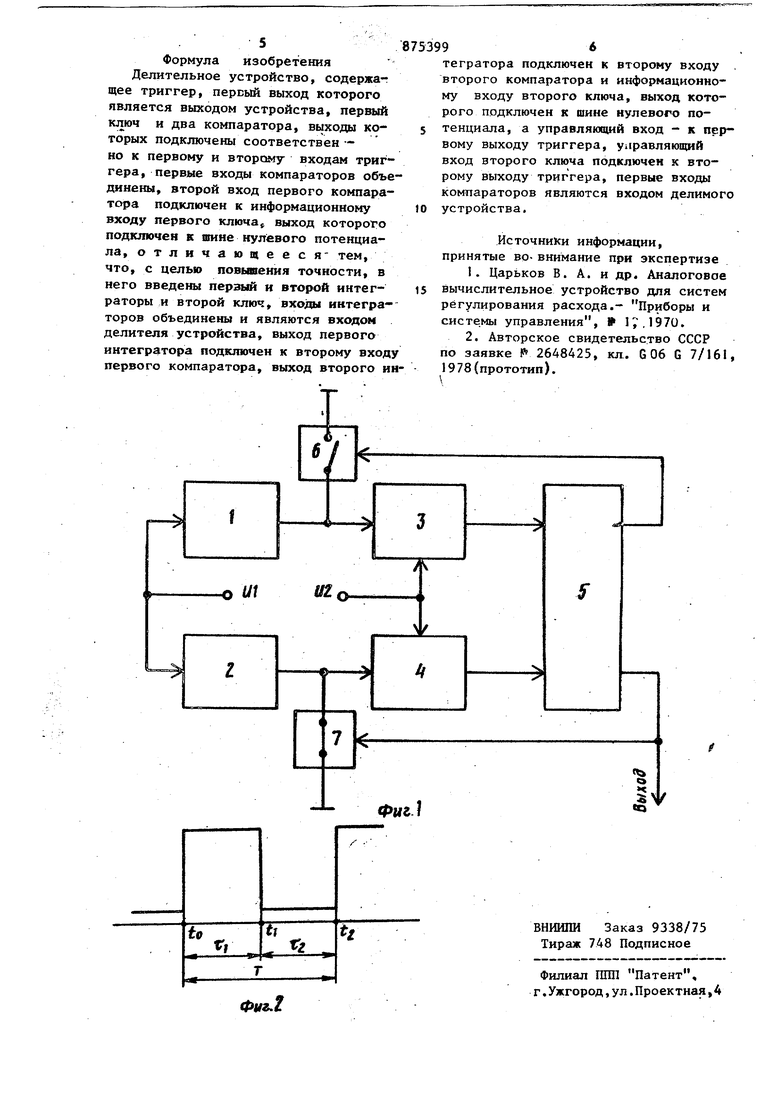

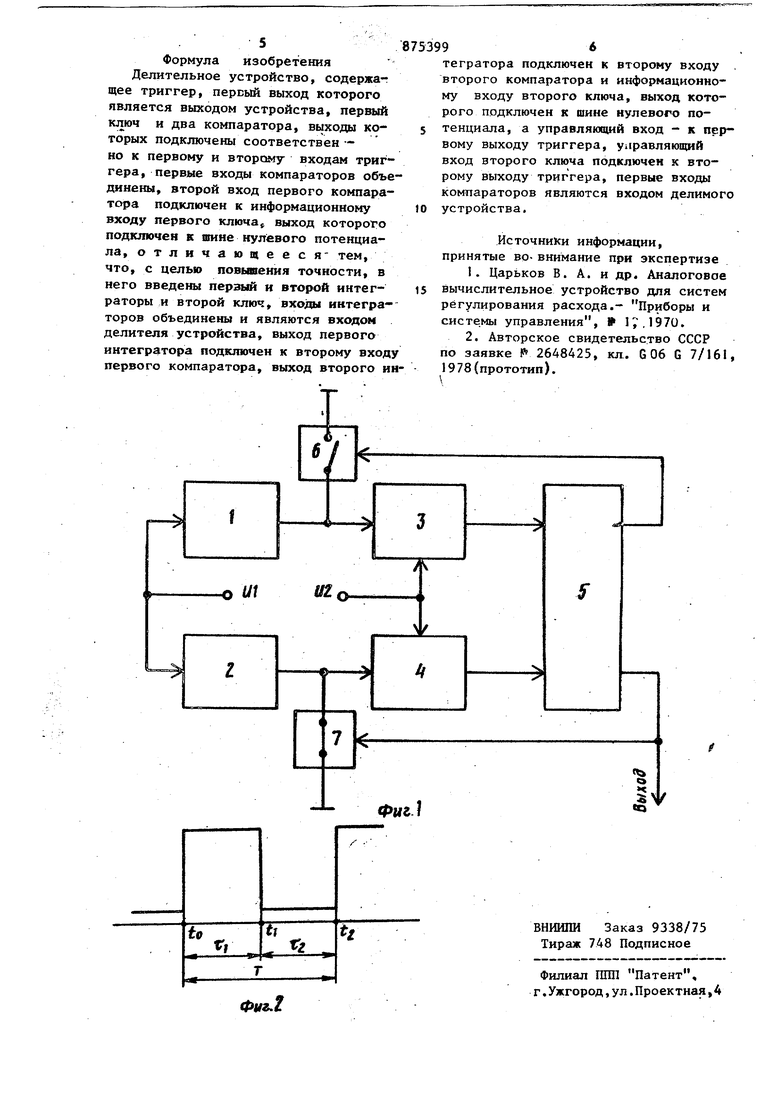

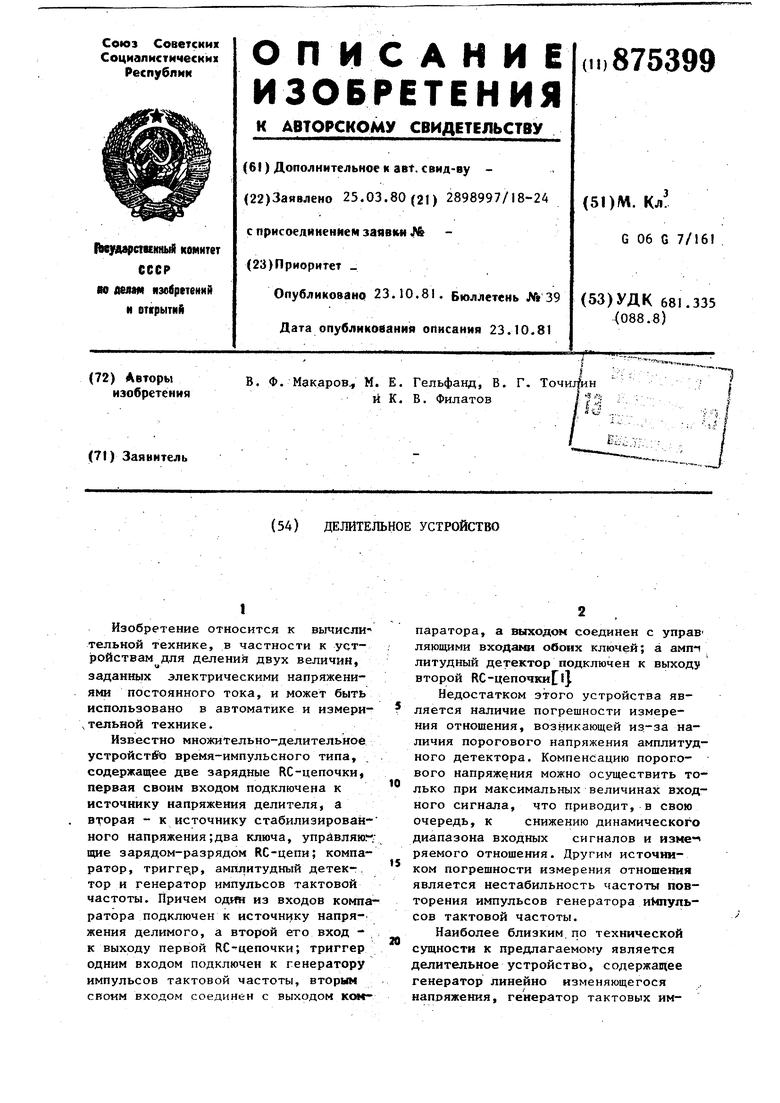

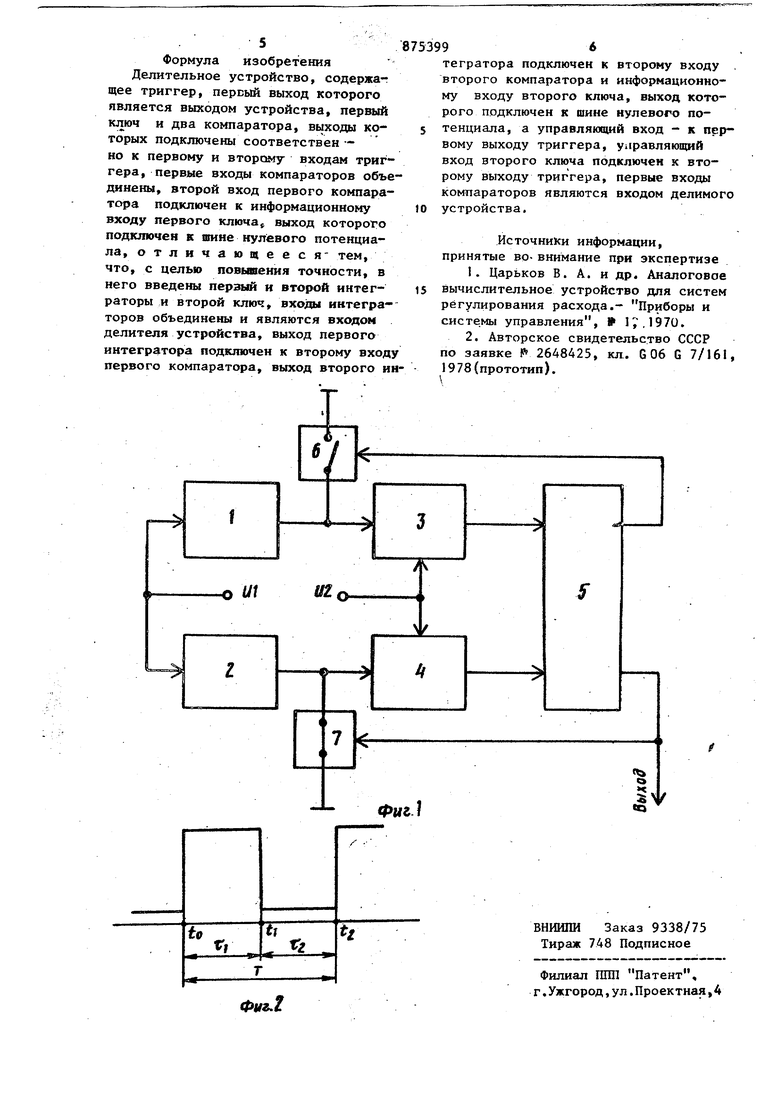

Наиболее близким.по технической сущности к предлагаемому является дели тельное устройство, соде ржаще е генератор линейно изменяющегося напояжения, генератор тактовых импульсов , выход которого подключен к первому входу генератора линейно изменяющегося напряжения, два компаратора первые входы которых объ.единены и подключены к выходу генератора линейно-изменяющегося напряг жения, а вторые входы подключены соответственно к источникам напряжения делимого и делителя, выходы компараторов подключены к соответствунидим входам триггера, выход которого является выходом устройства, ключ, первый информационш 1й вход которого подключен к второму входу пер вого компаратора и источнику напряжения делимогоi второй и1формационный вход ключа через первый резистор подключен к второму входу второго компаратора и источнику напряжения делителя, а через последова-п тельно соединенные первый и второй резисторы - к шине нулевого потенциала, выход ключа подключен к второму входу генератора линейно изменяющегося напряжения. С27 I . . Недостатком известного устройства является наличие погрешностей измерения отношения. Цель изобретения - повышение точности работы делительного устройства. Поставленная цель достигается тем что в делительное устройство, содержащее триггер, первый выход которого является выходом устройства, первый ключ и два компаратора, выхог ды которых подключены соответственно к первому и в.торому входай триггера, первые входы компараторов объединены, второй вход первого компагг ратора подключен к информационному входу первого ключа, введеш пер: вый и второй интеграторы и второй ключ, входы интеграторов объединены и являются входом делителя устройства, выход первого интегратора подключен К второму входу первого компаратора, выход второго интеграто ра подключен к второму входу второ го компаратора и информационному вх ду второго кл1оча, выходы первого и второго ключей подключены к шине ну левого потенциала, а управляющий вх к первому выходу триггера, управляю щий вход второго ключа подключен к втор,ому выходу триггера, первые вхо ды компараторов являются входом дел мого устройства. На фиг. 1 приведена блок-схема предлагаемого устройства; на фйг.2эпюра выходного напряжения. Делительное устройство содержит два канала, состоящих из интегра торов 1 и 2 входы которых объединены и подключены к источнику напряжения делителя , и компараторов 3 и 4, выходы которых подключены к соответствуюпдам входам триггера 5, первые входы объединены и подключены к источнику напряжения делимого, а вторые входы компараторов подключены к выасодам интеграторов, выходы триггеР 5 соединены с управляющими входами ключей 6 и 7, информационные входы которых подключены соответственно к выходам интеграторов 1 и 2, а выходы ключей подключены к шине нулевоГО потенциала. На эпюрах выходных напряжений (г. 2) показаны длительности 4 устойчивых состояний триггера 5; период Т повторения импульсов на выходе триггера 5. Делительное устройство работает следующим образом. Триггер 5 в исходном состоянии (момент времени ) замыкает ключ 7 и размыкает ключ 6. При этом на выходе интегратора 1 появляется линейно нарастающее напряжение. В момент времени t это напряжение достигает величины напряжения делимого, подаваемого на второй вход компаратора 3, последний при этом вьфабатывает импульс, поступающий на один из входов триггера 5. Триггре 5 опрокидывается, замыкает ключ 6 и размыкает ключ 7. В этот момент напряжение на интеграторе 1 падает, а на интеграторе 2 начинает линейно нарастать. В момент времени t2 напряжение на выходе интегратора 2 достигает величины напряжения делимого, подаваемого на второй вход компаратора 4, последний при этом возбзгждается и вырабатывает импульс, который поступает на второй вход триггера 5 и возвращает его в положение, соответствующее моменту времени t. Триггер 5 размыкает ключ 6 и замыкает ключ 7. Схема возвращается в исходное состояние. При этом период повторения импульсов на выходе триггера 5 пропорционален искомому отношению. Изобретение позволяет повысить точность измерения.

Формула изобретения Делительное устройство, содержаг щее триггер, первый выход которого является выходом устройства, первый ключ и два компаратора, выходы которых подключены соответствен - но к первому и второму входам триггера, первые входы компараторов объединены, второй вход первого компаратора подключен к информационному входу первого ключа, выход которого подключен к шине нулевого потенциала, отличающееся- тем, что, с цепью повьопения точности, в него введены первый и второй интеграторы и второй ключ, входы интеграторов объединены и являются входом делителя устройства, выход первого интегратора подключен к второму вход первого компаратора, выход второго итегратора подключен к второму входу , второго компаратора и информационному входу второго ключа, выход которого подключен к шине нулевого потенциала, а управляющий вход - к первому выходу триггера, у.фавляющий вход второго ключа подключен к второму выходу триггера, первые входы компараторов являются входом делимого

устройства.

Источники информации, принятые во- внимание при экспертизе

1.Царьков В. А. и др. Аналоговое вычислительное устройство для систем

регулирования расхода.- Приборы и систе. управления, № 1 7,1970.

2.Авторское свидетельство СССР

по заявке ( 2648425, кл. G 06 G 7/161,

1978(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Делительное устройство | 1979 |

|

SU805342A1 |

| Делительное устройство | 1978 |

|

SU750505A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Аналого-цифровое делительное устройство | 1979 |

|

SU886017A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| Устройство для измерения сопротивления | 1988 |

|

SU1649468A1 |

| Делительное устройство | 1982 |

|

SU1070569A1 |

| Времяимпульсное множительно-делительное устройство | 1980 |

|

SU1277142A1 |

| Аналоговое делительное устройство | 1979 |

|

SU834712A1 |

Авторы

Даты

1981-10-23—Публикация

1980-03-25—Подача