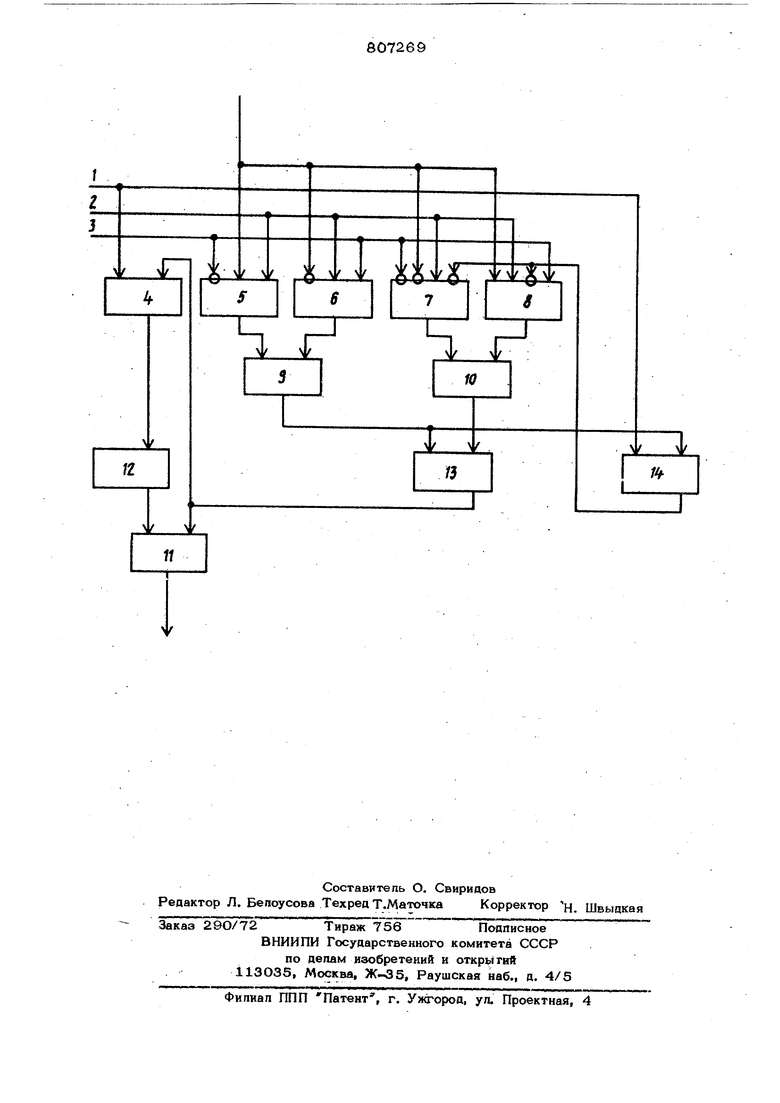

(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЙ БУЛЕВЫХ ФУНКЦИЙ ,38 де и не могут быть определены для аргу1ментов, часть из которых задана в инвертированном виде. Так для булевой функции (AX,.)v()vX известное устройство сформирует правильное значение, однако для функции (,,AX3)V(K4.X5)VXg значение на выходе устройства не будет соответствовать истинному значению заданной функции. Цель изобретения - расширение класса решаемых задач за счет возможности задания аргумента в инвертированном виде. Поставленная цель достигается тем, что устройство для определения значений булевых функций, содержащее первый, вто,рой и третий элементы И, три блока памяти, элемент ИЛИ, информационный вход устройства, соединенный с первым входом третьего элемента И и с запрещающим входом второго эпемента И, выход синхронизации устройства соединен с первым входом второго и вторым входом третьего элементов И, вход кода операций устройства соединен с первым входом первого : элемента И, с входом Установка О первого блока памяти, выход второго блока памяти соединен со вторым входом первого элемента И и с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу третьего блока памяти, Ежод которого соединен с выходом первого элемента И, выход первого блока памяти соединен с запрещаюцим входом третьего элемента И, а выход первого элемента ИЛИ является выходом устройства, дополнительно содержит, четвертый и пятый элементы И, второй и третий эле менты ИЛИ, причем вход признака аргумента устройства соединен с запрещающим вжодсм четвертого эпемента И, со вторым входом второго элемента И, с запрещ клдим первым входом пятого элемен та И и с третьим входом третьего эпемента И, первый вход четвертого элемента И и запрещающий второй вход пятого элемента И соединены с информационным входом устройства, второй вход четвертого и вход пятого элементов И соединены с Екодом синхронизации устройства, запрещающий третий Екод пятого элемента И соединен с выходом первого блока памяти, выхощз второго и четвертого элементов И соединены с входами третьего эпемента ИЛИ, выходы третьего и пятого элементов И соединены с входами второг эпемента ИЛИ, выход третьего элемента ИЛИ соединен с входом Установка О второго бпока памяти и с входом Установка 1 первого блока памяти, выход 9 второго элемента ИЛИ - с входом Устаовка в 1 второго блока памяти. На чертеже представлена схема устрой ства для определения значения булевых функций. Устройство содержит вход 1 кода операции, вход 2 синхронизации, шина 3 признака аргумента, .элементы И 4-8, элементы ИЛИ 9-11, блоки 12-14 памяти. Устройство работает следующим образом. На вход устройства последовательно поступают аргументы заданной булевой функции, значение которой следует определить. Импульсы синхронизации стробируют поступление сигналов на второй, третий, четвертый и пятый элементы И. Одновременно с поступлением каждого входного сигнала на шине 3 признака аргумента формируется сигнал логическая 1, если аргумент входит в булевое выражение в прямом коде, и сигнал логическай О, если аргумент входит в выражение в инвертированном коде. В зависимости от значения аргумента (О или 1) и сигиада на шине 3 входной сигнал про ходит через второй, третий, четвертый или пятый элементы И. Входной сигнал с уровнем 1югнческая 1, если аргумент аадан в прямом коде, и с уровнем логический О, естш аргумент задан в инвертированном виве, поступает на вход Установка 1 второго блока памяти. Если же входной сигнал имеет уровень логический О для аргумента, заданного в прямом коде, кпя логическая 1 для аргумента, заданного в прямом коде, или {югическая 1 для аргумента, заданного в инвертированном виде, то он устанавливает в, нулевое состояние второй блок памяти и в единичное состояние третий блок памяти. Единичное состояние третьего блока памяти блокирует поступление поспедукших сигналов на вход Установи ка 1 второго блока памяти, обеспечивая правильное выполнение операции конъюнкция. Сигнал на входе 1 появляется в промежутках между импульсами синхронизации, путем операции конъюнкция соответствует уровень логический О, а операции дизъюнкция-уровень логическая 1. При выполнении операции дизъюнкция сигнал на входе 1 устанавливает в нулевое состояние третий блок памяти, разблокируя третий и пятый элементы И и разрешая установку в единичное состояние второго бпока памяти, если следующий входной сигнал имеет уровень логическая 1 и аргумент задан в прямом коде или входной сигнал имеет уровень логический О и аргумент задан в инвертированном коде. Одновременно, сигнал логическая 1 на Входе 1 разрешает лерезапись единичного состояния второго блока памяти в первый блок памяти, фиксируя тот факт, что хотя бы один дизъюнктивный член в двоичной последовательности равен 1. После прохождения всей последовательности входных сигналов на выходе первого эпемента ИЛИ имеет место значение заданной булевой функции. Известные устройства обеспечивали возможность определения только функций для аргументов, заданных в прямом виде и не поавопяпи определять функции аргументов, часть из которых задается в инвертированном виде. Это приводило к необходимости создания сложных схем для систем, применяющихся лрп управлении и контроле техническими средствами, агр/егагами и технологическими npoueccaivJe в различных отраслях промышленности и народного хозяйства.. Применение предлагаемого технического решения обеспечит возможность сократить расходы на аппаратурную реализацию устройств для определения значений булевых функций, что значительно уменьшит затраты в целом на создание систем для управления техническими и технологическими средствами. Формула изобретения Устройство для определения значений булевых функций, содержащее первый, вто рой и третий элементы И, три блока памя . ти, элемент ИЛИ, информационный вход устройства соединен с первым входом тре тьего эпемента И и с запрешающкм входом второго элемента И, вход синхронизации устройства соединен с первым входом второго и вторым входом третьего элементов И, вход кода операций устройства соединен с первым входом первого элемента И, с входом Установка О первого блока памяти выход второго блока памяти соединен со вторым входом первого элемента И, с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу третьего блока памяти, вход которого соединен с вь:ходом перво- . го элемента И, выход первого блока памяти соединен с запрещающим входом третьего элемента И, а выход первого элемента ИЛИ является выходом устройства, отличающееся тем, что, с целью расширения класса решаемых з,адач за счет возможности задания аргумента в инвертированноКл виде, оно дсиолнительнс содержит четвертый и пятый элементы И, второй и третий элемент, ИЛИ, причем вход признака аргумента устройства соединен с запрещающим BXOIOM четвертого элемента И, со вторым входом второго элемента И, с запрещающим первым входом пятого элемента И, с третьим. входом третьего элемента И, первый вход четвертого элемента И и запрещающий второй вход пятого эпемента И соединен с информационным входом устройства, второй вход четвертого и вход пятого элемента И соединены с входом синхронизации устройства, запрещающий третий вход пятого элемента И соединен с выходом первого блока памяти, выходы второго и четвертсяо элементов И соединены с входами третьего элемента ИЛИ, выходы третьего и пятого элементов И соединены с входами второго элемента ИЛИ, , выход ретьего элемента ИЛИ соединен с входом yctaHOBKa О второго блока памяти и с входом Установка 1 первого блока памяти, выход второго элемента ИЛИ соединен с входом Установка 1 второго блока памяти. Источники информации, принятые во внимание при экспертизе 1. Патент США Na 3832696, кл. 235-164, 72. 2. Патент Великобритании 1466466, кл. Н 3 Р, 72 {прототип)

у Фу| Ф

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения значений буле-ВыХ фуНКций | 1979 |

|

SU840882A1 |

| Устройство для определения значений булевых функций | 1982 |

|

SU1037240A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для определения значений булевых функций | 1990 |

|

SU1805462A1 |

| Цифровой функциональный преобразователь | 1989 |

|

SU1695321A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ЦИФРОВЫХ СХЕМ | 1992 |

|

RU2042196C1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2207612C2 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2004 |

|

RU2273042C2 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2222822C2 |

Авторы

Даты

1981-02-23—Публикация

1978-06-20—Подача