Изобретение относится к вычислительной технике, в частности к устройствам вычисления функций, и может быть использовано в ЭВМ в качестве сопроцессора для вычисления произвольных функций или как самостоятельное устройство в системах цифрового автоматического управления,

Целью изобретения является повышение быстродействия.

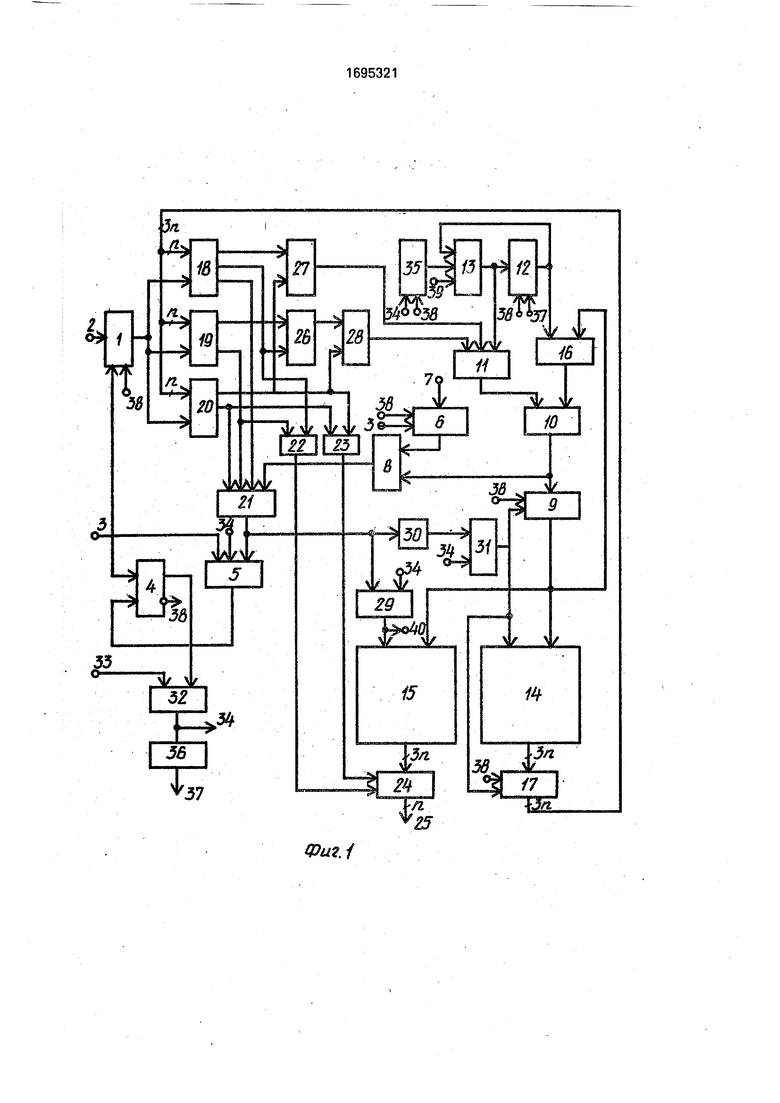

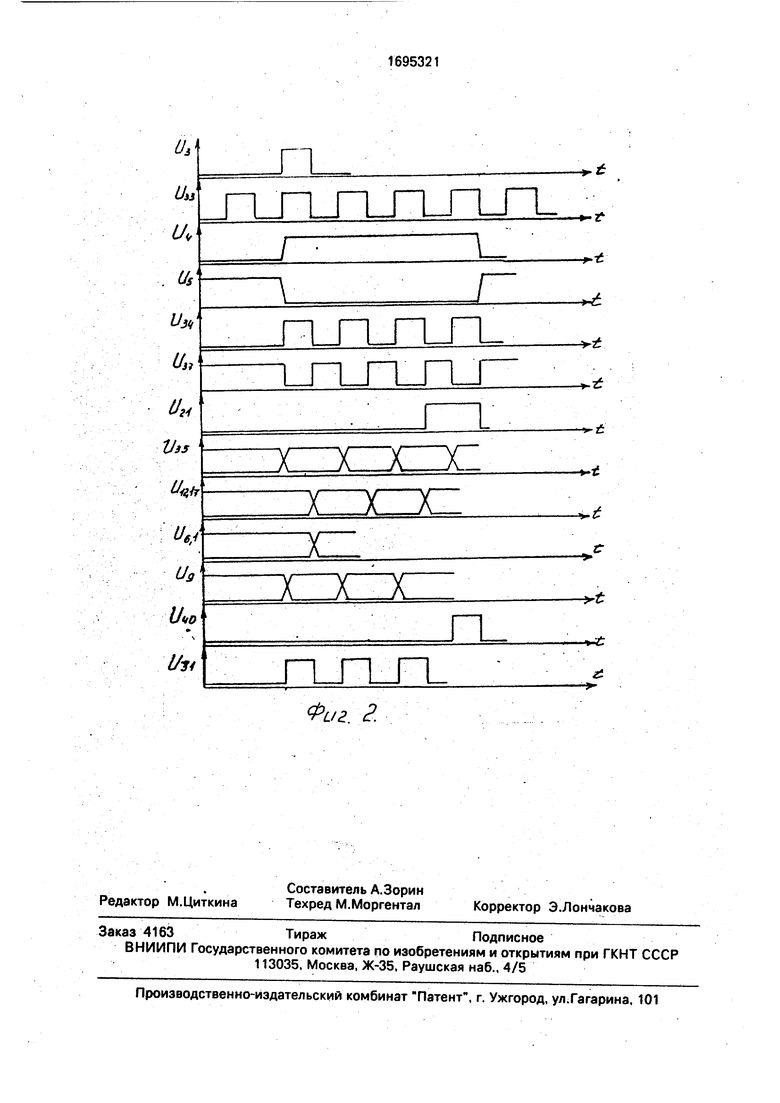

На фиг.1 представлена блок-схема преобразователя; на фиг.2 - временные диаграммы работы преобразователя.

Преобразователь содержит регистр 1 аргумента, первый информационный вход 2, вход 3 запуска, триггеры 4 и 5, регистр 6 верхней границы, второй информационный вход 7, схему сравнения 8, регистр 9 последовательных приближений, сумматоры 10 ч 11, регистр 12 нижней границы, сумматор 13, блоки памяти 14 и 15, вычитатель 16.

регистр 17 промежуточного хранения, схемы сравнения 18-20, элементы ИЛИ 21-23, мультиплексор 24, выход 25 устройства, элемент И 26, элементы ИЛИ 27-28, элемент И 29, элемент НЕ 30, элементы И 31-32, вход 33 тактовых импульсов 33, выход 34 элемента И 32, сдвиговый регистр 35, элемент НЕ 36, выход 37 элемента НЕ 36, инверсный выход 38 триггера 4, вход 39 логического нуля, выход 40 готовности.

Цифровой функциональный преобразователь работает следующим образом.

В исходном состоянии в первом блоке 14 памяти записаны дискретные значения аргумента, причем квантование выполнено таким образом, что расстояние между двумя любыми значениями функции одинаковы. Во втором блоке 15 памяти в одноименных ячейках записаны соответствующие значения функции. В исходном состоянии триггер 4 находится в нулевом состоянии, все разряды регистра 17 промежуточного хранения, регистра 9 последовательного приближения, регистра 12 нижней границы и сдвигового регистра 35 - в нулевом состоянии, все разряды регистра 1 аргумента и регистра 6 верхней границы - в единичном, для того чтобы исключить ложное срабатывание устройства в нулевом такте.

При необходимости вычисления функции на первый информационный вход 2 устройства подается код аргумента, на второй информационный вход 7 - максимальный адрес первого блока 14 памяти. Одновременно на вход запуска устройства подается единичный сигнал (см. фиг.2), по которому производится запись указанной выше информации соответственно в регистр 1 аргумента и регистр 6 верхней границы (переключение регистров 1 и 6 осуществляется по заднему фронту синхроимпульса), сброс триггера 5 в нуль, установка первого триггера 4 в единицу, причем сигнал с прямого выхода триггера 4 открывает элемент И 32 для прохождения синхроимпульсов с тактового входа 33 устройства на вход сдвигового регистра 35, на вход элемента НЕ 36, с выхода которого инвертированные синхроимпульсы поступают на регистр 12 нижней границы, кроме того с выхода 34 первого элемента И 32 синхроимпульсы поступают на вход второго 29 и четвертого 31 элементов И и соответственно, при определенных условиях, на входы синхронизации второго 15 и первого 14 блоков памяти, а также на регистр 17.

Под действием последовательности синхроимпульсов среди кодов, хранящихся в первом блоке 14 памяти, реализуется поиск ближайшего к аргументу зафиксированного на регистре 1. Указанный поиск осуществляется последовательным выделением интервала, заключающего в себе исковый код, причем на каждом шаге величина этого

интервала уменьшается в четыре раза.

В каждом такте вычисляется адрес ячейки первого блока 14 памяти, в которой содержатся три кода аргументов, делящие интервал, определенный в предыдущем такте (для нулевого такта таким интервалом является весь интервал изменения аргумента) на четыре части. При этом в первой трети разрядов ячейки блока 14 памяти содержится код аргумента, делящий указанный интервал пополам (первый код аргумента), во второй и третьей трети разрядов ячейки - соответственно второй и третий коды аргумента, которые делят первую и вторую половину интервала пополам. Адрес

анализируемой ячейки блока 14 памяти вычисляется следующим образом:

AI Н. + (Ам - Нм) 4 + V, где i - номер такта (I 0,1,2,...); АО 0;

Hi - начальный адрес ячейки на l-м ярусе блока 14 памяти;

Но 0; и

Hi - НН + 4м;

V - номер варианта VЈ {0,1,2,3} и определяется следующим образом: V 0, если искомый аргумент находится в первой четверти соответствующего интервала, V 1, если аргумент находится во второй четверти.

интервала, V 2, если аргумент находится в третьей части интервала, V 3, если аргумент находится в четвертой четверти интервала.

Адрес анализируемой ячейки блока 14 памяти вычисляется к началу каждого такта и фиксируется по фронту синхроимпульса на регистре 9 последовательных приближений, так как на вход синхронизации регистра 9 через элемент И 31, на второй вход которого подается единичный сигнал с выхода элемента НЕ 30 (на выходе первого элемента ИЛИ 21 - нулевой потенциал), поступает синхроимпульс с выхода 34 элемента И 32. Этот же синхроимпульс с выхода элемента И 31, поступая на вход синхронизации первого блока 14 памяти, инициирует считывание информации из последнего. Считанные коды трех аргументов фиксируются на регистре 17 промежуточного хранения (регистр 17 построен на триггерах с внутренней задержкой), откуда поступают на схемы 18,19,20, сравнения, где каждый считанный код сравнивается с кодом аргумента, зафиксированным на регистре 1 аргумента. Если один из считанных кодов совпадает с кодом поступившего аргумента, то на выходе Равно соответствующей из схем сравнения 18,19,20 формируется единичный сигнал, который свидетельствует о том, что искомое ближайшее к заданному аргументу найдено, а его адрес зафиксирован на регистре 9 последовательного приближения.

Если ни один из считанных кодов не больше поступившего аргумента, то на выходах Больше схем сравнения 18,19,20,а соответственно, и на выходах элементов ИЛИ 27,28 сформируется нулевой потенциал и таким образом номер варианта V 00, так как очевидно, что в этом случае искомое ближайшее к заданному аргументу находится в первой четверти исследуемого интервала.

Если только один из считанных аргу- ментов (второй) больше аргумента поиска (на выходе Больше схемы 19 сравнения в этом случае будет единица), на выходе Меньше первой схемы 18 сравнения единица), то искомое ближайшее к аргументу находится во второй четверти указанного интервала, в этом случае на выходе второго элемента ИЛИ 27 будет сформирован нулевой сигнал, на выходе третьего элемента ИЛИ 28 - единичный сигнал, т.е. V 01. Аналогично если первый и второй считанные коды аргументов больше заданного аргумента, искомое ближайшее находится в третьей четверти исследуемого интервала и единица будет присутствовать на выходе элемента ИЛИ 27 при нулевом потенциале на выходе элемента ИЛИ 28, т.е. V 10. В последнем случае, когда все три считанных аргумента больше кода заданного аргумента (на выходах Больше и всех трех схем 18,19,20 сравнения единицы) V 11, т.е. искомое ближайшее к заданному аргументу находится в последней четверти исследуемого интервала.

Сформированный по описанному спо- собу номер варианта V поступает с выходов элементов ИЛИ 27, 28 на вход первого слагаемого второго сумматора 11. Одновременно на-выходе третьего сумматора 13 формируется код HI Ны + 4 , причем Нм поступает с выходов регистра 12 нижней границы на вход сумматора 13, а слагаемое 2 формируется на выходах сдвигового регистра 35.

Так как информация с выходов регистра 35 поступает только на нечетные входы второго слагаемого сумматора 13, а на четные входы указанного сумматора 13 поступает нулевой сигнал с входа 30 логического нуля, то на входах второго слагаемого сумматора

13 в каждом такте формируется значение 4м. Сдвиг регистра 35 в сторону старших разрядов происходит по заднему фронту синхроимпульсов с заполнением освободившегося разряда единицей в нулевом (начальном) такте и нулем - в последующих.

С выхода регистра 12 нижней границы Н|-1 поступает также одновременно с этим на вход вычитателя 16, на выходе которого формируется разность Аы - Ны (Аы поступает на вход первого операнда вычитателя 16с регистра 9 последовательных приближений). Формируемая на выходе вычитателя 16 разность со сдвигом на два разряда в сторону старших разрядов (т.е. в виде 4 (Аы - Ны) поступает на вход первого слагаемого первого сумматора 10. Таким образом, на выходе сумматора 10 формируется адрес ячейки блока 14 памяти А|, который фиксируется на регистре 9 последовательных приближений. Вычиленный адрес с выхода сумматора 10 поступает на вторую схему 8 сравнения, где сравнивается с максимальным адресом блока 14 памяти. В конце каждого такта по срезу инвертированного синхроимпульса переключается регистр 12 нижней границы, на котором фиксируется поступающий на его входы код Hi с выхода третьего сумматора 13.

Описанная процедура повторяется до тех пор, пока на выходе Равно одной из трех схем 18,19,20 сравнения не будет сформирован единичный сигнал либо код на выходе сумматора 10 не превысит значение адреса последней ячейки блока 14 памяти, т.е. пока на выходе Больше схемы 8 сравнения не появится единичный сигнал. Единичный сигнал с выходов Равно схем 18,19,20 сравнения или с выхода Больше схемы 8 сравнения через элемент ИЛИ 21 поступает на вход установки в единицу второго триггера 5, на второй вход элемента И 29 и через элемент НЕ 30- на вход элемента И31.

В следующем такте, так как на второй вход элемента И 31 поступает с выхода элемента НЕ 30 нулевой сигнал, соответственно, на выходе элемента И 31 будет сформирован нулевой сигнал, который запрещает переключение регистра 9 последовательного приближения, регистра 17 и считывание с блока 14 памяти. В этом случае единичный сигнал с выхода элемента ИЛИ 21, поступая на вход элемента И 29, разрешает прохождение синхроимпульса на вход синхронизации второго блока 15 памяти и синхроимпульс инициирует считывание из указанного блока 15 содержимого ячейки, адрес которой зафиксирован на регистре 9. Единичный сигнал с выхода элемента И 29

поступает также на выход 40 устройства, свидетельствует о том, что на выходах 25 результата устройства сформировано значение функции. На выход блока 15 памяти считываются коды трех значений функции, которые поступают на входы мультиплексора 24, на управляющие входы которого поступают сигналы с выходов четвертого 23 и пятого 22 элементов ИЛИ, причем если на выходах Равно или Больше третьей схемы 19 сравнение присутствует сигнал единичный, а на аналоговых выходах первой 18 и четвертой 20 схем сравнения - нули, а также если на выходах Больше всех трех схем 18,19,20 сравнения - нули (такая ситуация соответствует тому, что ближайшим к заданному аргументу, записанному на регистре 1, является второй аргумент), то на выходах элементов ИЛИ 22 и 23 формируется код 01, который, поступая на управляющие входы мультиплексора 24, коммутирует на его выходы, а следовательно, и на выходы 25 результата устройства сигналы с входов второй группы мультиплексора 24, т.е. код значения функции соответствует второму аргументу.

Если на выходе Равно первой схемы 18 сравнения либо на выходе Больше первой 18 и третьей 19 схем сравнения единичный сигнал, а на выходе Больше четвертой схемы 20 сравнения - нуль (описанная ситуация соответствует тому, что ближайщим к заданному аргументу является первый аргумент из считанных из блока 14 памяти), то на выходах элементов ИЛИ 22,23 сформируется код 00, т.е. в этом случае на выходы 25 результата устройства коммутируются сигналы с первой группы входов мультиплексора 24 (значение функции соответствует первому аргументу).

Аналогично, если на выходе Равно четвертой схемы 20 сравнения либо на выходах Больше всех трех схем 18,19,20 сравнения присуствтует единичный сигнал, то на управляющих входах мультиплексора 24 сформируется код 10, под действием которого на выход 25 результата устройства коммутируются сигналы с третьей группы входов мультиплексора 24 (третьей группы выходов блока 15 памяти), т.е. коды значения функции, соответствующей третьему аргументу (считанному в предшествующем такте из блока 14 памяти), который в этом случае является ближайшим к заданному аргументу, зафиксированному на регистре 1.

В этом же такте по срезу синхроимпульса под воздействием единичного сигнала с выхода элемента ИЛИ 21 устанавливается в единицу второй триггер 5, единичный сигнал с прямого выхода которого сбрасывает

в нуль первый триггер 4, и схема приходит в исходное состояние.

И в прототипе, и в предлагаемом устройстве осуществляется поиск аргумента из числа хранящихся в блоке 14 памяти, ближайшего к заданному аргументу. В прототипе поиск осуществляется путем деления в каждом такте интервала возможного нахождения ближайшего пополам, Соответственно, максимальное число тактов поиска, требуемых в прототипе, равно Iog2m (m - число аргументов, хранящихся в блоке 14 памяти). В предлагаемом устройстве поиск за счет введения дополнительных, парал- лельно работающих схем сравнения осуществляется путем деления в каждом faKTe интервала аргументов, харнящихся в блоке 14 памяти, на четыре. Соответственно, максимальное число тактов поиска в предлага- емом устройстве

IOQ4 m m .

Следовательно, в предложенном функциональном преобразователе достигается,

по сравнению с прототипом, при одинаковых требуемых объемах памяти и трехкратном увеличении числа схем сравнения увеличение быстродействия в 2 раза.

Дальнейшее увеличение быстродействия функционального преобразователя за счет деления интервала на восемь и больше частей практически нецелесообразно, так как сопряжено с резким увеличением аппаратных затрат (так, трехкратное, по сравнению с

прототипом, увеличение быстродействия требует семикратного увеличения числа схем сравнения и такого же усложнения прочих узлов).

Формула изобретения

Цифровой функциональный преобразователь, содержащий первый и второй блоки памяти, первую и вторую схемы сравнения, регистр аргумента, регистр последовательных приближений, первый сумматор, регистр верхней .границы, регистр нижней границы, два триггера, три элемента И, первый элемент ИЛИ, причем первый информационный вход устройства соединен с информационным входом регистра аргумента, выход которого соединен с входом первого операнда первой схемы сравнения, выход первого сумматора соединен с входом первого операнда второй схемы сравнения и информационным входом регистра

последовательных приближений, выход которого соединен с адресными входами первого и второго блоков памяти, вход запуска устройства соединен с входом синхронизации регистра аргумента и входом установки в 1 первого триггера, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен с тактовым входом устройства, выход первого элемента И соединен с входом синхронизации второго триггера и первым входом второго элемента И, инверсный выход первого триггера соединен с входом установки регистра верхней границы и входом установки регистра нижней границы, отличающийся тем, что, с целью повышения быстродействия, в него введены третья и четвертая схемы сравнения, мультиплексор, сдвиговый регистр, регистр промежуточного хранения, второй и третий сумматоры, вычитатель, с второго по пятый элементы ИЛИГдва элемента НЕ, четвертый и пятый элементы И, причем выход первого блока памяти соединен с информационным входом регистра промежуточного хранения, первая, вторая и третья группы выходов ко- торого соединены соответственно с входом второго операнда первой схемы сравнения, первого операнда третьей и первого операнда четвертой схем сравнения, входы второго операнда третьей и четвертой схем сравнения соединены с выходом регистра аргумента, выход Больше первой схемы сравнения соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с вторыми входами третьего и чет- вертого элементов ИЛИ и выходом Больше четвертой схемы сравнения, выход четвертого элемента ИЛИ соединен с первым управляющим входом мультиплексора, второй управляющий вход которого под- ключей к выходу пятого элемента ИЛИ, второй вход которого соединен с вторым входом третьего элемента И и выходом Меньше первой схемы сравнения, выходы Равно первой, третьей и четвертой схем сравнения и выход Больше второй схемы сравнения соединены с первого по четвертый входами первого элемента ИЛИ, выход Равно третьей и четвертой схем сравнения соединены с первыми входами соответ- ственно пятого и четвертого элементов ИЛИ, выход Больше третьей схемы сравнения соединен с первым входом третьего элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выхо- ды второго и третьего элементов ИЛИ соединены с входом первого слагаемого второго сумматора, вход второго слагаемого которого соединен с информационным

входом регистра нижней границы и выходом третьего сумматора, входы четных разрядов второго слагаемого которого соединены с входом логического нуля преобразователя, входы нечетных разрядов второго слагаемого третьего сумматора соединены с выходами разрядов сдвигового регистра, выход регистра нижней границы соединен с входом первого слагаемого третьего сумматора и входом первого операнда вычитателя, вход второго операнда которого соединен с выходом регистра последовательных приближений, выход вычитателя соединен с входом первого слагаемого со сдвигом на два разряда в сторону старших первого сумматора, вход второго слагаемого которого соединен с выходом второго сумматора, первая, вторая и третья группы выходов второго блока памяти соединены с соответствующими информационными входами мультиплексора, выход которого соединен с выходом результата преобразователя, выход первого элемента ИЛИ соединен с входом установки в 1 второго триггера, вторым входом второго элемента И и через первый элемент НЕ с первым входом четвертого элемента И, выход которого соединен с входами синхронизации регистра последовательных приближений, регистра промежуточного хранения и первого блока памяти, выход второго элемента И соединен с входом синхронизации второго блока памяти и выходом готовности преобразователя, вход запуска устройства соединен с входом синхронизации регистра верхней границы и входом установки в О второго триггера, прямой выход которого подключен к входу установки в О первого триггера, инверсный выход которого соединен с входами установки регистра аргумента, сдвигового регистра, регистра последовательных приближений и регистра промежуточного результата, выход первого элемента И подключен к входу синхронизации сдвигового регистра, второму входу четвертого элемента И и входу второго элемента НЕ, выход которого подключен к входу синхронизации регистра нижней границы, второй информационный вход преобразователя соединен с информационным входом регистра верхней границы, выход которого подключен к входу второго операнда второй схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1989 |

|

SU1709303A1 |

| Функциональный преобразователь | 1987 |

|

SU1508207A1 |

| Функциональный преобразователь | 1988 |

|

SU1587500A1 |

| Функциональный преобразователь | 1988 |

|

SU1619258A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления скользящего спектра | 1986 |

|

SU1363240A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

Изобретение относится к вычислительной технике, в частности к устройствам вычисления функций, и может быть использовано в ЭВМ в качестве сопроцессора для вычисления произвольных функций или как самостоятельное устройство в системах цифрового автоматизированного управления. Целью изобретения является повышение быстродействия. Цифровой функциональный преобразователь содержит два блока памяти, четыре схемы сравнения, три сумматора, вычитатель, два триггера, регистр аргумента, регистр последовательных приближений, регистры верхней и нижней границы, сдвиговый регистр, регистр промежуточного хранения, пять элементов ИЛИ, п ять элементов И, два элемента НЕ, мультиплексор. Сущность работы состоит 8 том, что s устройстве реализуется хранение значений т j- гументов и соответствующих им значений функций, причем интервал между соседними значениями аргумента непостоянен, а выбирается исходя из требуемой точности воспроизведения фуннкции на различных участках. При поступлении кода аргумента на регистр осуществляется поиск в упорядоченной таблице аргументов значения, ближайшего к поступившему коду. В каждом такте поиска код аргумента сравнивается с тремя табличными значениями, благодаря чему интервал поиска сокращается на каждом такте в четыре раза, что обуславливает высокую скорость поиска. 2 ил. w Ё О ю ся со го

&u.-f

| Цифровой функциональный преобразователь | 1982 |

|

SU1027732A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1987 |

|

SU1508207A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-30—Публикация

1989-10-17—Подача