1

Изобретений относится к логической обработке бинарных, сигналов и ||ложет быть использовано в различного рода устройствах, связанных с проверкой и анализом состояния двух позиционных элементов, например, в системах контроля и управления, содержащих двухпозиционные датчики, сигнализаторы положения.

Известно устройство для.определения булевых функций,в котором осуществляется последовательный ввод аргументов и производится их логическая обработка,в результате чего на выходе устройства формируется значение заданной булевой функции этих

аргументов I1.

Недостатком устройства является его сложность и низкая скорость работы.

Наиболее близким по технической сущности к предлагаемому является устройство для определения значений булевых функций, содержащее шину кода операции, шину синхронизации, шину признака аргумента, первый, второй, третий, четвертый и пятый элементы И, первый, второй и третий элементы ИЛИ, первый, второй и третий элементы ПАМЯТЬ.

Вход аргумента устройства срединен с первыми входами третьего и пятого элементов И, а также с первыми запрещающими входами третьего и чет-,

вертого элементов И. Шина кода,операции соединена с первым входом первого элемента И и с входом |Установка в третьего элемента ПАМЯТЬ. Шина синхронизации соединена со вторыми входами второго, третьего, чет- вертого и пятого элементов И. Ыина признака аргумента соединена с третьими входами третьего и пятого элементов И и с третьими запрещающими

5 входами второго и четвертого элементов И. Выходы второго и терьего элементов И соединены с входами второго элемента ИЛИ, а выходы четвертого пятого элементов И соединены с

0 входами элемента ИЛИ.

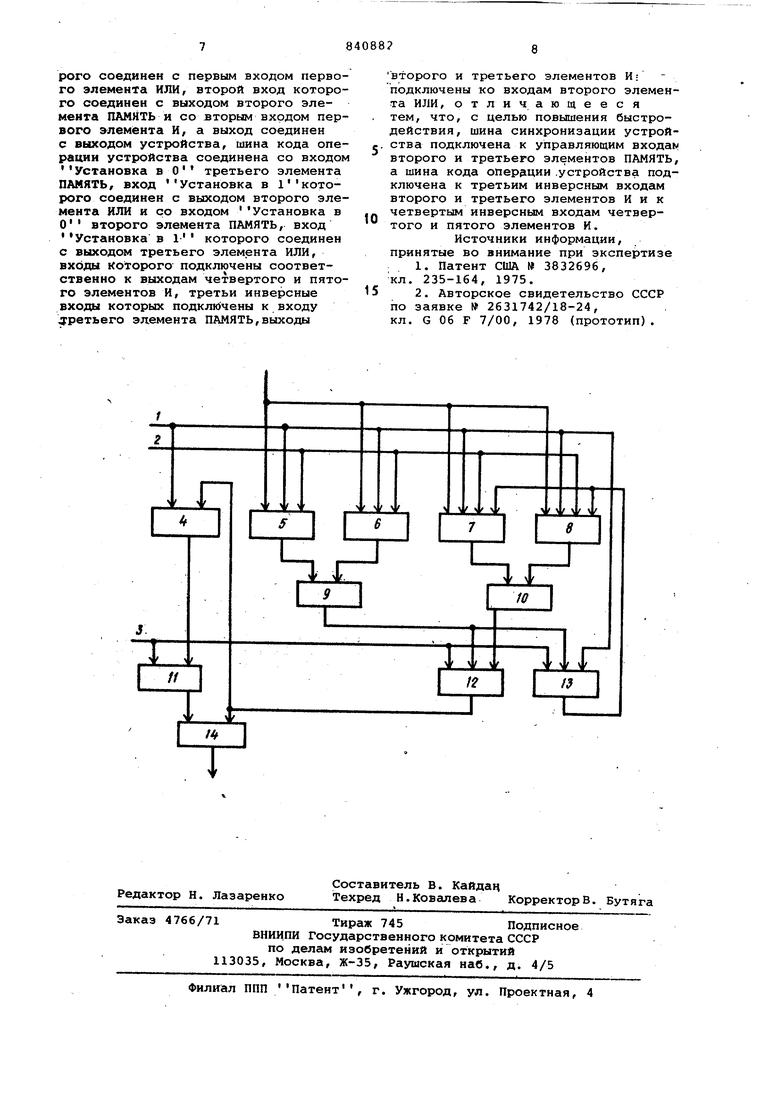

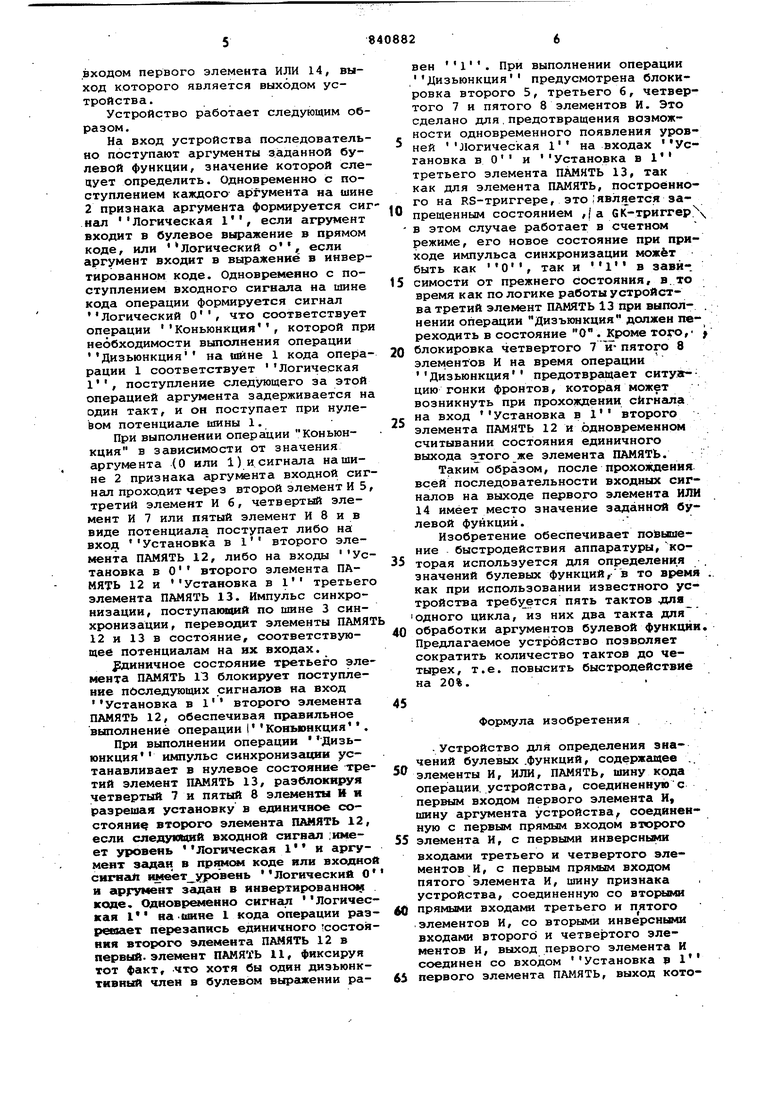

Выход второго элемента ИЛИ соединен с входом Установка в О второго элемента ПАМЯТЬ и с входом Ус5 тановка в 1 третьего элемента ПАМЯТЬ. Выход третьего элемента ПАМЯТЬ соединен с четвертыми запрещающими входами четвертого и пятого элементов И. Выход второго элемента соединен с первым входом первого элемента ИЛИ и со вторым входом первого элемента И. Зыход первого элемента И соединен с входом-Установка в 1 первого элемента ПАМЯТЬ Выход первого элемента ПАМЯТЬ соединен со вторым вхо дом первого элемента ИЛИ выход котброго является выходом устройства 2 Недостатком известного устройства является сложность сннхрониэации устройства, обусловленная тем, что сигнал на шине кода операции должен выставляться в промежутках между импульсако синхронизации. Следовательно, при практической регшиэации устройства необходимо фор шровать две синхронизирующие последовательности импульсов - одну для стробирования входных сигналов и CHiHeuiOB признака аргумента, другу дпя стробирования сигналов в коде on рации.. С точки зрения упрощения технической реализации (не нужно вводи- ь в устройство распределитель импульсов) целесообразно формировать одну синхронизирующую последовательность импульсов. Кроме того, это позволяет повысить быстродействие устройства, так как каждый аргумент булевой функ ции обрабатывается не за два такта, а за один. . .Цель изобретения - повьоиение быстродействия устройства. Поставленная цель достигается тем что в устройстве для .определения значений булевых фуикций, содержащем элементы И, ИЛИ, ПАМЯТЬ, шину кода операции устройства, которая соединена с первым входом первого элемента И, шину аргумента устройства, соединенную с первым прямым входом второго элемента И, с первыми инверсными входами третьего и четвертогбэлементов и, с первьвя прямым входом пятого элемента И, шину признака аргумента устройства, соединенную со вторыми прямыми входами треть и элементов и, со вторыми инверсНымя входами второго и четвер того элементов И, выход первого эле мента И соединен со входом Установка в 1 первого элемента ПАМЯТЬ, выход которого-соединен с йёрвым входом первого элемента , второй .вход которого соединен с выходом .второгоЭлемента ПАМЯТЬ и со вторым входом первого эламюнта И, а выход соединен с выходом устройства, шина кода операции устройства соединена с ходом Устаиовх% 19 О третьего фбифнта ПАМЯТЬ, эход Установка в 1 которого, соединен с выходом торого элемента ИЛИ и со входом Усновка в О второго элемента ПАМЯТЬ вход Установка в 1 которого соеДИН1ВЙ с выходом третьего элемента . ИЛИ, входы которого подключены соответственно к выходам четвертого и пятого элементов И, третьи инверсные входы которых подключены к входу третьего элемента ПАМЯТЬ, выходы второго и третьего элементов И подключены ко входам второго элемента ИЛИ, шина синхронизации устройства подключена к управляющим входам второго и третьего элементов ПАМЯТЬ, а Ц1на кода операции устройства подk)no4eHa к третьим инверсным входам второго и третьего элементов Ник четвертым инверсньв входам четвертого н пятого элементов И. На чертеже представлена схема предлагаемого устройства. Устройство содержит шину 1 кода операции, шину 2 признака аргумента, шину 3 синхронизации, первый элемент И 4, второй элемент И 5, третий элемент И б, четвертый элемент И 7, пятый элемент И -8, второй элемент ИЛИ 9, третий элемент ИЛИ 10, первый элемент ПАМЯТЬ 11, второй элемент ПАМЯТЬ 12, третий элемент ПАМЯТЬ 13, первый элемент ИЛИ 14. Вход аргумента устройства соединен с первыми прямыми входами второго 5н пятого 8 элементов И, а также с первыми инверсными входами третьего 6и четвертого 7 элементов И. Шина 1 кода операции соединена с первым входом первого элемента И 4, с третьими инверсными входами второго 5 и третьего 6, а также с четвертыми инверсными входами четвертого 7 и пятого 8 элементов И, а также с входсм Установка в О третьего элемента ПАМЯТЬ 13. Шина 2 признака аргумента соединена со вторыми.прямьми входами третьего 6 и пятого 8 элементов И, а также со вторьвш инверсньми входами второго 5 и четвертого 7 элементов И. Выходы второго 5 И третьего 6 элементов И соединены р входгили второго элемента ИЛИ 9,выход которого соединен с входом Установка в О второго элемента ПАМЯТЬ 12 и с входом Установка в 1 третьего элемента ПАМЯТЬ 13. Входы четвертого 7 и пятого 8 элементов И соединены с входсм Ус- . тановка в I второго элемента ПАМЯТЬ 12. Шина синхронизации 3 соединена с управляющими входами второхю 12 и третьего 13 элементов ПАМЯТЬ. Единичный выход третьего элемента ПАМЯТЬ 13 соединен с третьими инверсными входам четвертого 7 и пятого 8 элемен ов И. Единичный выход второго элемента ПАМЯТЬ 12 соединен со вторыми входгши первого элемента И 4 и первого элемента ИЛИ 14. Выход первого элемента И 4 соединен с входе Установка в 1 первого элемента ПАМЯТЬ 11 , единичный выход которого соединен с первым

входом первого элемента ИЛИ 14, выход которого является выходом устройства.

Устройство работает следующим образом.

На вход устройства последовательно поступают аргументы заданной булевой функции, значение которой слечует определить. Одновременно с поступлением каждого аргумента на шине 2 признака аргумента формируется сигнал Логическая 1, если агрумент входит в булевое выражение в прямом коде, или логический о , если аргумент входит в выражение в инвертированном коде. Одновременно с поступлением входного сигнала на шине кода операции формируется сигнал Логический О , что соответствует операции Конъюнкция, которой при необходимости выполнения операции Дизъюнкция на шине 1 кода операрации 1 соответствует Логическая 1, поступление следующего за этой операцией аргумента задерживается на один такт, и он поступает при нулеЬом потенциале шины 1.

При выполнении операции Конъюнкция в зависимости от значения аргумента (О или 1) и сигнала нашине 2 признака аргумента входной сигнал проходит через второй элемент И 5, третий элемент И 6, четвертьлй элемент И 7 или пятый элемент И В и в виде потенциала поступает либо на вход Установка в 1 второго элемента ПАМЯТЬ 12, либо на входы Установка в О второго элемента ПАМЯТЬ 12 и Установка в 1 третъего элемента ПАМЯТЬ 13. Импулъс синхронизации, поступакиций по шине 3 синхронизации , переводит элементы ПАМЯТ 12 и 13 в состояние, соответствующее потенциалам на их входах.

Единичное состояние третьего элемента ПАМЯТЬ 13 блокирует поступление последующих сигналов на вход Установка в 1 второго элемента ПАМЯТЬ 12, обеспечивая правильное выполнение операции IКовьюнкция .

При выполнении операции Дизъюнкция импульс синхронизации устанавливает в нулевое состояние третий элемент ПАМЯТЬ 13, разблокируя четвертый 7 и пять 8 элементы И и разрешая установку в единичное состояние второго элемента ПАМЯТЬ 12, если следуняций входной сигвгш .имеет уровень Логическая и аргумент задан в прямом коде или входной сигна11 11меет 5фовень Логический О и аргумент задан в инвертирован HOI коде. Одновременно сигнал Логическая нашине 1 кода операции раэpetoaer перезапись единичного состояния второго элемента ПАМЯТЬ 12 в первый, элемент ПАМЯТЬ 11, фиксируя тот факт, что хотя бы один дизъюнктивный член в булевом выражении ра. При выполнении операции

вен

.Дизъюнкция предусмотрена блокировка второго 5, третъего б, четвертого 7 и пятого 8 элементов И. Это сделано для,предотвращения возможности одновременного появления уровней Логическая 1 на входах Установка в О и Установка в 1 третъего элемента ПАМЯТЬ 13, так как для элемента ПАМЯТЬ, построенного на RS-триггере, это .является за0прещенным состоянием ,| а 6К-триггер. - в этом случае работает в счетном режиме, его новое состояние при приходе импулъса синхронизации может бытъ как О , так и 1 в завй-.

5 симости от прежнего состояния, в. то время как по логике работы устройства третий элемент ПАМЯТЬ 13 при выпол- . нении операции Дизъюнкция должен переходить в состояние О . Кроме того, j

0 блокировка четвертого 7 и- пятого 8 элементов И на время операции Дизъюнкция предотвращает ситуа-цию гонки фронтов, которая может возникнуть при прохождении ckгнaлa

на вход Установка в 1 второго

5

элемента ПАМЯТЬ 12 и одновременном считывании состояния единичного выхода же элемента ПАМЯТЬ. :

Таким образом, после прохождения всей последовательности входных сигналов на вьоходе первого элемента ИЛИ 14 имеет место значение заданной булевой функций.

Изобретение обеспечивает повышение быстродействия аппаратуры,ко5 торая исполъзуется для определения значений булевых функций,-в то время . как при исполъзованни известного устройства требу ется пять тактов -для Iодного цикла, из них два такта для

0 обработки аргументов булевой функции. Предлагаемое устройство позволяет сократить количество тактов до четырех, т.е. повысить быстродействие на 20%..

45

Формула изобретения

-Устройство для определения значений булевых .функций, содержащее ..

элементы И, ИЛИ, ПАМЯТЬ, шину кода операции, устройства, соединенную с первым входом первого элемента И шину аргумента устройства соединенную с первым прямым входом второго

элемента И, с первыми инверсными входами третъего и четвертого элементов И, с первым прямым входом пятого элемента И, шину признака устройства, соединенную со вторамя

прямыми входами третьего и пятого элементов И, со вторыми инверсными входами второго и четвертого элементов И, выход первого элемента И соединен со входом Установка в 1

первого элемента ПАМЯТЬ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента ПАМЯТЬ и со вторым входом первого элемента И, а выход соединен с выходом устройства, шина кода операции устройства соединена со входом Установка в О третьего элемента ПАМЯТЬ, вход Установка в 1 которого соединен с выходом второго элемента ИЛИ и со входом Установка в О второго элемента ПАМЯТЬ, вход Установка в 1 которого соединен с выходом третьего элемента ИЛИ, входы которого подключены соответственно к выходам четвертого и пятого элементов И, третьи инверсные входы которых подключены к входу третьего элемента ПАМЯТЬ,выходы

второго и третьего элементов Иг подключены ко входам второго элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия, шина синхронизации устройства подключена к управляющим входам второго и третьего элементов ПАМЯТЬ, а шина кода операции .устройства подключена к третьим инверсным входам второго и третьего элементов И и к четвертым инверсным входам четвертого и пятого элементов И.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3832696, кл. 235-164, 1975.

2.Авторское свидетельство СССР по заявке № 2631742/18-24,

кл. G 06 F 7/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения значенийбулЕВыХ фуНКций | 1978 |

|

SU807269A1 |

| Устройство для определения значений булевых функций | 1982 |

|

SU1037240A1 |

| Устройство для вычисления булевых функций | 1986 |

|

SU1372319A1 |

| Процессор программируемого контроллера | 1984 |

|

SU1269150A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для определения значений булевых функций | 1983 |

|

SU1151950A1 |

| Многофункциональный модуль | 1977 |

|

SU691845A1 |

| Программируемый многофункциональныйлОгичЕСКий МОдуль | 1979 |

|

SU851399A1 |

| Программируемый контроллер | 1986 |

|

SU1328815A1 |

| Устройство для определения значений булевых функций | 1990 |

|

SU1805462A1 |

гул

Г

Авторы

Даты

1981-06-23—Публикация

1979-06-07—Подача