(54) ЯЧЕЙКА ВЫЧИСДИТЕЛЬНСЙ СРЕДЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПО ПРОЦЕССОРАМ | 1991 |

|

RU2017206C1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1416978A1 |

. . -.:::

Изо етение относится к цифровым ей чиспитепьным машинам и преднаэначёко для построения структур, дискретных ройств управления на вычислнтепьнык О11 нородных средах.

Известна ячейка вычиснительной среци содержащая коммутационные aneNiieHTbt,, триконы и функциональный элемент F.. Этот эпемент выполняет лсйгическук 4УНК« цию стрелка Пирса и соединительпыё функции D , Р и О tl.

Недостатком ее является сложность, большое число настроечных и внфс1| ма11Я онных входов, резкое синжение бьтсТродеЦ- ствия автоматов, в котсфых ова йспользу-. ется с ростом их сложности, знаЧйтель ное число элементов, необходимое Д1Ш синтеза в среде аискретного устройсгоа.

Наиболее близким ло технической cym ности к предлагаемому является ячейка j вычислительной среды, содержащая авв триггера, элементы И, НЕ, дешифратс ы причем первая.группа входов первого де шифратора соединена соответственно с аыxcNSOMHtintrreiiDB, первый и второй в91:оШ)1 . второй групщ первого деши4 а1ч ра сЬот«ветс енао через и второй апемев- ftii НЕ соею11зе19 1 с первым я вторым, вхооамя ячейки первый и второй выходы пер- вого «шифрэтррА соедич ень1 с первым вхойом ячейки, а третий и четвертый вьи хсвМ nefUBord оешвфратора соедавевы со BTCHfMUM Екоосгм ячейки первая группа вхо Й(вт«1рого дешифратора являкугся втррым, третьям в четвертым входами ячейки. Bit)рая rpfima входе второго дешифратора нейосреоственяо и через первы э юмент НЕ соедияейа с первым входом ячейки, выходы Btoptuo дешифратора соеввяены соО:Тветственно со входами триггеров,

Второй вход ячейки,:кроме того, черва второй авемент НЕ соединен со входом второго дешифратора 2..

Недостатком ячейки является малое ц число выполняемых операций коммутаций;

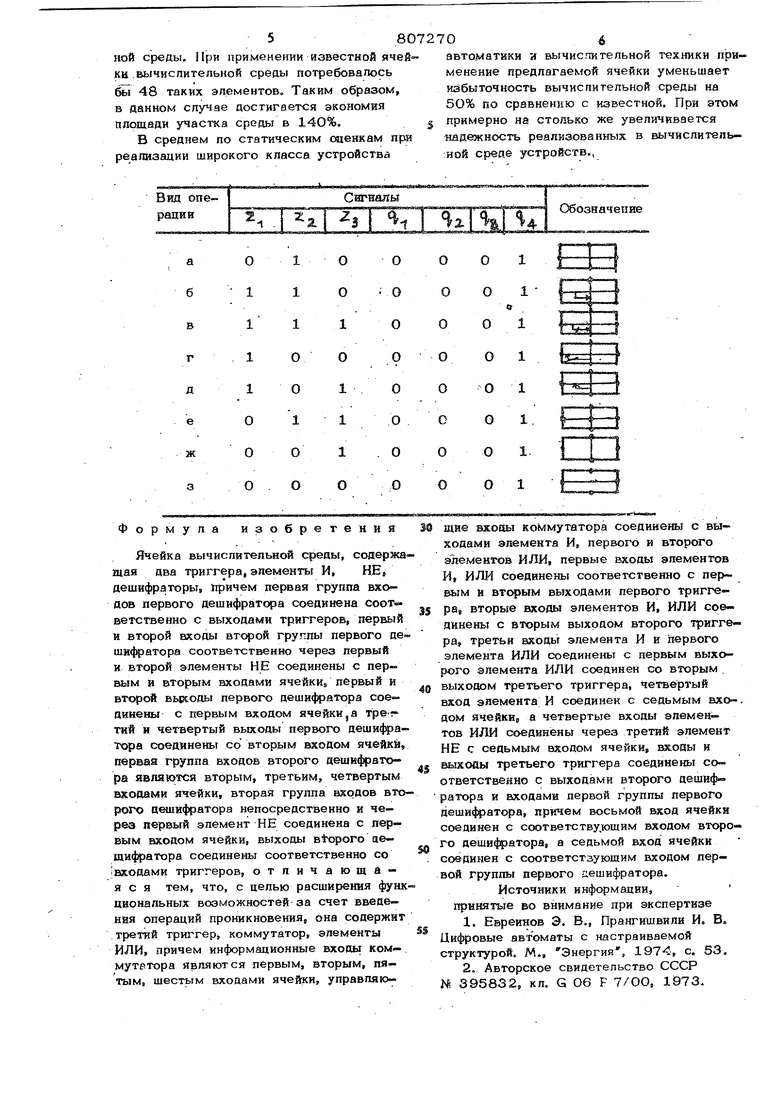

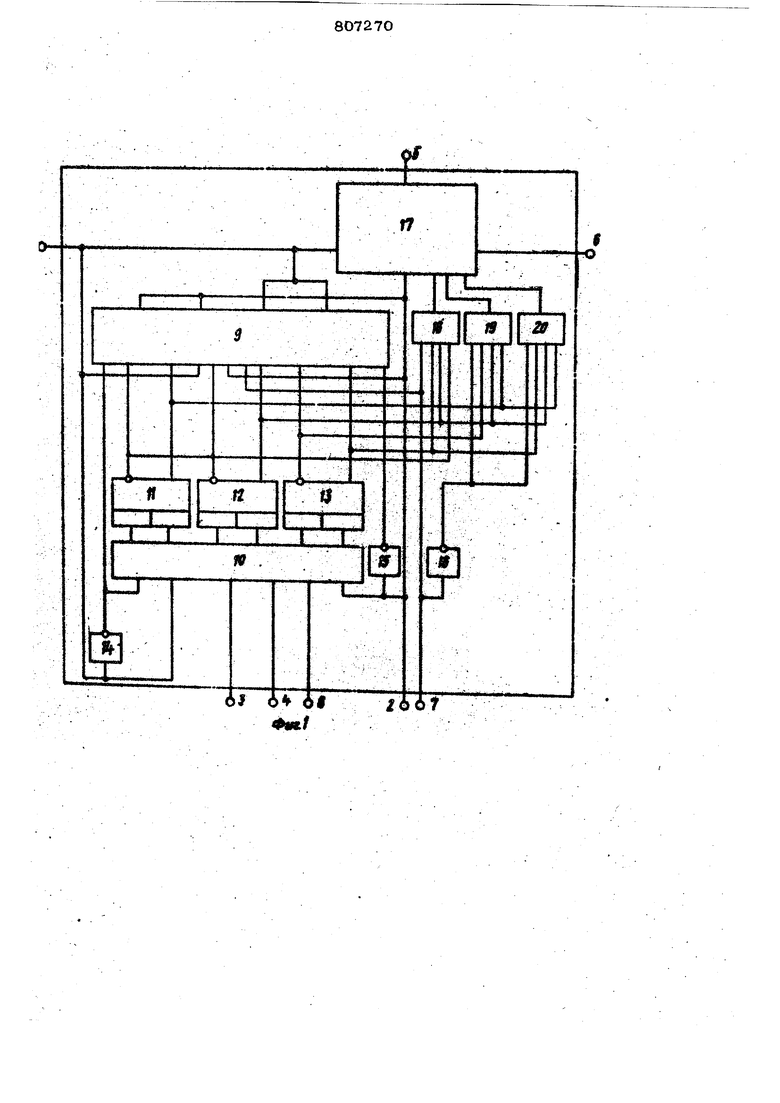

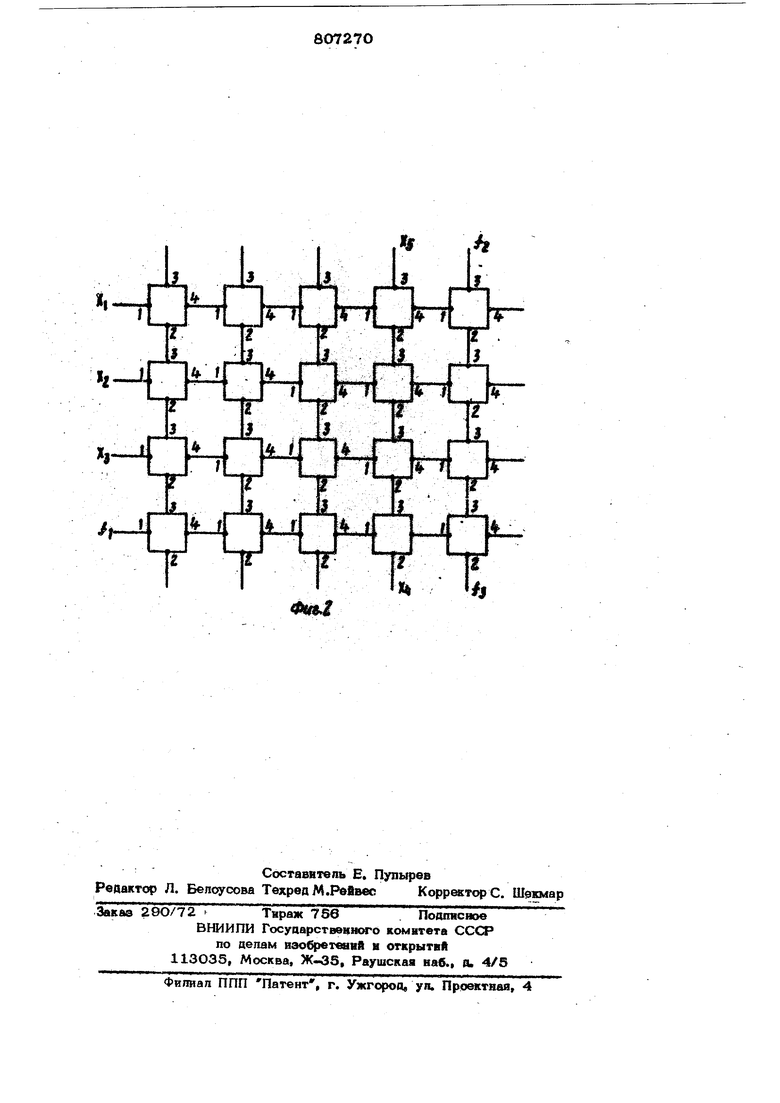

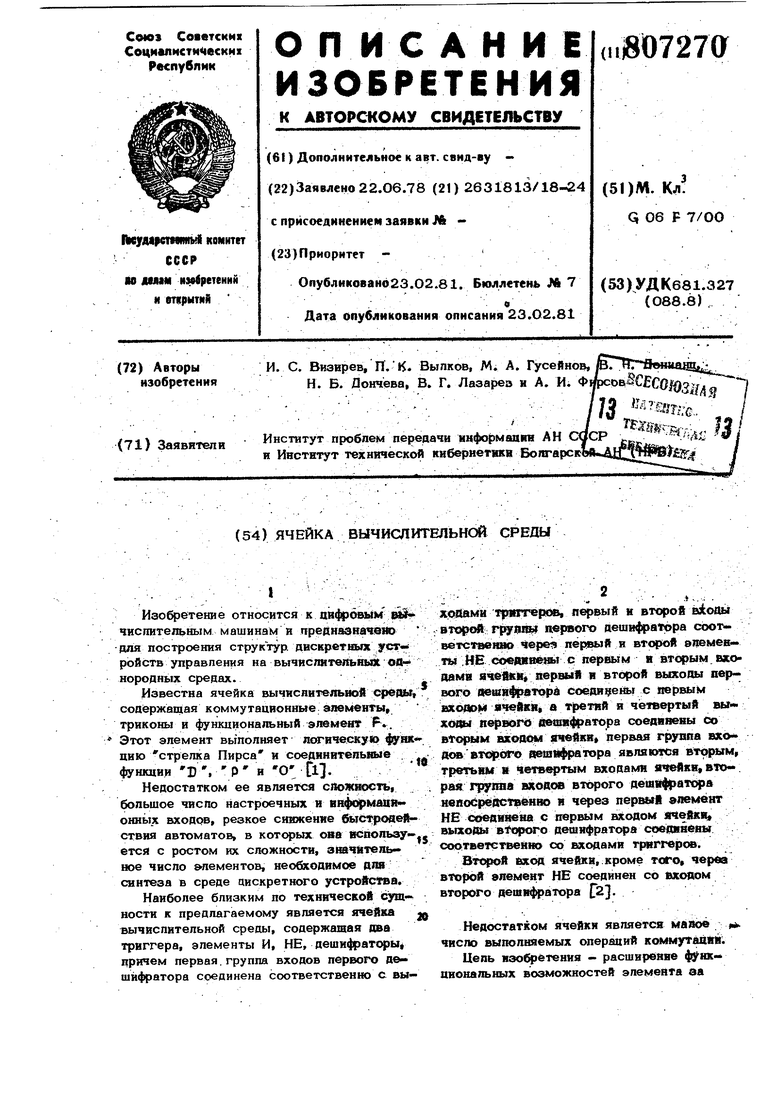

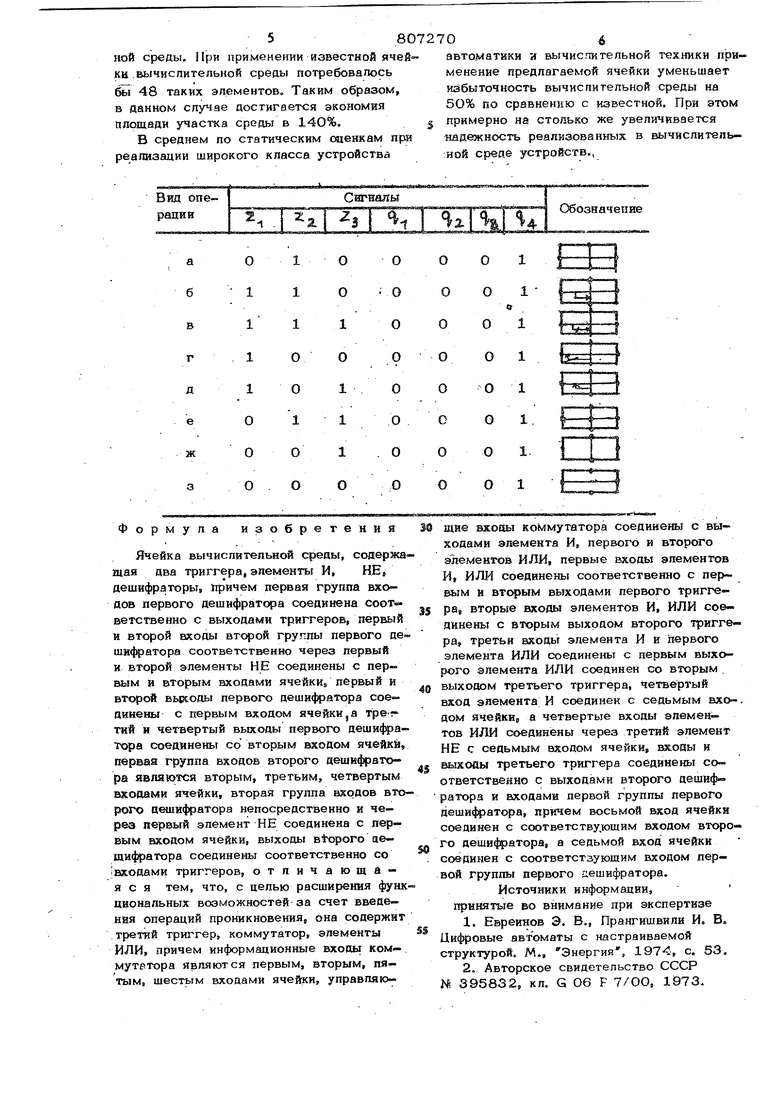

Цель изобретения - расширение фз икциональных возможностей элемента аа 380 счет введения дополнительных операций проникновения. Поставленная цель достиггается там, что ячейка содержит третий триггер, ком мутатор, элемшты ИЛИ, причем внформа- ционные входы коммутатора являются пер вым, вторым, пятым, шестым вводами ячейка, управляющие входы коммутатора соединены с выходами элемента И, перво го н второго элементов ИЛи, первые вхо ды эпементов И, ИЛИ соединены соответственно с первым и вторым выходами пер вого триггера, вторые входы эпементов .И, ИЛИ соединены с вторым выходом .второго триггера, третьи входы эпемента И и первого элемента ИЛИ соединены с первым выходом третьего триггера, а эретий вход второго эпемента ИЛИ соединен со вторым выходом третьего триггера, четвертый вход эпемента И соединен с седьмым входом ячейки, а четвертые входы элементов ИЛИ соединены через третий элемент НЕ с седьмым входом ячейки, входы и выходы третьего триггера соединены соответственно с выходами второго деши(|ратора и входами первой группы первого дешифратора, причем восьмой вход ячейки соединен с соответствующим входом второго дешифратора, а седьмой вход ячейки соединен с соответствую щим входом первой группы первого дешиф ратора. На фиг. 1 представлена ячейка; на фиг. 2 - матрица ячеек вычислительной среды. Ячейка содержит входы - 1-8, первый дешифратор 9, второй дешифратор 10 первый триггер-11, второй tpmrep 12, третий триггер 13, первый элемент НЕ 14 второй элемент НЕ 15, третий элемент ИВ 16, коммутатор 17, элемент И 18, второй элемент ИЛИ 19 и первый элемент ИЛИ 2О. Ячейка вычислительной среды имеет следующие режимы работы: Настройка (когда в среде синтезируется дискретное устройство); Обработка информации {режим функционирования син тезированного в среде устройства). При наличии управляющего сигнала нояь на входе 7 и управляющего сигна па единица на входе 2, ячейка переходит в режим работы Настройка. В первом такте настройки на вход 3 подается сигнал единица, а на входы 4 и 8 ноль. При этом триггер 11 устанавливается сигналом с входа 1. Во втором такте настройки на вход 4 подается сигнал единица, а на входы 3 и 8 -ноль При этом триггер 12 устанавпивается 0 сигналом с входа 1. В третьем такте настройки на вход 8 подаётся сигнал единица, а на вкоды 3 и 4 - ноль. При этом триггер 13 устанавливается сигна/ЮМ входа 1. При Наличии управлякяцего сигнала единица на входе 7 и сигнала ноль на входах 3, 4 и 8, ячейки переходит в режим работы Обработка информации. Сигналы о выходов триггеров 11, 12 и 13 управляют работой коммутатора 17, Помимо четырех операций, выполняемых известной ячейкой вычислительной среды, такая ячейка может настраиваться на вы- полнение четырех следующих дополнителыных операций: д - передача прямого сигнала от второго входа к первому входу| е - соединение первого,, второго, пятого и шестого входов; ж развязка между первым и шестым входами; 3 развязка между вторым и пятым входами., ;В таблице поясняется работа ячейки в режиме Обработка информации, где сим волы в крайнем левом стол& е обозначают вид операции, согласно описанию, 2,2,j.i2-3 сигналы На вторых выходах триггеров 11,- 12 и .13 соответственно, Ча 4-4- - сигналы на настроечных входах 3, 4, 8 и 7 соответственно. Введение в состав ячейки триггера, коммутатора, элементов И, НЕ и элементов ИЛИ существенно расширяет функциональные возможности элемента И, соответственно, повышает надежность вычис. . лительной среды и снижает ее избыточность. Для покапизации распространения ложных сигналов настраиваются на выпопмение операции ж и э соответственно со седние с неисправной ячейкой исправные ячейки вычислитепсьной среды. При реализации в Бычислитет ной среде микропрограммных автоматов, многовыходных ком«бинационных устройств и др. настройка соответствующих ячеек вычислительной « выполнение операции а, е, ж, приводит к уменьшению размеров среды. вычислительной среды в матричной однородной среды рассмотрим на примере реализации следующей системы булевых функций (фиг. 2), f. f.x X, с использованием 20 ячеек вычисли тальной среды. При применении известной ячей KU вычиспителькой среды потребовалось бы 48 таких элементов. Таким образом, в данном случае достигается экономия площади участка среды в 14О%,

В среднем по статическим оценкам при реализации широкого класса устройства ормула изобретения Ячейка вычислительной среды, содержа щая два триггера, элементь И, НЕ дешифраторы, причем первая группа входов первого дешифратс а соединена соот- ветственно с выходами триггеров, первый и второй входы второй группы первого де шифратора соответственно через первый и второй элементы НЕ соединены с первым и вторым входами ячейкИэ первый и второй вьрсоды первого дешифратора соединены с первым входом ячейки,а тре гтий и четвертый выходы первого дешифра тора соединень со вторым входом ячейки, первая группа входов второго дешифратора являются вторым, третьим, четвертым входами ячейки, вторая группа входов вто рого дешифратора непосредственно и через первый элемент НЕ соединена с первым входом ячейки, выходы второго ае шифратора соединены соответственно со входами триггеров, отличающаяся тем, что, с целью расширения функ циональных возможностей за счет введения операций проникновения, она содержит третий триггер, коммутатор, элементы Или, причем информационные входы коммутатора являются первым, вторым, пятым, шестым входами ячейки, управляю-

автол атики и вычислительной техники применение предлагаемой ячейки уменьшает избыточность вычислительной среды на 50% по сравнению с известной. При этом примерно на столько же увеличивается надежность реализованных в вычислитель- :ной среде устройств., щие входы коммутатора соединены с выходами элемента И, первого и второго элементов ИЛИ, первые входы элементов И, ИЛИ соединены соответственно с пер вым и вторым выходами первого триггеpaj вторые вкошл элементов И, ИЛИ соединены с вторым выходом второго триггера, третьи входы элемента И и первого элемента ИЛИ соединены с первым выхорого элемента ИЛИ соединен со вторым . выходом третьего триггера, четвертый вход элемента И соединен с седьмым вхо. дом ячейкив а четвертые входы эпемен- тов ИЛИ соединены через третий элемент НЕ с седьмым входом ячейки, шсоаы и выходы третьего триггера собдинены соответственно с выходами второго дешифратора и входами первой группы первого дешифратора, причем восьмой вход ячейки соединен с ctxiTBeTCTByjomHM входом второго аеши4)атора, а седьмой вход ячейки соединен с соответствующим входом первой группы первого дешифратора. Источники информации, принятые во внимание при экспертизе 1.Евреияов Э. В., Прангишвили И. В. Цифровые автоматы с настраиваемой структурой. М., Энергия, 197, с. S3. 2.Авторское свидетельство СССР М 395832, кл. G Об F 7/ОО, 1973.

Авторы

Даты

1981-02-23—Публикация

1978-06-22—Подача