Изобретение относится к вычислительной технике, в частности к устройствам сопряжения, и может быть использовано для программно-аппаратного вычисления булевых функций, зависящих от локальных дискретных сигналов.

Известно устройство, содержащее де- шифратор эдрееа. два элемента И, элемент ИЛИ, ш,инный; формирователь, регистр, групЬу элементов И, группу элементов

и-н|, j/i:;;;;:;r:;.... .- / Недостат.крм такого устройства является низкая производительность и большой обьем аппаратурных затрат.

Наиболее близким по технической сущности к предлагаемому является устройство,- содержащее дешифратор адреса, шинный формирователь, пять элементов И, два элемента ИЛИ, два триггера, оперативную память, генератор, счетчик, группу элементов И с тремя состояниями на выходе, группу элементов И-НЕ с тремя состояниями на выходе, причем вход дешифратора адреса подключен ко входу устройства для подключения шины адреса микроЭВМ, первый выход дешифратора адреса соединен с первыми входами второго и третьего Элементов И, выход второго элемента И соединен с входом выборки шинного формирователя, вход задания, направления передачи которого и первый вход элемента ИЛИ соединен с входом устройства для подключения выхода команды ввода микро- ЭВМ, выход элемента ИЛИ соединен с вторым входом второго элемента И, второй вход элемента ИЛИ и второй вход третьего элемента И соединены с входом устройства для подключения команды вывода микро- ЭВМ, вход/выход шинного формирователя соединен с входом-выходом устройства для подключения входа-выхода данных микро- ЭВМ, вторые входы К-ro (К 1, В) элемента И с тремя состояниями на выходе группы и К-го элемента И-НЕ стремя состояниями на выходе группы соединены с К-м разрядом входов для подключения дискретных сигналов, выходы К-го элемента И с тремя состояниями на выходе группы и К-го элемента И-НЕ с тремя состояниями на выходе группы соединены с К-м входом первого элемента И, нечетный выход оперативной памяти соединен с первым входом К-го элемента И с тремя состояниями на выходе группы, четный выход оперативной памяти соединен с первым входом К-го элемента И-НЕ с тремя состояниями на выходе группы, информационные входы оперативной памяти соединены с выходами шинного формирователя, вход управления записью оперативной памяти подключен к выходу третьего элемента

И, подключенному также к первому входу второго элемента ИЛИ, вход выборки оперативной памяти подключен к отрицательной шине источника пмтания и постоянно

активирован, адресные входы оперативной памяти подключены к информационным выходам счетчика, выход переполнения счетчика подключен к входу сброса первого триггера, второй выход дешифратора адреса подключен к первым входам четвертого и пятого элементов И, второй вход четвертого элемента И подключен к второму входу третьего элемента И, второй вход пятого элемента И подключен к первому входу пер5 вого элемента ИЛИ, а выход пятого элемента И подключен к входу установки первого триггера, выход которого подключен к входу управления генератора и к (В + 1)-му входу первого элемента И, выход генератора под0 ключей ко второму входу второго элемента ИЛИ, выход которого подключен к счетному входу счетчика, выход первого элемента И подключен ко входу установки второго триггера, выход четвертого элемента И подклю5 цен к входу сброса второго триггера, выход которого подключен к входу шинного формирователя.

Недостатком известного устройства является большой объем аппаратурных за0 трат. В связи с этим целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что в известное устройство для ввода в микро- ЭВМ дискретных сигналов.содержащее де5 шифратор адреса, шинный формирователь, счетчик, блок памяти констант, блок синхронизации, первые и второй RS-триггеры, группу элементов И стремя состояниями на выходе, группу элементов запрета с тремя

0 состояниями на выходе, с первого по пятый элементы И, первый и второй элементы ИЛИ, причем, адресный вход устройства соединен с входами дешифратора .адреса, первый выход которого соединен с первыми

5 входами первого и второго элементов И, второй выход дешифратора адреса соединен с первыми входами третьего и четвертого элементов И, выход последнего из которых соединен с входом установки в еди0 ницу первого RS-триггера, выход которого соединен с входом запуска блока синхронизации, первый выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом

5 счетчика, выход которого соединен с адресным входом блока памяти констант, вход разрешения записи которого соединен с вторым входом первого элемента ИЛИ и выходом второго элемента И, второй вход которого и второй вход третьего элемента И

соединены соответственно с первым входом второго элемента ИЛИ и входом задания режима вывода информации устройства, вход задания режима ввода информации которого соединен со вторыми входами второго элемента ИЛИ, четвертого элемента И и входом задания направления шинного формирователя, вход выбора которого соединен с выходом первого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, выход шинного формирователя соединен с информационным входом блока памяти констант, 1-й (, n; n - количество информационных разрядов) разряд информационного входа устройства соединен с первым входом 1-го элемента И с тремя состояниями на выходе группы и с инверсным входом 1-го элемента запрета с тремя состояниями на выходе группы; выход 1-го элемента И с тремя состояниями на выходе группы соединен с выходом 1-го элемента запрета с тремя состояниями на выходе группы и с f-м входом пятого элемента И, выход которого соединен со входом установки в единицу второго RS-триггера, вход установки в ноль которого соединен с выходом третьего элемента И, вход-выход шинного формирователя соединен с входом-выходом устройства, согласно изобретению введены группа элементов И, группа элементов запрета, две группы RS-триггеров, коммутатор, дешифратор, третий RS-триггер, с третьего по пятый элементы ИЛИ, шестой и седьмой элементы И, два элемента запрета и элемент задержки, выход которого соединен с входами установки в ноль RS- триггеров первой и второй групп, информационный вход шинного формирователя соединен с выходом коммутатора, управляющий вход которого соединен с выходом третьего RS-триггера, входы установки в ноль и единицу которого соединены с выходами соответственно шестого и седьмого элементов И, первые входы которых соеди-, нены с третьим выходом дешифратора адреса, младшие разряды выхода блока памяти констант соединены со входами третьего элемента ИЛИ и дешифратора, 1-й выход которого соединен с первым входом 1-го элемента И группы и первым информационным входом 1-го элемента запрета группы, выходы i-rc элемента И и 1-го элемента запрета соединены с входами установки в единицу 1-го RS-триггера соответственно первой и второй группы, выходы которых соединены соответственно с вторым входом элемента И с тремя состояниями на выходе группы и с прямым входом элемента запрета с тремя состояниями на

выходе группы, второй выход блока синхронизации соединен с первым прямым входом первого элемента запрета и с входом второго элемента запрета, выходы которых 5 соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен со входом элемента задержки и (п + 1)-м входом пятого элемента И, выход которого соединен с первым вхо- 10 дом пятого элемента ИЛИ, второй вход которого соединен с выходом второго элемента запрета, первый и второй инверсные входы которого соединены соответственно с инверсным входом и с вторым 5 прямым входом первого элемента запрета, вторые входы шестого и седьмого элементов И соединены соответственно с вторым и первым входами второго элемента ИЛИ, третий выход блока синхронизации соеди0 нен с вторыми входами элементов И группы и вторыми прямыми входами элементов запрета группы, инверсные входы элементов запрета которой соединены с третьими входами элементов И группы и выходом стар5 шего разряда блока памяти констант и вторым прямым входом первого элемента запрета, выход пятого элемента ИЛИ соединен с входом установки в ноль первого RS- , триггера, выход которого соединен с

0 первым разрядом информационных входов первой группы коммутатора, второй разряд информационных входов первой группы которого соединен с выходом второго RS-триггера, информационные входы второй

5 группы коммутатора соединены с информа- ционными входами устройства, выход третьего элемента И соединен с входом сброса счетчика, выход третьего элемента ИЛИ соединен с инверсным входом первого

0. элемента запрета.

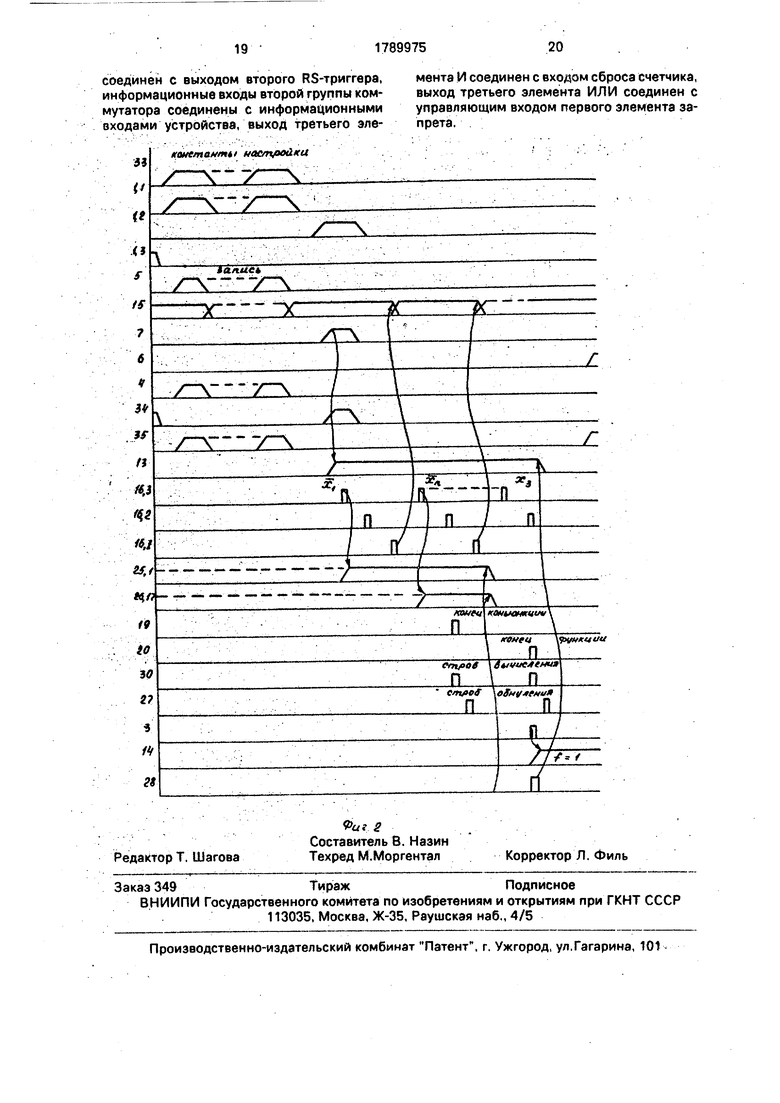

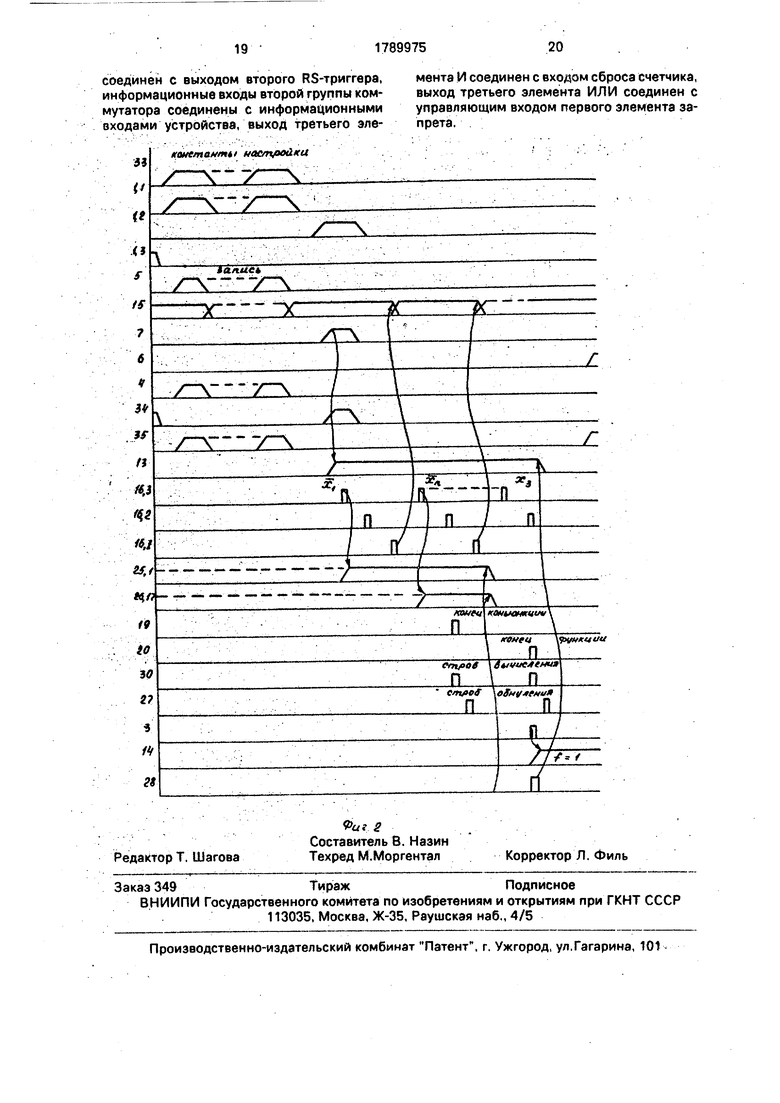

На фиг. 1 изображена функциональная схема предлагаемого устройства для ввода в микроЭВМ дискретных сигналов; на фиг. 2 - временная диаграмма работы устройст5 ва при настройке и при вычислении значения функции.

Устройство для ввода в микроЭВМ дискретных сигналов содержит дешифратор адреса 1, шинный формирователь 2, пять

0 элементов И 3-7, два элемента ИЛИ 8, 9, группу элементов И 10.1-10.В с тремя .состояниями на выходе, группу элементов запрета 11.1-11.В с тремя состояниями на выходе, блок памяти констант 12, два триг5 гера 13, 14, счетчик 15, блок 16 синхронизации, шестой - седьмой элементы И 17, 18, два элемента запрета 19, 20, группу элементов И.21.1-21.В, группу элементов запрета 22.1-22,В, второй дешифратор 23, коммута- тор 24, первую группу триггеров 25,1-25,В,

вторую группу триггеров 26.1-26.В, элемент задержки 27, третий, четвертый и пятый элементы ИЛИ 28, 29, 30, третий триггер 31, входы адреса 32, входы-выходы данных 33, входы управления 34, 35, информационные входы 36.

Дешифратор 1 предназначен для дешифрации адреса, выставленного на входах адреса 32 устройства.

Дешифратор 1 может быть реализован, например, на стандартных интегральных микросхемах 155ИДЗ.

Шинный формирователь 2 предназначен для усиления по мощности сигналов на входах-выходах 33 устройства при активации первого входа разрешения (входа выборки), а также для перевода своего входа-выхода в состояние высокого импеданса при неактивизации первого входа разрешения отключения информационных входов-выходов 33 устройства. Режим работы шинного формирователя 2 определяется уровнем сигнала на втором входе разрешения (входе направления передачи).

Шинный формирователь 2 может быть реализован, например, на стандартной интегральной микросхеме 589АП16.

Элемент ИЗ предназначен для формирования значения коньюнктивного терма по значению выходов каждой пары элементов 10-11. Причем, когда выходы обоих элементов в паре находятся в высокоимпедансном состоянии, это воспринимается К-м входом (К Т, В).элемента ИЗ как в ТТЛ логике - логической.

Элемент И4 предназначен для управления первым входом разрешения (выходом выборки) шинного формирователя 2. Выход элемента И4 возбуждается, если активиро- ваны выход 1.1 дешифратора 1 и выход элемента ИЛИ8.

Элемент И5 предназначен для управления входом записи блока памяти констант 12 и элементом ИЛИ9 в том случае, если активирован выход 1.1 дешифратора 1 и вход 35 устройства.

Элемент И6 предназначен для управления входом сброса триггера 14 в том случае, если активирован выход 1.2 дешифратора 1 и вход 35 устройства.

Элемент И7 предназначен для управления входом установки триггера 13 в том случае, если активирован выход 1.2 дешифратора 1 и вход 34 устройства.

Элемент ИЛИ8 предназначен для управления элементом И4 в том случае, если активированы входы 34 и 35 устройства.

Элемент ИЛИ9 предназначен для управления счетным входом счетчика 15 сигналами либо с выхода 16.1 блока 16, либо с выхода элемента И5.

Группа элементов И с тремя состояниями на выходе без инверсии 10,1-Ю.В предназначены для идентификации прямого значения К-й переменной в коньюнктивном терме. При атом активизирован вход управления К-го из элементов 10.1-10.В. В противном случае, выход элемента находится в высокоимпедансном состоянии и не влияет на работу К-го из элементов 11,1-11.В.

Группа элементов И с тремя состояниями на выходе 10.1-10.В может быть реализована, например, на стандартных интегральных микросхемах 589АГИ6, причем информационный вход сопоставляется с двумя входами элемента И, объединенных вместе и изображен на фиг, 1 как единственный D-вход.

Группа элементов запрета с тремя состояниями на выходе 11.1-11.В предназначены для идентификации инверсного значения К-й переменной в коньюнктивном терме, При этом активизирован вход управления К-го из элементов 11.1-11.В. В противном случае, выход элемента находится в высокоимпедансном состоянии и не влияет на работу К-го из элементов 10.1-10.В.

Группа элементов запрета с тремя состояниями на выходе 11.1-11.В может быть реализована, например, на стандартных интегральных микросхемах 571ХЛ2, причем информационный вход сопоставляется с двумя входами элемента И, объединенных вместе и изображен на фиг. 1 как единственный вход.

Блок памяти констант 12 предназначен для записи, хранения и выдачи кодов настройки,

Болк памяти констант 12 может быть реализован, например, на стандартных интегральных микросхемах 541РУ2.

Триггер 1.3 предназначен для управления блоком 16, Триггер 13 устанавливается сигналом с выхода элемента И7, а обнуляется сигналом с элемента ИЛЙ28.

Триггер 13 может быть реализован, например, на стандартной интегральной микросхеме. 155ТМ2.

Триггер 14 предназначен для фиксации единичного значения вычисленной булевой функции от переменных входного сигнала 36 при активизации выхода элемента ИЗ.

Триггер 14 обнуляется при активизации выхода элемента И6,

Триггер 14 может быть реализован, например, на стандартных интегральных элементах 155ТМ2.

Счетчик 15 предназначен для адресации оперативной памяти 12 при записи или

считывании информации. Счетный вход счетчика 8 управляется выходом элемента ИЛИ9.

Счетчик 15 может быть реализован, например, на стандартных интегральных микросхемах 155ИЕ7.

Блок 16 предназначен для управления по счетному входу счетчиком 15 при считывании информации из блока памяти констант 12. (через элемент ИЛИ9) - импульсами по выходу 16.1; управления элементами И 19, и запрета 20 - импульсами по выходу 16,2 управления первой и второй группами элементов И 21 и запрета 22 - импульсами по выходу 16.3.

Блок 16 может быть реализован, например, на стандартной интегральной микросхеме 155ЛАЗ; резисторе, конденсаторе и элементах задержки.

Шестой элемент И 17 предназначен для обнуления третьего триггера 31 в том случае, если возбуждается выход 1.3 дешифратора 1 и вход 34 (внешняя микроЭВМ обращается к устройству по адресу, возбуждающему выход 1.3 дешифратора 1 в режиме ввода информации, однако фактически данные не вводятся, так как шинный формирователь 2 в этом случае отключён от шины данных 33).

Седьмой элемент И 18 предназначен для установки третьего триггера 31 в том случае, если возбуждается выход 1.3 дешифратора 1 и вход 35 устройства (внешняя мик- роЭВМ обращается к устройству по адресу, возбуждающему выход 1.3 дешифратора 1 в режиме вывода, однако фактически данные не выводятся, так как шинный формирователь 2 отключен от шины данных).

Элемент запрета 19 предназначен для формирования признака окончания констант коньюнкции в том случае, если неак- тивирован выход элемента ИЛИ 29, активирован отдельный выход 12.2 блока памяти констант 12 и имеется импульс на выходе 16.2 блока 16.

Элемент запрета 20 предназначен для формирования признака окончания всех констант всех коньюнкции (конец констант функции) в том случае, если неактивирован выход элемента ИЛИ 29, неактивирован отдельный выход 12.2 оперативной памяти 12 и имеется импульс ма выходе 16.2 блока 16 синхронизации.

Первая группа элементов И 21.1-21.В предназначена для управления входами установки соответствующего триггера первой группы триггеров 25.1-25.В при активиро- вании соответствующего из выходов 23.1- 23.В дешифратора 23, при активировании отдельного выхода 12.2 блока памяти констант 12 и при наличии импульса на выходе 16.1 блока 16.

Вторая группа элементов запрета 22.122.В предназначена для управления входа5 ми установки соответствующего из

триггеров второй группы триггеров 26.126.В при активировании соответствующего

из выходов 23.1-23.В дешифратора 23 при

неактивировании отдельного выхода 12.2

10 блока памяти 12 и при наличии импульса на

выходе 16.3 блока 16.

Первая и вторая группа элементов И 21 и запрета 22 обеспечивает последовательную развертку константы настройки групп 15 элементов И 10 и запрета 11с тремя состояниями на выходе, которая записывается и хранится в группах триггеров 25, 26.

Первая группа триггеров 25.1-25.В предназначена для установки и хранения 0 сигнала управления соответствующими элементами И группы, 10.1-10.В с тремя состояниями на выходе (в том случае, если в коньюнкцию входят соответствующие по номеру переменная без инверсии). 5 Вторая группа триггеров 26.1-26.В предназначена для установки и хранения сигнала управления соответствующими элементами запрета группы 11.1-11.В с тремя состояниями на выходе (в том случае, если в 0 коньюнкцию входят соответствующие по номеру переменные с инверсией). Первая и вторая группы триггеров могут быть реализованы, например, на стандартных интегральных микросхемах 155ТМ2, 5 Элемент задержки 27 предназначен для временного сдвига импульса на выходе элемента ИЛИ 30, который имитирует вычисление значения коньюнкции элементом ИЗ с целью последующего (после вычисления) 0. обнуления триггеров групп 25, 26 и подготовки их к очередной развертке констант.

Третий элемент ИЛИ 28 предназначен

для обнуления триггера 13 импульсом либо

с выхода элемента ИЗ (вычисленная коньюн5 кция 1), либо с выхода элемента запрета

20 (конец всех констант).

Четвертый элемент ИЛИ 29 предназначен для определения факта наличия констант, кодирующих данную коньюнкцию 0 ИЛИ (И) всех констант функции. Такому факту соответствует нулевая константа (нулевое состояние выходов 12,1 выходов блока памяти 12), т.е. если факт (признак) имеет место, то на выходе элемента ИЛИ 29 - 5 логический ноль.

Пятый элемент ИЛИ 30 предназначен для формирования импульса вычисления (строба вычисления) при наличии таковых либо на выходе элемента И 19, либо на выходе элемента запрета 20, т.е. по окончанию

развертки константы коньюнкции, в том числе и последней.

Третий триггер 31 предназначен для управления мультиплексором 24. Он устанавливается импульсом с выхода элемента И 18 и обнуляется импульсом с выхода элемента И 17.

Третий триггер 31 может быть реализован, например, на стандартной интегральной микросхеме 155ТМ2.

Второй дешифратор 23 предназначен для дешифрации информации на выходах 12.2 блока памяти 12 и управления группами элементов И 21.1-21.В, запрета 22.1-22.В с целью определения номера су- щественной переменной и формирования в дальнейшем развернутой константы.

Коммутатор 24 предназначен для подключения ко входам шинного формирователя 2 либо информационных входов 36 - вторая группа входов (триггер 31 установлен), либо выходов триггеров 13,14 (триггер 31 обнулен)- первая группа входов.

Коммутатор 24 представляет собой совокупность мультиплексора типа 155КП1, у которых все одноименные адресные входы объединены между собой, а одноименные бходы различных мультиплексоров подключены к различным разрядам кодовой шины (входы DI), а входы Do соединены в соответ- ствии с линиями связи на фиг. 1. Однако, более экономично групповой мультиплексор 24 может быть реализован, например, на мультиплексорах типа.

Входы адреса 32 предназначены для подключения шины адреса внешней микро- ЭВМ. ..:

Входы-выходы данных 33 предназначены для подключения шины данных внешней микроЭВМ.

Первый вход управления 34 (Чтение) предназначен для подключения сигнала вывода информации внешней микроЭВМ.

Второй вход управления 35 (Запись) предназначен для подключения сигнала ввода информации внешней микроЭВМ.

Информационные входы 36 предназначены для подключения дискретных сигналов.

Устройство для ввода в микроЭВМ дис- кретных сигналов работает следующим образом.

Настройка.

При этом внешняя микроЭВМ, подключенная к устройству ко входам адреса 32, входам-выходам данных 33, входам управления 34 (Чтение), 35 (Запись), обращается к нему как к порту вывода с фиксированным адресом. Активируется вход управления 35 (Запись), на входах 32

выставляется адрес/ активирующий выход

1.1 дешифратора 1, активируется выход элемента ИЛИ8. Поэтому активируется выход элемента И4, подключающий шинный формирователь 2 по первому входу управления (Е1) к входам-выходам 33, а так как второй вход управления (Е2) неактивирован, то шинный формирователь 2 подключается в режиме ввода с входов-выходов 33, информация с которых передается на входы данных блока памяти 12, Блок памяти 12 имеет постоянно-активизированный вход управления, поэтому активированный выход элемента И5 переводит ее в режим записи по входу записи. Счетчик 15 обнулен в исходном положении по цепям сброса/не указанным на фиг. 1, поэтому на входах адреса оперативной памяти 12 выставлен адрес нулевой ячейки (см. фиг. 1, 2). В. блок памяти

12 записывается первое слово информации с выходов блока 2. По заднему фронту сигнала на выходе элемента И5 (и соответственно по заднему фронту сигнала на выходе элемента ИЛИ9) изменяется состояние счетчика 15 и его выходные сигналы адресуют ячейку блока памяти 12.

При очередном обращении к устройству и активировании входа 20 аналогично запишется второе слово информации. Далее устройство работает аналогично. Далее внешняя микроЭВМ обнуляет счетчик 15, причем на входах адреса 32 устанавливается код; возбуждающий выход 1.2 дешифратора 1 и активируется вход 35. Поэтому сигнал с выхода элемента И6 обнуляет счетчик 15 и триггер 14 Для ввода информации с локальной обработкой внешняя микро- ЭВМ обнуляет также триггер 31, при этом выставляется адрес (на входах 32), активирующий выход 1,3 дешифратора 1 и возбуждается вход 34, что приводит к возбуждению выхода элемента И17 и обнулению триггера 31, т.е. на выходы коммутатора 24 подключается информация его первой группы входов, подключенной к выходам триггеров 13, 14.

Устройство готово к локальной обработке сигналов на информационных входах 36.

Режим поэлементной развертки констант вычисляемых коньюнкции.

Режим инициируется внешней микро- ЭВМ, которая обращается к устройству по адресу, активирующему выход 1.2 дешифратора 1. кроме того возбуждается вход управления 35, в связи с чем активируется выход элемента И7 (фиг. 1, 2). Поэтому устанавливается триггер 13, выход которого запускает блок 16, который начинает формировать три перекрывающиеся последовательности импульсов на выходах 16.1, 16.2, 16.3. На выходе 12.1 блока памяти 12 установлен код и значение первой переменной первой конь- юнкции (нулевая ячейка, счетчик 15 обнулен по цепям, не указанным на фиг. 1). На выходе второго дешифратора 23 установлен уни- тзрный код первой переменной (т.е. активирован соответствующий ее номеру выход дешифратора 23), на отдельном выходе 12.2 блока памяти 12 установлено значение этой переменной (1 - прямое значение, О - инверсное значение). На фиг. 1 указано, что номер первой переменной первой конь- юнкции 1 и по первому импульсу 1 б устанавливается (по входу 5) триггер 25.1 через соответствующий элемент 21.1 группы 21 (прямое значение переменной Xi), Первый импульс на выходе 16.2 блока 16 проверяет признаки окончания констант коньюнкций или (и) всех констант функции на элементах запрета 19, 20. Признаком окончания констант коньюнкций является нулевое состояние выходов 12.1 блока памяти 12 и единичные выходы 12.2, признаком окончания констант функции является нулевое состояние выходов 12.1 блока памяти 12 и нулевое состояние выхода 12.2. Если выходы элементов запрета 19, 20 не возбуждаются (признаков нет), то не формируется строб вычисления на вход элемента ИЗ и строб обнуления групп триггеров 25, 26. Первый импульс на выходе 16.1 блока 16 через элемент ИЛИ9 обеспечивает изменение состояния счетчика 15, выход которого адресует теперь очередную (первую) ячейку блока памяти 12, информация из которой устанавливается на выходах 12.1, 12.2. Вновь происходит дешифрация второй по счету переменной первой коньюнкций (очевидно, это порядок развертки констант переменных не имеет значения). Второй импульс на выходе 16.3 блока 16 вновь стро- бирует входы групп 21, 22 элементов И и запрета, соответственно. На фиг. 2 показана установка триггеЈа 26. В (инверсное значение переменной Хв). Второй импульс на выходе 16.2 на фиг. 2 возбуждает выход элемента И19 - т.е. наблюдается конец первой коньюнкций (первая коньюнкция XiXs). Импульс с выхода элемента запрета 19 через элемент ИЛИЗО стробирует элемент ИЗ, который определяет значение первой коньюнкций на наборе сигналов, установленных на входах 36. Вычисления производятся аналогично прототипу: входы управления (Е) групп 10.1-10.В, 11.1-11.8 возбуждают соответствующие триггеры групп 25.1-25.В, 26.1-26.В, причём триггеры устанавливаются последовательно при развертке констант (на фиг. 1 показана установка двух триггеров 25.1, 26.В - коньюнкция ХтХв. Первый

разряд входов 36, допустим, равен единице, поэтому логическая единица устанавливается на выходе элемента 10.1 (он открыт, т.е. возбужден его вход Е, вход Е элемента 11.1 5 неактивирован, поэтому его выход находится в высокоимпедансном состоянии и не влияет на передачу информации, с выхода элемента 10.1). Последний разряд входов 36, допустим, равен нулю (на выходе эле- 10 мента 11.В - логическая единица - у него инверсный вход данных, выход элемента 10. В в высоко.импедансном состоянии. Остальные разряды выходов 36 могут быть любыми, т.к. остальные триггеры групп 25, 26 15 обнулены и, соответственно, выходы остальных элементов групп 10,11 находятся в высокоимпедансном состоянии, что воспринимается соответствующими входами элемента ИЗ как в ТТЛ-логике - логической

0 единицей. Таким образом, в описанном случае на всех входах элемента ИЗ установлены логические единицы, поэтому по стробу на выходе элемента ИЛИЗО возбуждается выход ИЗ. Поэтому устанавливается триггер

5 14, фиксируя, что функция равна единице. На фиг, 1 показан случай установки триггера 14 по признаку окончания функции - т.е. по импульсу на выходе элемента запрета 20. Этот же импульс через элемент ИЛИ28

0 обеспечивает обнуление триггера 13, который обнуляется выходом элемента ИЗ (на фиг. 2 оба этих импульса появляются на входах элемента ИЛИ28 одновременно, если же это условие не соблюдается в реаль5 ном устройстве, то второй импульс - с выхода элемента ИЗ подтверждает обнуленное состояние триггера 13). Выход триггера 13 останавливает блок 16, который не успевает сформировать импульс на выходе 16.1,

0 поэтому после определения единичного значения функции счетчик 15 продолжает адресовать последнюю выбранную ячейку памяти 12 (с признаком окончания функции) до своего обнуления. Обнуление устройства

5 производится выходом элемента И6, когда возбуждаются выход 1.2 дешифратора 1 и вход управления 35 (внешняя микроЭВМ обращается к устройству как к порту вывода с адресом, возбуждающим выход 1.2 де0 шифратора 1), Такое обнуление производится после ввода значения функции в микроЭВМ. При этом триггер 31 обнулен и . через коммутатор 24 к шинному формирователю 2 подключены выходы триггеров 13,14

5 (остальные, недействительные входы подключены к отрицательному полюсу источника питания). Внешняя микроЭВМ, проведя . имитацию вычислений функции (установка триггера 13), вводит информацию с выходов триггеров 13, 14. При этом возбуждается

выход 1.1 дешифратора 1, вход 34, выход И4, входы Е1, Е2 шинного формирователя 2, что настраивает его на передачу информации со входов на входы-выходы данных 33, МикроЭВМ анализирует состояние выходов триггеров 13,14, выделяет состояние выхода триггера 13 и, когда он обнулится (вычисления закончены), анализирует состояние триггера 14, которое равно значению функции; Для функций, зависящих от малого числа коньюнкций и при высокой частоте импульсов блока 16 вычисления могут закончиться в промежутке между командой индикации результатов счета и командой ввода состояния триггеров 13,14. При необходимости ввода информации со входов 36 без локальной их обработки (или части разрядов входов 36) внешняя микроЭВМ обращается к устройству по адресу, воэбуж- дающему выход 1.3 дешифратора 1, при этом возбуждается также вход управления 35. Поэтому активируется выход элемента Й18 и устанавливается триггер 31, что приводит к тому, что на выход мультиплексора подключается информация с второй группы входов. Эта информация затем через шинный формирователь 2 по входам-выходам 33 передается в микроЭВМ в случае ее обращения к устройству по адресу, возбуждающему выход 1.1 дешифратора 1. Выход элемента ИЛИ8 возбуждает второй вход элемента И4, а его выход в свою очередь активирует вход Б1 шинного формирователя 2. вход Е2 которого возбуждается активированным входом 34. Шинный формирователь 2 находится в режиме передачи информации на входы-выходы данных 33.

Для обнуления триггера 31 внешняя микроЭВМ обращается к устройству по адресу, возбуждающему выход 1.3. при этом активируется и вход 34 (внешней микро- ЭВМ). Поэтому возбуждается выход элемента И17 и триггер 31 обнуляется, что приводит к подключению на выходы коммутатора 24 выхода триггера 14.

Таким образом, режим поэлементной развертки констант вычисляемых коньюнк- цйй характеризуется последовательной настройкой групп элементов И 10.1-10.В и запрета 11.1-1-1.В с тремя состояниями на выходе, что пбзволйет экономно использовать блок памяти 12.

Кодирование констант производится следующим образом.

В поле номера переменной (соответствует выходам 12.1 блока памяти 12) записывается двоичный номер переменной К , В, где В - разрядность информационных входов 35. Причем разрядность выходов 12,1 intlogaB + 1, где Int - ближайшее большее, чем logaB целое число.

В поле значения переменной (соответ-. ствуёт отдельному выходу 12.1 блока памяти 12) записывается О, если переменная входит в данную коньюнкцию с инверсией, и Г, если переменная входит в данную коньюнкцию без инверсии.

Нулевой код на выходах 12.1 ( в поле номера переменной) означает конец констант данной коньюнкции или (и) всех констант. Если в поле номера переменной нули, а в поле значения переменной единицы, это означает конец констант данной коньюнкции. Если в поле номера переменной и в поле значения переменной нули, это означает конец всех констант (конец функции).

Рассмотрим пример конкретного выполнения..-,.:.. Реализовать функцию

fXl - Х2 XI X V Х2 V Хз V Х4 V Х5 V Хб V Х7

Определим величину потребной разрядности выходов 12.1 оперативной памяти 12 lntlog2B + 1 - 4.

Сформируем массив констант для пер- вой коньюнкции:

12.1 12.2

переменная Xt переменная Xs конец коньюнкции 1

коиыонкция Ха конец коньюнкции 2

коньюнкция Хз конец коньюнкции 3

коньюнкция Хд конец коньюнкции 4

коньюнкция Xs конец коньюнкции 5

коньюнкция Хв конец коньюнкции б

0111 0000

О коньюнкция X

О . конец коньюнкции 7

55

Итак, необходимо 15-5-75 бит. В прототипе требуется 8 -2 -7 - 112 бит.

Формула изобретения Устройство для ввода в микроЭВМ дискретных сигналов, содержащее дешифратор адреса, шинный формирователь, счетчик, блок памяти констант, блок синхронизации, первый и второй RS-триггеры, группу элементов И с тремя состояниями на выходе, группу элементов запрета с тремя состояниями на выходе, с первого по пятый элементы И, первый и второй элементы ИЛИ, причем адресный вход устройства соединен с входами дешифратора адреса, первый выход которого соединен с первыми входами первого и второго элементов И, второй выход дешифратора адреса соединен с первыми входами третьего и четвертого элементов И, выход последнего из которых соединен с входом установки в единицу первого RS-триггерз, выход которого соединен с входом запуска блока синхронизации, первый выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен со счетным входом счетчика,, выход которого соединен с адресным входом блока памяти констант, вход разрешения записи которого соединен с вторым входом первого элемента ИЛИ и выходом второго элемента И, второй вход которого и второй вход третьего элемента И соединены с первым входом второго элемента ИЛИ и входом задания режима вывода информации, вход задания режима ввода информации соединен с вторыми входами второго элемента ИЛИ, четвертого элемента И и входом задания направления шинного формирователя, вход выборки которого соединен с выходом первого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, выход шинного формирователя соединен с информационным входом блока памяти констант 1-й (I 1, n; n - количество информационных разрядов) разряд информационного входа соединен с первым входом 1-го элемента И с тремя состояниями на выходе группы и с управляющим входом 1-го элемента запрета с тремя состоя- ниями на выходе группы, выход 1-го элемента И с тремя состояниями на выходе группы соединен с выходом 1-го элемента запрета с тремя состояниями на выходе группы и с 1-м входом пятого элемента И, выход которого соединен с входом установки в 1 второго RS-триггера, вход установки в О которого соединен с выходом третьего элемента И, вход-выход шинного формирователя соединен с входом выходом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит группу элементов И, группу элементов запрета, две группы RS-триггеров, коммутатор, дешифратор, третий RS- триггер, с третьего по пятый элементы ИЛИ шестой и седьмой элементы И, два элемента запрета и элемент задержки, выход которого соединен с входами установки в О RS- триггеров первой и второй групп, вход шинного формирователя соединен с выходом коммутатора, управляющий вход которого соединен с выходом третьего RS-триггера, входы установки в О и 1 которого соединены с выходами соответственно шестого и седьмого элементов И, первые входы которых соединены с третьим выходом дешифратора адреса, выходы младших разрядов блока памяти констант соединен с входами третьего элемента ИЛИ и дешифратора, 1-й выход которого соединен с первым входом 1-го элемента И группы и первым информационным входом 1-го элемента запрета группы, выходы которых соединены с входами установки в Т 1-го RS-триггера соответственно первой и второй групп, выходы которых соединены соответственно с вторым входом элемента И с тремя состояниями на выходе группы и информационным входом элемента запрета с тремя состояниями на выходе группы, второй выход блока синхронизации соединен с первым информационным входом первого элемента запрета и информационным входом второго элемента запрета, выходы которых соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен с входом элемента задержки и (п + 1)-м входом пятого элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом второго элемента запрета, первый и второй управляющие входы которого соединены соответственно с управляющим входом и вторым информационным входом первого элемента запрета, вторые входы шестого и седьмого элементов И соединены соответственно с вторым и первым входами второго элемента ИЛИ, третий выход блока синхронизации соединен с вторыми входами элементов И группы и вторыми информационными входами элементов запрета группы, управляющие входы элементов запрета которой соединены с третьими входами элементов И группы и выходом старшего разряда блока памяти констант и вторым информационным входом первого элемента запрета, выход пятого элемента ИЛИ соединен с входом установки в О первого RS-триггера, выход которого соединен с первым разрядом информационных входов первой группы коммутатора, второй разряд информационных входов первой группы которого

соединен с выходом второго RS-триггера, информационные входы второй группы коммутатора соединены с информационными входами устройства, выход третьего элемента И соединен с входом сброса счетчика, выход третьего элемента ИЛИ соединен с управляющим входом первого элемента запрета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1786482A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1751772A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Устройство для ввода-вывода дискретных сигналов микроЭВМ | 1989 |

|

SU1681306A1 |

Изобретение относится к вычислительной технике, в частности к устройствам сопряжения, и может быть использовано для программно-аппаратного вычисления булевых функций, зависящих от локальных дискретных сигналов. Цель изобретения - сокращение аппаратурных затрат. Устройство содержит дешифратор 1 адреса, шинный формирователь 2, элементы 3... 7 И, элементы 8, 9 ИЛИ, группу элементов 10 И с тремя состояниями на выходе, группу элементов 11 И-НЕ с тремя состояниями на выходе, блок памяти констант 12, триггеры 13, 14, счетчик 15, блок синхронизации 16, элементы 17 .... 18 И, элементы запрета 19, 20, группу элементов 21 И, группу элементов запрета 22. дешифратор 23, коммутатор 24, группы триггеров 25, 26, элемент задержки 27, элементы 28, 29, 30 ИЛИ, триггер 31, входы 32 адреса, входы-выходы данных 33, входы 34,35 управления и информационные входы 36. 2 ил.

| Авторское свидетельство СССР Mr 13143145, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1987 |

|

SU1503043A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1990-04-11—Подача