(54) ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный генератор | 1983 |

|

SU1120363A1 |

| Функциональный генератор | 1980 |

|

SU926679A1 |

| Функциональный генератор | 1983 |

|

SU1120308A1 |

| Функциональный генератор | 1983 |

|

SU1120364A1 |

| Функциональный генератор | 1985 |

|

SU1262533A1 |

| Устройство для воспроизведения функций | 1985 |

|

SU1273955A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

| Функциональный преобразователь | 1979 |

|

SU830430A1 |

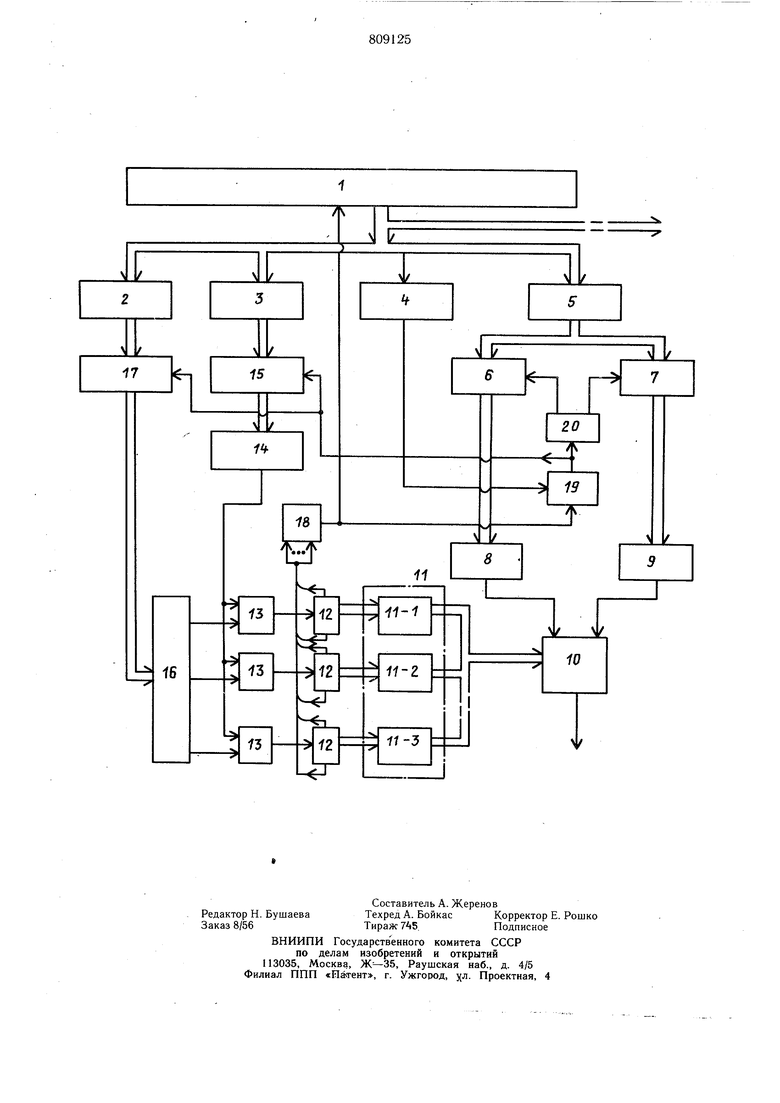

Изобретение относится к вычислительной технике и может найти применение как программно-задающее устройство при автоматизации процессов испытания на прочность и выносливость объектов авиационной техники в акустических реверберационных камерах. Известен цифровой функциональный синтезатор, содержащий формирователи серий импульсов, регистры режима и амплитуды, сумматоры серий импульсов, цифровые сглаживающие фильтры, реверсивные счетчики и выходные цифровые преобразователи 11. Принцип построения такого цифрового функционального синтезатора состоит в ТОМ , что его выходной сигнал образуется посредством накопления на реверсивном счетчике импулъсов, вырабатываемых остальной частью устройства, которая последовательно формирует ряд серий импульсов разной частоты. Темп изменения выходного сигнала зависит от частоты импульсов в данной серии. В зависимости от того, какие последовательности серий импульсов выбирает блок выборки серий импульсов в качестве аппроксимирующей функции, может быть выбрана либо линейная, либо синусоидальная функция. Для реализации синусоидальной функции вырабатывается шесть серий импульсов со строгим соотношением частот. Недостатки указанного функционального синтезатора состоят в том, что ограничен набор аппроксимирующих функций, а расширение этого набора связано с аппаратурными затратами, кроме того, ограничен верхний частотный предел воспроизводимых функций ввиду необходимости разбиения сложной функции на большое число аппроксимирующих участков, практический верхний частотный предел генерации функции не превышает 50 Гц. Таким образом, рассмотренный синтезатор не решает задачу воспроизведения высокочастотных сложных функций, необходимых для проведения акустических прочтостей испытаний. , Наиболее близким по технической сущности к предлагаемому является функциональный генератор, содержащий постоянное запоминающее устройство, три циф|юаналоговых преобразователя, два регистра ординат (начальной и конечной точек аппроксимации), два счетчика, два элемента задержки и генератор 2. Этот генератор работает так. Два цифроаналоговых преобразователя (ЦАП) задают на входы третьего два аналоговых сигнала, соответствующих ординатам начала и конца воспроизводимого участка аппроксимации. Третий ЦАП на своем аналоговом выходе за постоянный промежуток времени (задаваемый генератором через посредство счетчика, подключенного к цифровому входу третьего ЦАП) изменяет сигнал от начальной до конечной точки каждого участка аппроксимации. В результате осуществляется ступенчато-линейная аппроксимация требуемой функции. Обмен межд,у запоминающим устройством и регистрами ординат происходит в конце каждого участка аппроксимации Недостаток данного генератора - постоянство длительности и формы участков аппроксимации. Это сужает класс воспроизводимых функций как по сложности, так и по быстродействию. , Цель изобретения - повыщение быстродействия. Поставленная цель достигается тем, что в функциональный генератор, содержащий управляющий процессор, выход которого соединен с информационными входами трех буферных регистров и входом регистра цикла, выходы первого и второго буферных регистров соединены соответственно с входами регистра формы участков и регистра длительности участков, выход которого подключен к входу делителя частоты, выход третьего буферного регистра соединен с входами первого и второго регистров амплитуды, выходы которых соединены соответственно с входами первого и второго цифроаналоговых преобразователей, выходы которых соединены соответственно с первым и вторым входами третьего цифроаналогового преобразователя, выход которого является выходом генератора, выход регистра цикла соединен с первым входом переключателя циклической работы, выход которого соединен с управляющими входами регистров формы участков и длительности участков и с входом переключателя режимов, выходы которого подключены соответственно к управляющим входам перв,ого и второго регистров амплитуды, внедены элементы И, элемент ИЛИ, реверсивные сдвиговые регистры, дещифратор и запоминающее устройство, выход которого подключен к третьему входу третьего цифроаналогового преобразователя, адресные входы запоминающего устройства соединены соответственно с информационными выходами реверсивных сдвиговых регистров, управляющие выходы которых через элемент ИЛИ подключены к входу управляющего процессора и к второму входу переключателя циклической работы, первый вход каждого элемента И соединен с соответствующим выходом дещифратора, второй вход подключен к выходу делителя частоты, выход каждого элемента И соединен с входом соответствующего реверсивного сдвигового регистра, вход дещифратора соединен с выходом регистра формы участков. На чертеже дана схема предлагаемого функционального генератора. Генератор содержит управляющий процессор 1, буферные регистры 2 и 3, регистр 4 цикла, буферный регистр 5, регистры 6 и 7 амплитуды, цйфроаналоговые преобразователи 8-10, запоминающее устройство 11, содержащее отдельные области 11 - 1, 11-2, И-3, реверсивные сдвиговые регистры 12, элементы И 13, делитель 14 частоты, регистр 15 длительности участков, дещифратор 16, регистр 17 формы участков, элемент ИЛИ 18, переключатель 19 циклической работы, переключатель 20 режимов. Предлагаемый функциональный генератор работает следующим образом. На подготовительном этапе процессор 1 обнуляет регистры 2, 3, 4, 5, 6, 7, 15 и 17, затем засылает в регистр 2 код формы первого участка аппроксимации, в регистр 3 - код длительности первого участка аппроксимации, в регистр 5 - код ординаты конечной точки первого участка аппроксимации. Регистры 6, 7, 15 и 17 остаются обнуленными. Таким образом, на выходах всех трех цифроаналоговых преобразователей, а следовательно, и лащото канала (при наличии нескольких каналов в функциональном генераторе) находятся нулевые потенциалы. По команде «пуск информация с буферных регистров 2, 3 и 5 переписывается на соответствующие регистры 17, 15 и 7, в результате чего на дешифратор 16 приходит код формы участка аппроксимации, на делитель 14 частоты - код длительности участка аппроксимации (частоты следования импульсов), цифроаналоговый преобразователь 9 на своем выходе устанавливает потенциал конечной точки первого участка аппроксимации. В соответствии с кодом формы участка аппроксимации активизируется один из выходов дешифратора 16 и через соответствующий элемент И 13 соединяет выход делителя 14 с соответствующим реверсивным сдвиговым регистром 12, т.е. происходит выбор той области запоминающего устройства И, в которой последовательно записаны коды, обеспечивающие требуемую форму аппроксимации. Необходимые коды в различных комбинациях, соответствующих различным законам аппроксимации, записываются предварительно от процессора 1 во все области

запоминающего устройства 11. Каждая область обеспечивает свой закон аппроксимации. В качестве запоминающего устройства 1 принципиально может быть использован любой из трех видов памяти (оперативная, полупостоянная или постоянная).

После прохождения команды «пуск запускается делитель 14. Приходящие от него импульсы сдвигают выбранный реверсивный сдвиговый регистр 12, который последовательно с частотой, заданной генератором, обеспечивает передачу информации из выбранной области запоминающего устройства 11 на вход цифроаналогового преобразователя 10. В результате этого на выходе цифроаналогового преобразовате ля 10 в соответствии с выбранной формой аппроксимации будет изменяться аналоговый сигнал от нуля до величины, соответствующей ординате конечной точки первого участка задаваемой цифроаналоговым преобразователем 9. По достижении последнего разряда сдвигового регистра вырабатывается сигнал на реверс, который одновременно служит сигналом окончания генерации первого участка. Число ступеней, аппроксимирующих отрезок функции, определяется разрядностью реверсивного сдвигового регистра, которая соответствует числу кодов, записанных в одной области запоминающего устройства 11. Если функция периодическая, о чем свидетельствует сигнал, приходящий с регистра 4, то переключателем 19 обеспечивается запрет смены информации на всех рабочих регистрах, что приводит к повторению первого (любого) участка программы, но в обратном направлении (реверс регистра) от ординаты конечной точки к. ординате начальной. По достижении другого крайнего разряда регистра вырабатывается сигнал на прямой ход, и цикл продолжается дальще. Процессор 1 подсчитывает сигналы о количестве выполненных участков и по Достижении требуемого числа снимает команду «цикл. Отсутствие команды «цикл при наличии сигналов о достижении крайних разрядов сдвигового регистра приводит к обмену информацией между буферными регистрами, на которые процессор 1 предварительно уже записал информацию о новом участке аппроксимации, и остальными регистрами. Поступивщая новая информация проходит по всем каналам аналогично уже приведенному описанию. Следует отметить, что с буферного регистра 5 ордината конечной точки каждого последуюцХего участка аппроксимации поочередно записывается то на регистр 6, то 7, что при реверсивном характере выбора кодов из запоминающего устройства 11 обеспечивает «сшивание аппроксимирующих участков.

Быстродействие функционального генератора при воспроизведении сложных функций увеличается за счет сокращения числа обменов между процессором и аппаратурной частью генератора в результате принципиального расщирения набора форм аппроксимирующих функций.

Формула изобретения

Функциональный генератор, содержащий управляющий процессор, выход которого соединен с информационными входами трех буферных регистров и входом регистра цикла, выходы первого и второго буферных регистров соединены соответственно с входами регистра формы участков и регистра длительности участков, выход которого подключен к входу делителя частоты, выход третьего буферного регистра соединен с входами первого и второго регистров амплитуды, выходы которых соединены соответственно с входами первого и второго цифроаналоговых преобразователей, выходы которых соединены соответственно с первым и вторым входами третьего цифроаналогового преобразователя, выход которого является выходом генератора, выход регистра цикла соединен . с первым входом переключателя циклической работы, выход которого соединен с управляющими входами регистров формы участков и длительности участков и с входом переключателя режимов, выходы которого подключены соответственно к управляющим входам первого и второго регистров амплитуды, отличающийся тем, что, с целью повыщения быстродействия, в него введены элементы И, элемент ИЛИ, реверсивные сдвиговые регистры, дещифратор и запоминающее устройство, выход которого подключен к третьему входу третьего цифроаналогового преобразователя, адресные входы запоминающего устройства соединены соответственно с информационными выходами реверсивных сдвиговых регистров, управляющие выходы которых через элемент ИЛИ подключены к входу управляющего процессора и к второму входу переключателя циклической работы, первый вход каждого элемента И соединен с соответствующим выходом дещифратора, второй вход подключен к выходу делителя частоты, выход каждого элемента И соединен с входом соответствующего реверсивного сдвигового регистра, вход дещифратора соединен с выходом регистра формы участков.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-02-28—Публикация

1979-03-05—Подача