(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1985 |

|

SU1249523A2 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| Устройство для сопряжения электронных вычислительных машин | 1981 |

|

SU1013938A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1987 |

|

SU1501077A1 |

1

Изобретение относится к вычислительной технике и может быть исполъзовано при объединении в вычислительную систему двух разнотипных ЭВМ через интерфейсы ввода-вывода, в частности, интерфейс общая шина (ОШ) и интерфейс типа магистрали.

Известны устройства для сопряжения основной и вспомогательных цифровых вычислительных машин, содержащие блоки прерывания, блоки режима обмена, блоки согласования, блоки управления, регистры приема и выдачи слова 1.

Недостатками устройства являются недостаточное .быстродействие и ограниченная область применения из-за невозможности объединения в вычислительную систему двух разнотипных ЭВМ:ЭВМ с общей щиной (ОШ) и ЭВМ с сопряжением 2К.

Наиболее близким к предлагаемому техническому решению является устройство для сопряжения периферийной системы с электронной вычислительной машиной, содержащее дешифратор, регистр управления, блок выполнения прерывания, блок обмена, коммутатор, переключатель блока усиления, первый из которых соединен с общей шиной ЭВМ, второй - с общей шиной периферийной системы, первый, второй, третий и четвертый вы.ходы первого блока усиления соединены соответственно с первыми вхолтами дешифратора, коммутатора, регистра управления и блока выполнения прерывания, первый, второй и третий входы первого блока усиления соединены соответственно с первыми выходами дешифратора, регистра управления и блока выполнения прерывания, второй и третий входы дешифратора соединены соответственно с первыми

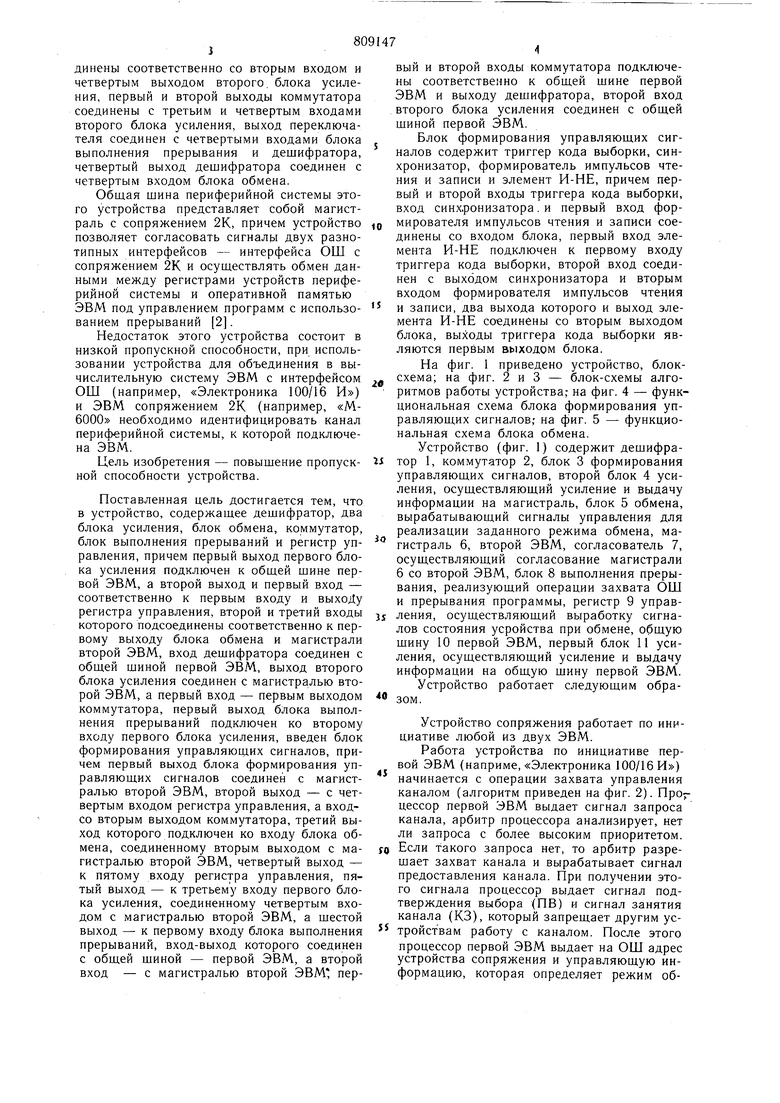

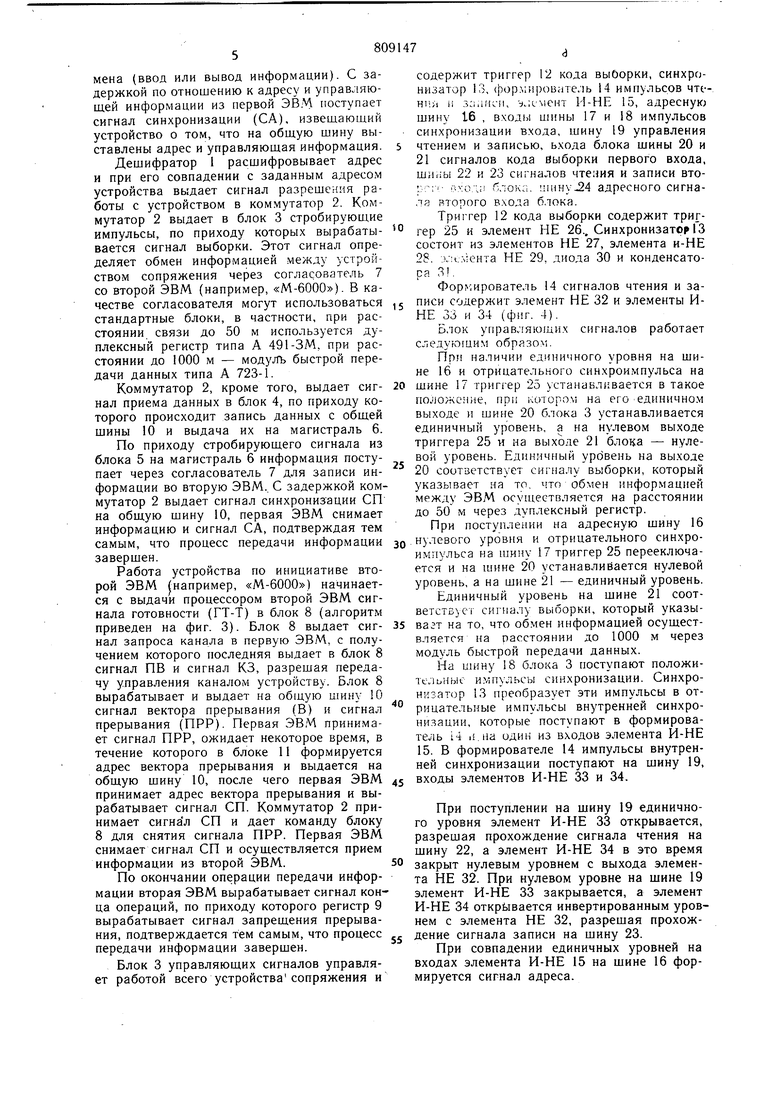

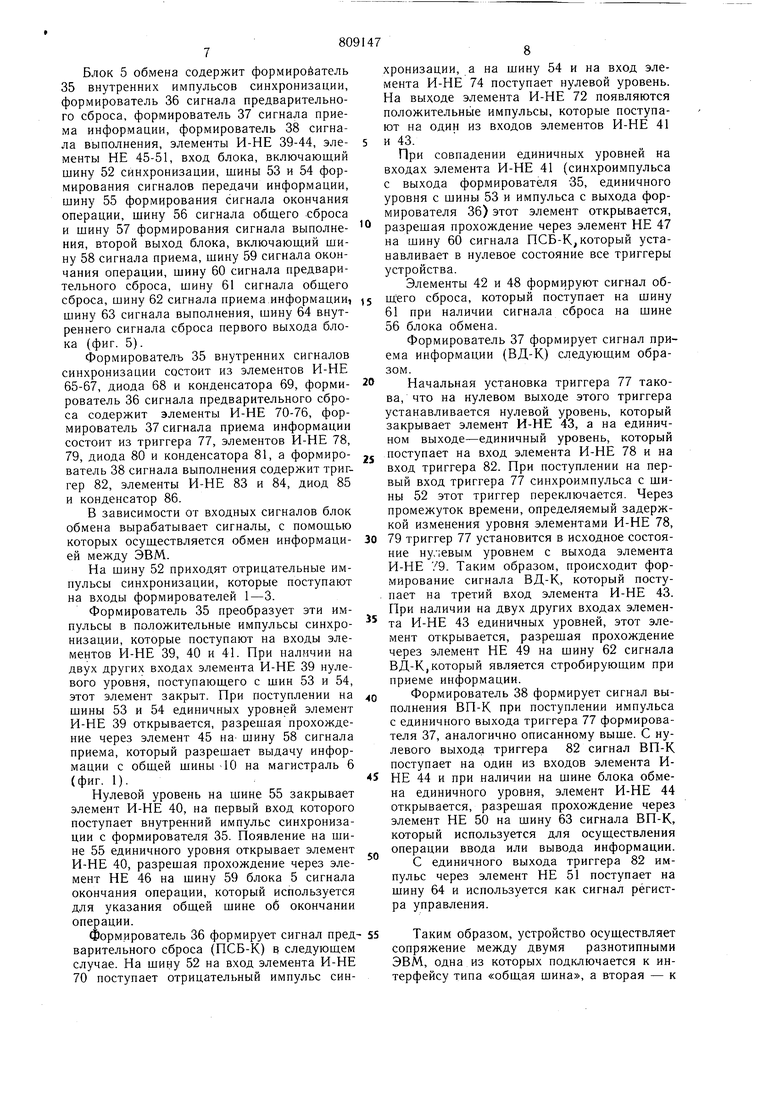

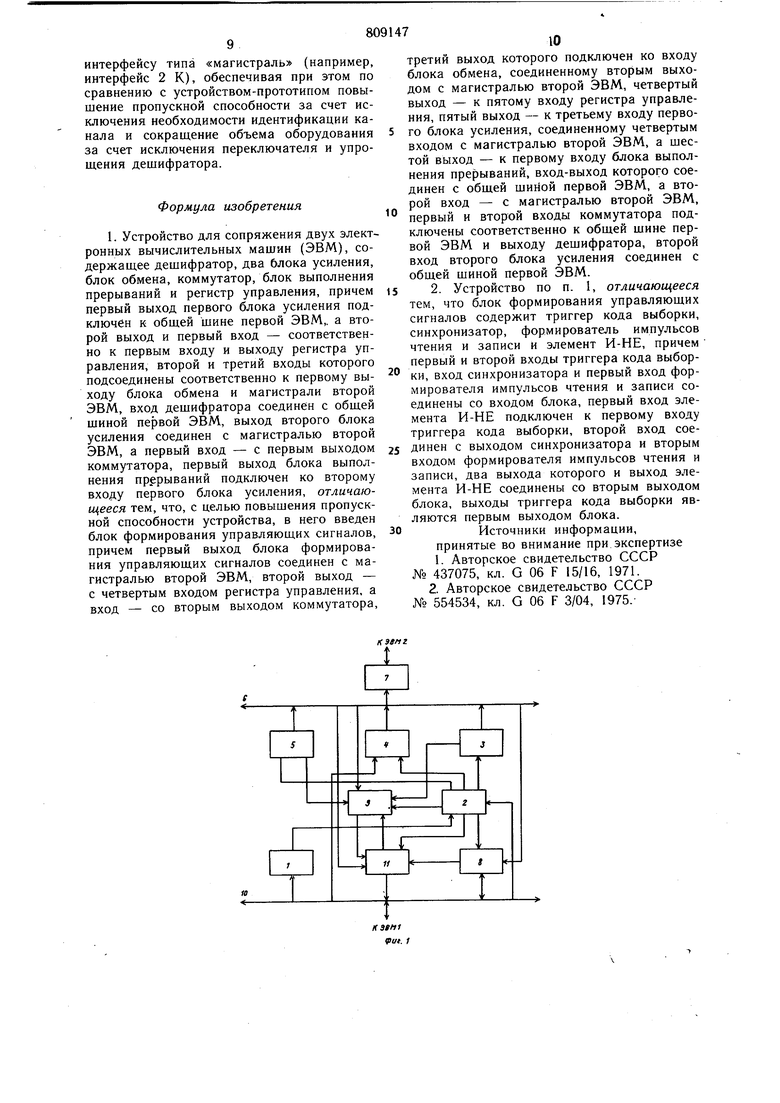

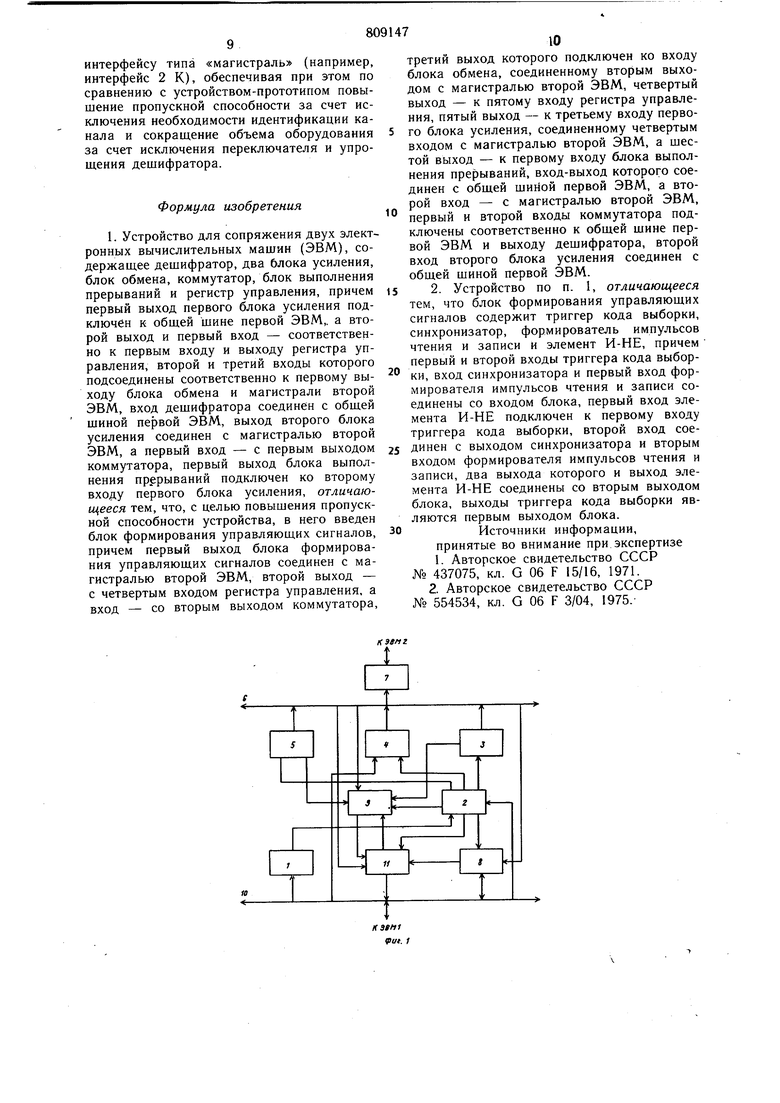

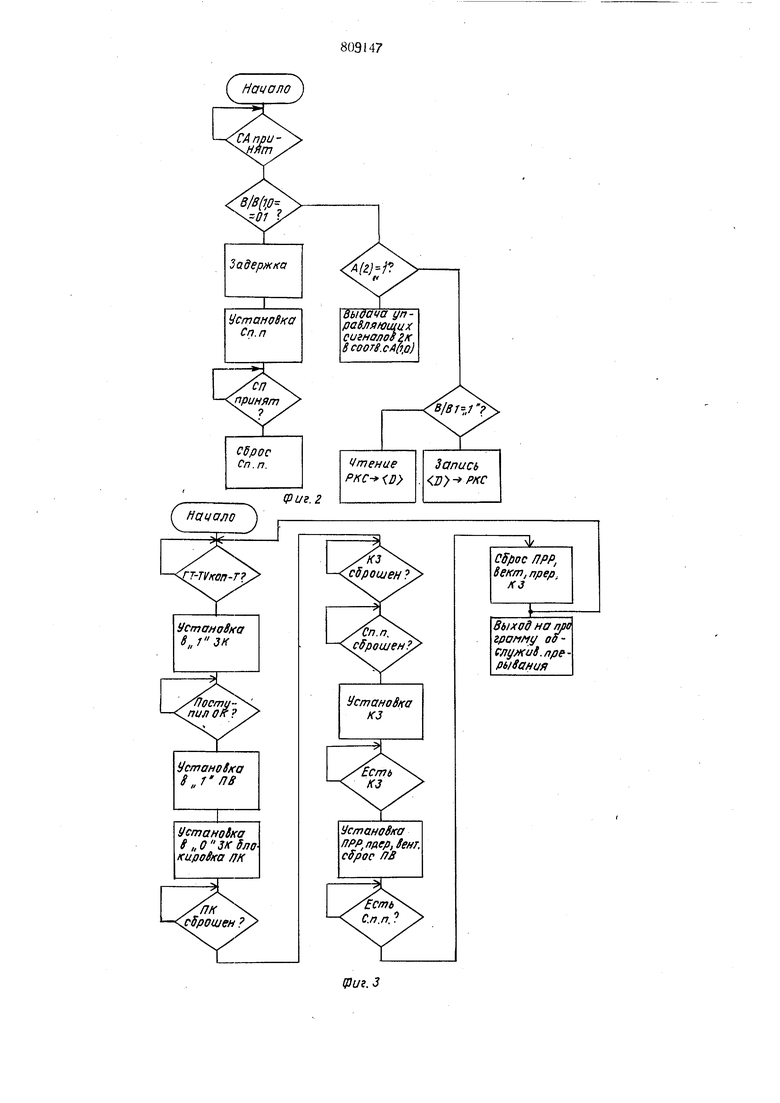

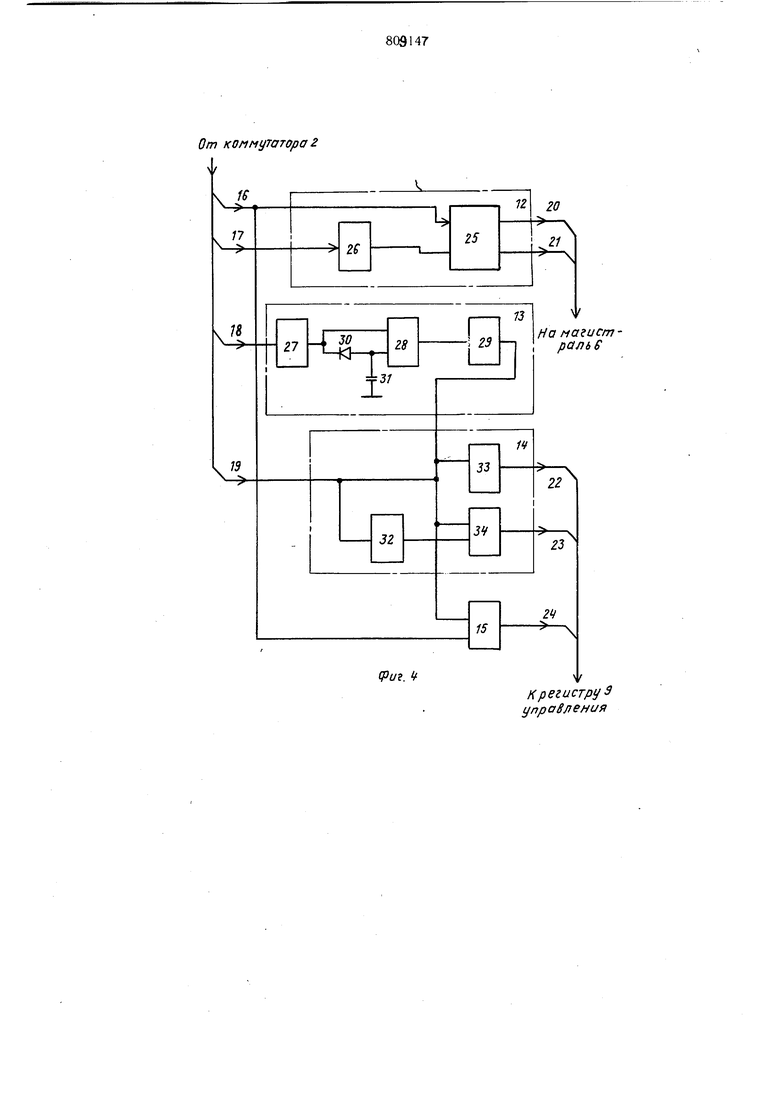

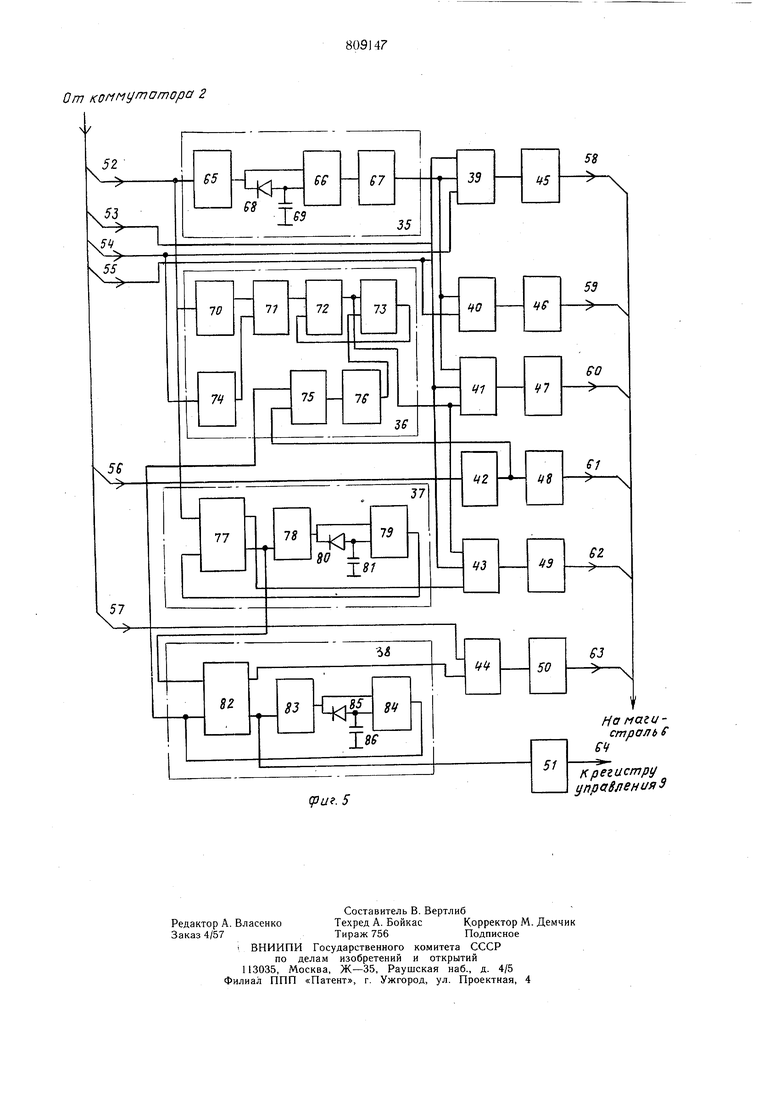

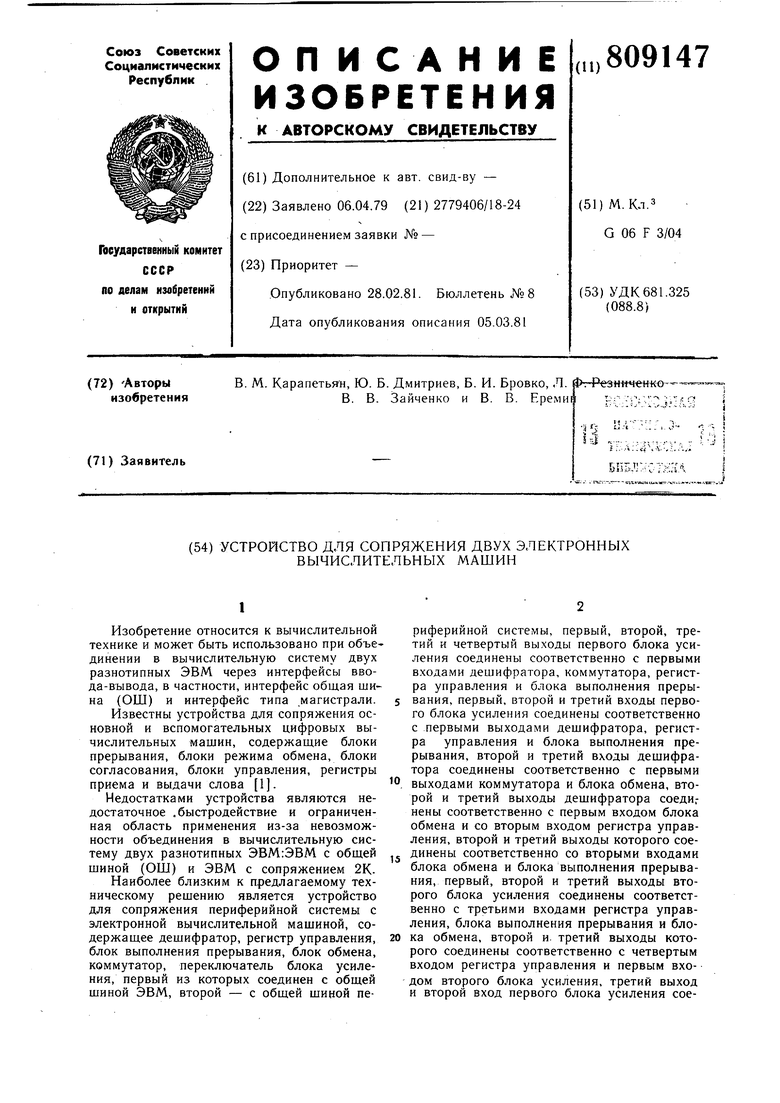

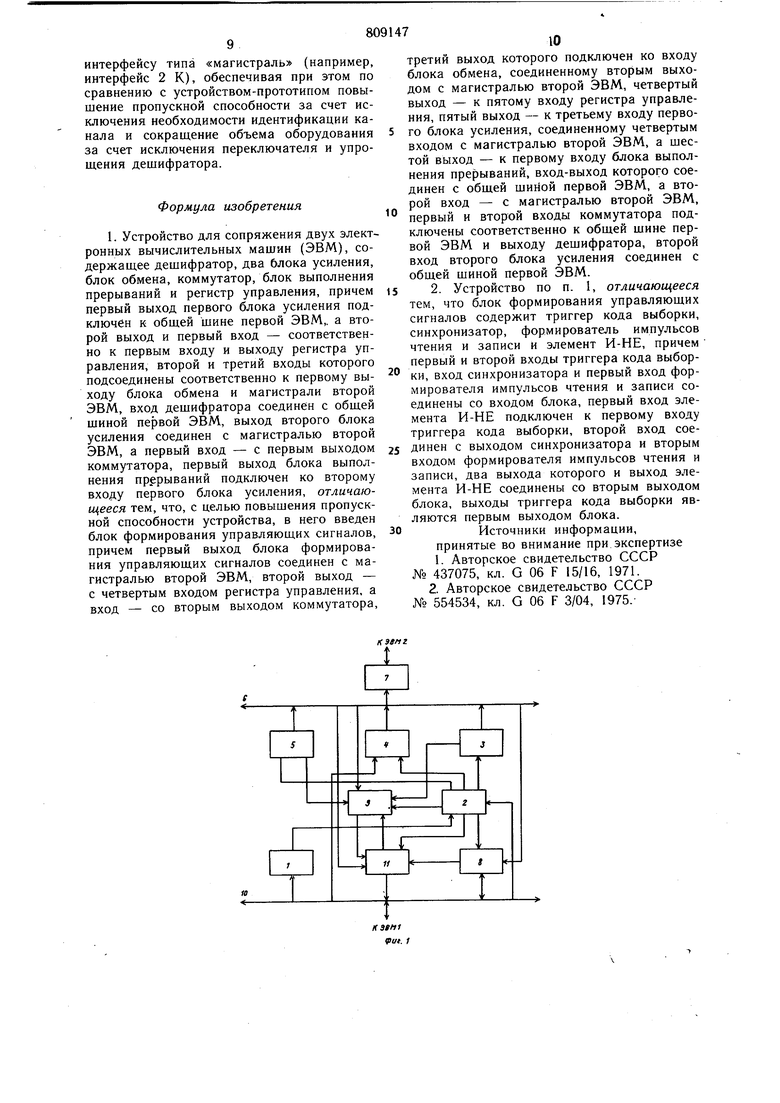

выходами коммутатора и блока обмена, второй и третий выходы дешифратора соедиг иены соответственно с первым входом блока обмена и со вторым входом регистра управления, второй и третий выходы которого соединены соответственно со вторыми входами блока обмена и блока выполнения прерывания, первый, второй и третий выходы второго блока усиления соединены соответственно с третьими входами регистра управления, блока выполнения прерывания и блока обмена, второй и. третий выходы которого соединены соответственно с четвертым входом регистра управления и первым входом второго блока усиления, третий выход и второй вход первого блока усиления соединены соответственно со вторым входом и четвертым выходом второго, блока усиления, первый и второй выходы коммутатора соединены с третьим и четвертым входами второго блока усиления, выход переключателя соединен с четвертыми входами блока выполнения прерывания и дешифратора, четвертый выход дешифратора соединен с четвертым входом блока обмена. Обшая шина периферийной системы этого устройства представляет собой магистраль с сопряжением 2К, причем устройство позволяет согласовать сигналы двух разнотипных интерфейсов - интерфейса ОШ с сопряжением 2К и осушествлять обмен данными между регистрами устройств периферийной системы и оперативной памятью ЭВМ под управлением программ с использованием прерываний 2. Недостаток этого устройства состоит в низкой пропускной способности, при использовании устройства для объединения в вычислительную систему ЭВМ с интерфейсом ОШ (например, «Электроника 100/16 И) и ЭВМ сопряжением 2К (например, «М6000 необходимо идентифицировать канал периферийной системы, к которой подключена ЭВМ. Цель изобретения - повышение пропускной способности устройства. Поставленная цель достигается тем, что в устройство, содержашее дешифратор, два блока усиления, блок обмена, коммутатор, блок выполнения прерываний и регистр управления, причем первый выход первого блока усиления подключен к обшей шине первой ЭВМ, а второй выход и первый вход - соответственно к первым входу и выхоДу регистра управления, второй и третий входы которого подсоединены соответственно к первому выходу блока обмена и магистрали второй ЭВМ, вход дешифратора соединен с обшей шиной первой ЭВМ, выход второго блока усиления соединен с магистралью второй ЭВМ, а первый вход - первым выходом коммутатора, первый выход блока выполнения прерываний подключен ко второму входу первого блока усиления, введен блок формирования управляющих сигналов, причем первый выход блока формирования управляющих сигналов соединен с магистралью второй ЭВМ, второй выход - с четвертым входом регистра управления, а входсо вторым выходом коммутатора, третий выход которого подключен ко входу блока обмена, соединенному вторым выходом с магистралью второй ЭВМ, четвертый выход к пятому входу регистра управления, пятый выход - к третьему входу первого блока усиления, соединенному четвертым входом с магистралью второй ЭВМ, а шестой выход - к первому входу блока выполнения прерываний, вход-выход которого соединен с общей шиной - первой ЭВМ, а второй вход - с магистралью второй ЭВМ первый и второй входы коммутатора подключены соответстве 1но к обшей шине первой ЭВМ и выходу дешифратора, второй вход второго блока усиления соединен с обшей шиной первой ЭВМ. Блок формирования управляющих сигналов содержит триггер кода выборки, синхронизатор, формирователь импульсов чтения и записи и элемент И-НЕ, причем первый и второй входы триггера кода выборки, вход синх,ронизатора. и первый вход формирователя импульсов чтения и записи соединены со входом блока, первый вход элемента И-НЕ подключен к первому входу триггера кода выборки, второй вход соединен с выходом синхронизатора и вторым входом формирователя импульсов чтеция и записи, два выхода которого и выход элемента И-НЕ соединены со вторым выходом блока, выходы триггера кода выборки являются первым выходом блока. На фиг. 1 приведено устройство, блоксхема; на фиг. 2 и 3 - блок-схемы алгоритмов работы устройства,- на фиг. 4 - функциональная схема блока формирования управляющих сигналов; на фиг. 5 - функциональная схема блока обмена. Устройство (фиг. 1) содержит дешифратор 1, коммутатор 2, блок 3 формирования управляющих сигналов, второй блок 4 усиления, осуществляющий усиление и выдачу информации на магистраль, блок 5 обмена, вырабатывающий сигналы управления для реализации заданного режима обмена, магистраль 6, второй ЭВМ, согласователь 7, осуществляющий согласование магистрали 6 со второй ЭВМ, блок 8 выполнения прерывания, реализующий операции захвата ОШ и прерывания программы, регистр 9 управления, осуществляющий выработку сигналов состояния усройства при обмене, общую шину 10 первой ЭВМ, первый блок 11 усиления, осушествляющий усиление и выдачу информации на общую шину первой ЭВМ. Устройство работает следующим образом. Устройство сопряжения работает по инициативе любой из двух ЭВМ. Работа устройства по инициативе первой ЭВМ (наприме, «Электроника 100/16 И) начинается с операции захвата управления каналом (алгоритм приведен на фиг. 2). Про;цессор первой ЭВМ выдает сигнал запроса канала, арбитр процессора анализирует, нет ли запроса с более высоким приоритетом. Если такого запроса нет, то арбитр разрешает захват канала и вырабатывает сигнал предоставления канала. При получении этого сигнала процессор выдает сигнал подтверждения выбора (ПВ) и сигнал занятия канала (КЗ), который запрещает другим устройствам работу с каналом. После этого процессор первой ЭВМ выдает на ОШ адрес устройства сопряжения и управляющую информацию, которая определяет режим обмена (ввод или вывод информации). С задержкой по отношению к адресу и управляющей информации из первой ЭВМ поступает сигнал синхронизации (СА), извещающий устройство о том, что на общую щину выставлены адрес и управляющая информация. Дещифратор 1 расщифровывает адрес и при его совпадении с заданным адресом устройства выдает сигнал разрещення работы с устройством в коммутатор 2. Коммутатор 2 выдает в блок 3 стробирующие импульсы, по приходу которых вырабатывается сигнал выборки. Этот сигнал определяет обмен информацией .между устройством сопряжения через согласователь 7 со второй ЭВМ (например, «М-6000). В качестве согласователя могут использоваться стандартные блоки, в частности, при расстоянии связи до 50 м используется дуплексный регистр типа А 491-ЗМ, при расстоянии до 1000 м - модуль быстрой передачи данных типа А 723-1. Коммутатор 2, кроме того, выдает сигнал приема данных в блок 4, по приходу которого происходит запись данных с общей щины 10 и выдача их на магистраль 6. По приходу стробирующего сигнала из блока 5 на магистраль 6 информация поступает через согласователь 7 для записи информации во вторую ЭВМ.. С задержкой коммутатор 2 выдает сигнал синхронизации СП на общую щину 10, первая ЭВМ снимает информацию и сигнал СА, подтверждая тем самым, что процесс передачи информации заверщен. Работа устройства по инициативе второй ЭВМ (например, «М-6000) начинается с выдачи процессором второй ЭВМ сигнала готовности (ГТ-Т) в блок 8 (алгоритм приведен на фиг, 3). Блок 8 выдает сигнал запроса канала в первую ЭВМ, с получением которого последняя выдает в блок 8 сигнал ПВ и сигнал КЗ, разрещая передачу управления каналом устройству. Блок 8 вырабатывает и выдает на общую шину 10 сигнал вектора прерывания (В) и сигнал прерывания (ПРР). Первая ЭВМ принимает сигнал ПРР, ожидает некоторое время, в течение которого в блоке 11 формируется адрес вектора прерывания и выдается на общую щину 10, после чего первая ЭВМ принимает адрес вектора прерывания и вырабатывает сигнал СП. Коммутатор 2 принимает сигнал СП и дает команду блоку 8 для снятия сигнала ПРР. Первая ЭВМ снимает сигнал СП и осуществляется прием информации из второй ЭВМ, По окончании операции передачи информации вторая ЭВМ вырабатывает сигнал конца операций, по приходу которого регистр 9 вырабатывает сигнал запрещения прерывания, подтверждается тем самым, что процесс передачи информации заверщен. Блок 3 управляющих сигналов управляет работой всего устройствасопряжения и содержит триггер 12 кода выборки, синхронизатор 13, |1ор.;ирователь 14 импульсов чте-, Hibi и , :.;1мент М-НЕ 15, адресную щину 16 , шины 17 и 18 импульсов синхронизации входа, щину 19 управления чтением и записью, входа блока щины 20 и 21 сигналов кода Выборки первого входа, щипы 22 и 23 сигналов чте:1ия и записи вторг; - вход; блока, адресного сигналя второго входа блока. Триггер 12 кода выборки содержит триггер 25 и элемент НЕ 26.. Синхронизатор 13 состоит из элементов НЕ 27, элемента и-НЕ 28. :л:;1..%;ента НЕ 29, диода 30 и конденсатора 3. Фop ;иpoвaтeль 14 сигналов чтения и записи содержит элемент НЕ 32 и элементы ИНЕ 33 и 34 (фиг. 4). Блок управляющих сигналов работает следующим образом. При наличии единичного уровня на шине 16 и отрицательного синхрои.мпульса на шине 17 триггер 25 устанавливается в такое положение, npii котором на его единичном выходе и шине 20 блока 3 устанавливается единичный уровень, а на нулевом выходе триггера 25 и на вы.ходе 21 блока - нулевой уровень. Единичный уровень на выходе 20 соответствует сигналу выборки, который указывает на то, что обмен информацией между ЭВМ осуществляется на расстоянии до 50 м через дуплексный регистр. При поступлении на адресную щину 16 уровня и отрицательного синхроимпульса на шину 17 триггер 25 перееключается и на шине 20 устанавлибается нулевой уровень, а на шине 21 - единичный уровень. Единичный уровень на щине 21 соответстБуст сигналу выборки, который указывагт на то, что обмен информацией осуществляется на расстоянии до 1000 м через модуль быстрой передачи данных. На шину 18 блока 3 поступают положительные и.мпульсы синхронизации. Синхронизатор 13 преобразует эти импульсы в отрицательные импульсы внутренней синхронизации, которые поступают в формирователь 14 и.на один из входов элемента И-НЕ 15. В формирователе 14 нмпульсы внутренней синхронизации поступают на щину 19, входы элементов И-НЕ 33 и 34. При поступлении на щину 19 единичного уровня элемент И-НЕ 33 открывается, разрещая прохождение сигнала чтения на щину 22, а элемент И-НЕ 34 в это время закрыт нулевым уровнем с выхода элемена НЕ 32. При нулевом уровне на шине 19 элемент И-НЕ 33 закрывается, а элемент И-НЕ 34 открывается инвертированным уровнем с элемента НЕ 32, разрещая прохожение сигнала записи на щину 23, При совпадении единичных уровней на ходах элемента И-НЕ 15 на щине 16 форируется сигнал адреса. Блок 5 обмена содержит формиробатель 35 внутренних импульсов синхронизации, формирователь 36 сигнала предварительного сброса, формирователь 37 сигнала приема информации, формирователь 38 сигнала выполнения, элементы И-НЕ 39-44, элементы НЕ 45-51, вход блока, включающий шину 52 синхронизации, шины 53 и 54 формирования сигналов передачи информации, шину 55 формирования сигнала окончания операции, шину 56 сигнала общего сброса и шину 57 формирования сигнала выполнения, второй выход блока, включающий шину 58 сигнала приема, шину 59 сигнала окончания операции, шину 60 сигнала предварительного сброса, шину 61 сигнала общего сброса, шину 62 сигнала приема информации, шину 63 сигнала выполнения, шину 64 внутреннего сигнала сброса первого выхода блока (фиг. 5). Формирователь 35 внутренних сигналов синхронизации состоит из элементов И-НЕ 65-67, диода 68 и конденсатора 69, формирователь 36 сигнала предварительного сброса содержит элементы И-НЕ 70-76, формирователь 37 сигнала приема информации состоит из триггера 77, элементов И-НЕ 78, 79, диода 80 и конденсатора 81, а формирователь 38 сигнала выполнения содержит триггер 82, элементы И-НЕ 83 и 84, диод 85 и конденсатор 86. В зависимости от входных сигналов блок обмена вырабатывает сигналы,, с помошью которых осушествляется обмен информацией между ЭВМ. На шину 52 приходят отрицательные имцульсы синхронизации, которые поступают на входы формирователей 1-3. Формирователь 35 преобразует эти импульсы в положительные импульсы синхронизации, которые поступают на входы элементов И-НЕ 39, 40 и 41. При наличии на двух других входах элемента И-НЕ 39 нулевого уровня, поступающего с шин 53 и 54, этот элемент закрыт. При поступлении на шины 53 и 54 единичных уровней элемент И-НЕ 39 открывается, разрешая прохождение через элемент 45 на- шину 58 сигнала приема, который разрешает выдачу информации с общей шины -10 на магистраль 6 (фиг. 1). Нулевой уровень на шине 55 закрывает элемент И-НЕ 40, на первый вход которого поступает внутренний импульс синхронизации с формирователя 35. Появление на шине 55 единичного уровня открывает элемент И-НЕ 40, разрешая прохождение через элемент НЕ 46 на шину 59 блока 5 сигнала окончания операции, который используется для указания общей шине об окончании операции. Формирователь 36 формирует сигнал предварительного сброса (ПСБ-К) в следуюшем случае. На шину 52 на вход элемента И-НЕ 70 поступает отрицательный импульс синхронизации, а на шину 54 и на вход элемента И-НЕ 74 поступает нулевой уровень. На выходе элемента И-НЕ 72 появляются положительнь1е импульсы, которые поступают на один из входов элементов И-НЕ 41 и 43. При совпадении единичных уровней на входах элемента И-НЕ 41 (синхроимпульса с выхода формирователя 35, единичного уровня с шины 53 и импульса с выхода формирователя 36) этот элемент открывается, разрешая прохождение через элемент НЕ 47 на шину 60 сигнала ПСБ-К,который устанавливает в нулевое состояние все триггеры устройства. Элементы 42 и 48 формируют сигнал обцХего сброса, который поступает на шину 61 при наличии сигнала сброса на шине 56 блока обмена. Формирователь 37 формирует сигнал приема информации (ВД-К) следующим образом. Начальная установка триггера 77 такова, что на нулевом выходе этого триггера устанавливается нулевой уровень, который закрывает элемент И-НЕ 43, а на единичном выходе-единичный уровень, который поступает на вход элемента И-НЕ 78 и на вход триггера 82. При поступлении на первый вход триггера 77 синхроимпульса с шины 52 этот триггер переключается. Через промежуток времени, определяемый задержкой изменения уровня элементами И-НЕ 78, 79 триггер 77 установится в исходное состояние ну,;евым уровнем с выхода элемента И-НЕ 79. Таким образом, происходит формирование сигнала ВД-К, который поступает на третий вход элемента И-НЕ 43. При наличии на двух других входах элемента И-НЕ 43 единичных уровней, этот элемент открывается, разрешая прохождение через элемент НЕ 49 на шину 62 сигнала ВД-К,который является стробирующим при приеме информации. Формирователь 38 формирует сигнал выполнения ВП-К при поступлении импульса с единичного выхода триггера 77 формирователя 37, аналогично описанному выще. С нулевого выхода триггера 82 сигнал ВП-К поступает на один из входов элемента ИНЕ 44 и при наличии на шине блока обмена единичного уровня, элемент И-НЕ 44 открывается, разрешая прохождение через элемент НЕ 50 на шину 63 сигнала ВП-К, который используется для осуществления операции ввода или вывода информации. С единичного выхода триггера 82 импульс через элемент НЕ 51 поступает на шину 64 и используется как сигнал регистра управления. Таким образом, устройство осуществляет сопряжение между двумя разнотипными ЭВМ, одна из которых подключается к интерфейсу типа «общая шина, а вторая - к

интерфейсу типа «магистраль (например, интерфейс 2 К), обеспечивая при этом по сравнению с устройством-прототипом повышение пропускной способности за счет исключения необходимости идентификации канала и сокращение объема оборудования за счет исключения переключателя и упрощения дешифратора.

Формула изобретения

третий выход которого подключен ко входу блока обмена, соединенному вторым выходом с магистралью второй ЭВМ, четвертый выход - к пятому входу регистра управления, пятый выход - к третьему входу первого блока усиления, соединенному четвертым входом с магистралью второй ЭВМ, а шестой выход - к первому входу блока выполнения прерываний, вход-выход которого соединен с общей шиной первой ЭВМ, а второй вход - с магистралью второй ЭВМ,

первый и второй входы коммутатора подключены соответственно к общей шине первой ЭВМ и выходу дешифратора, второй вход второго блока усиления соединен с общей щиной первой ЭВМ.

Источники информации,

принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 437075, кл. G 06 F 15/16, 1971.

ральК

(риг.

КрегиструЗ управления

От коммутатора 2

(puf. 5

стральf

К регистру упрс(8ления9

Авторы

Даты

1981-02-28—Публикация

1979-04-06—Подача