{

К)

со СП

Изобретение относится к вычисли- тельной технике и может быть использовано в информационно-измерительных вычислительных комплексах дотя подключения аналоговых датчиков в вычислительной машине.

Цель изобретения - повьпиение быстродействия .

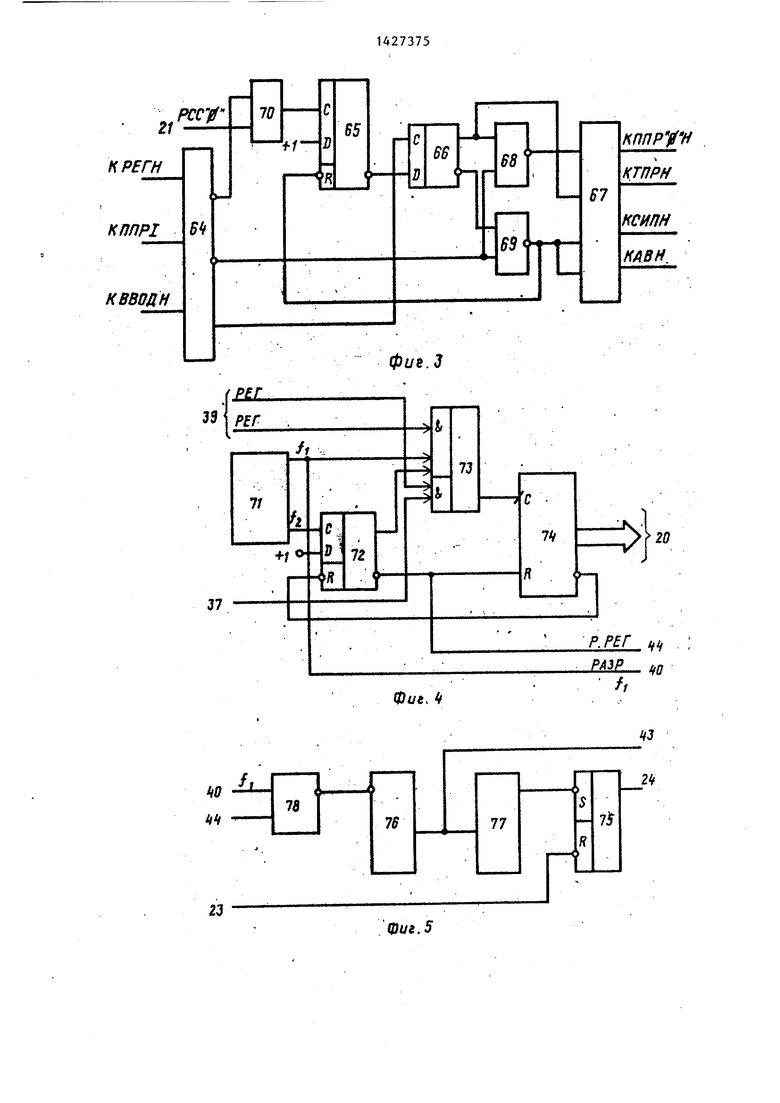

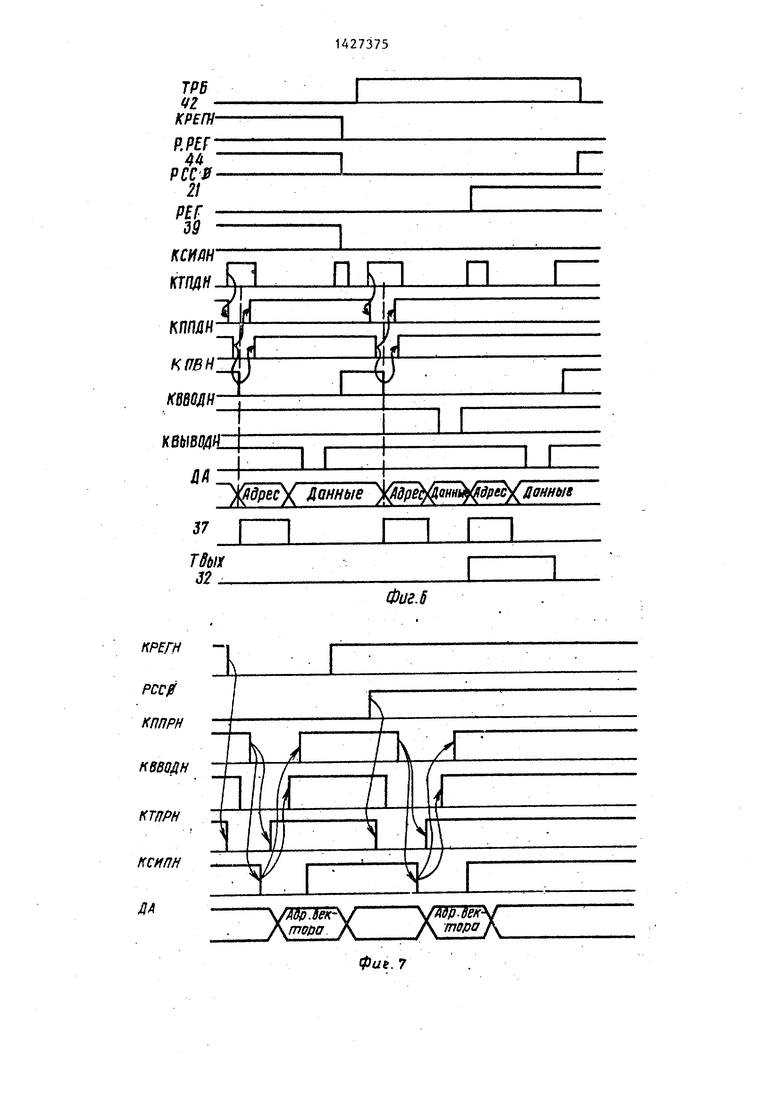

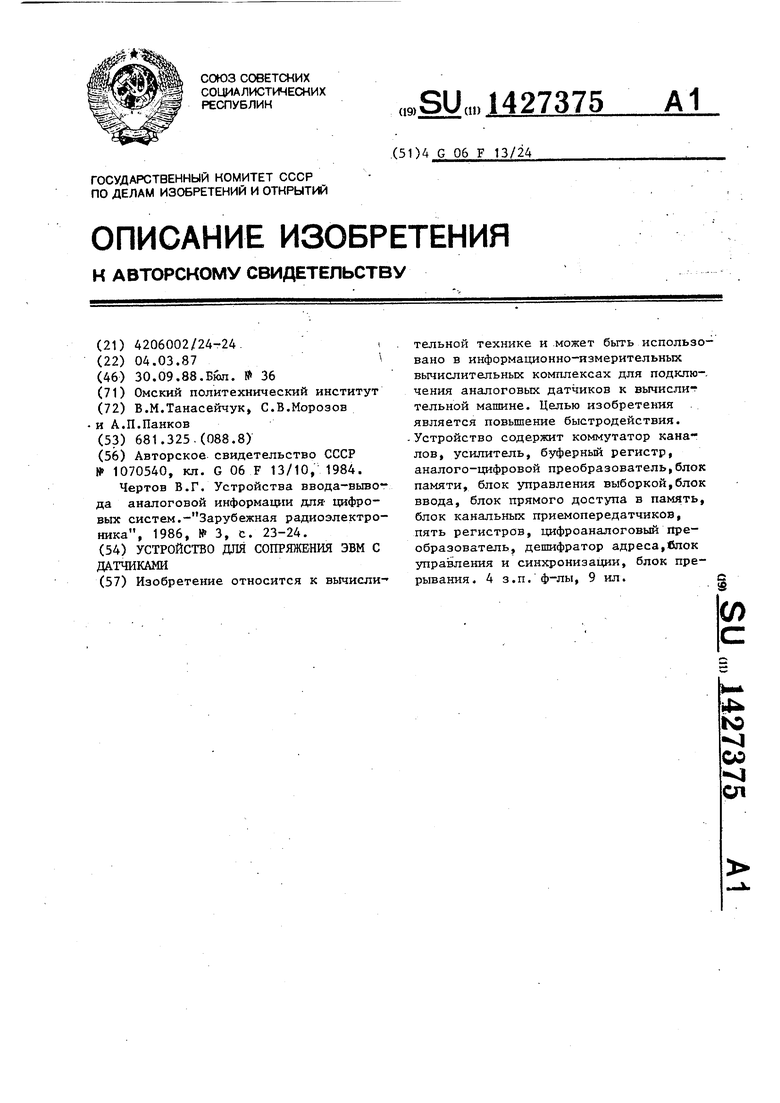

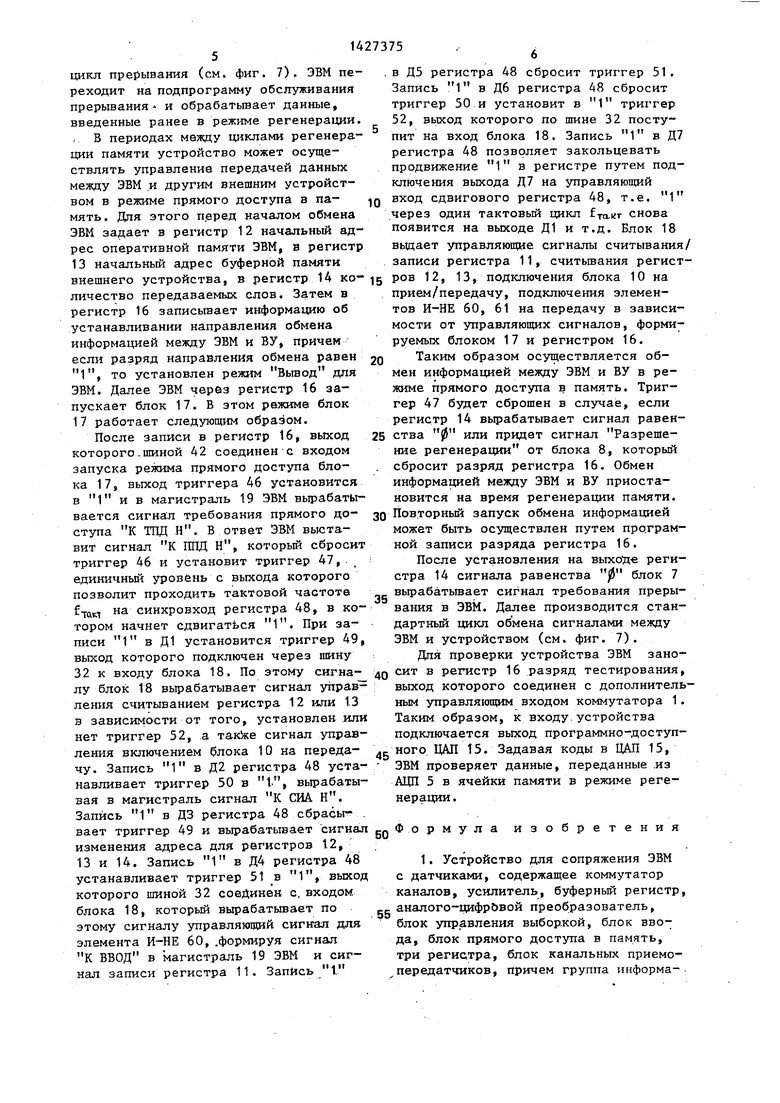

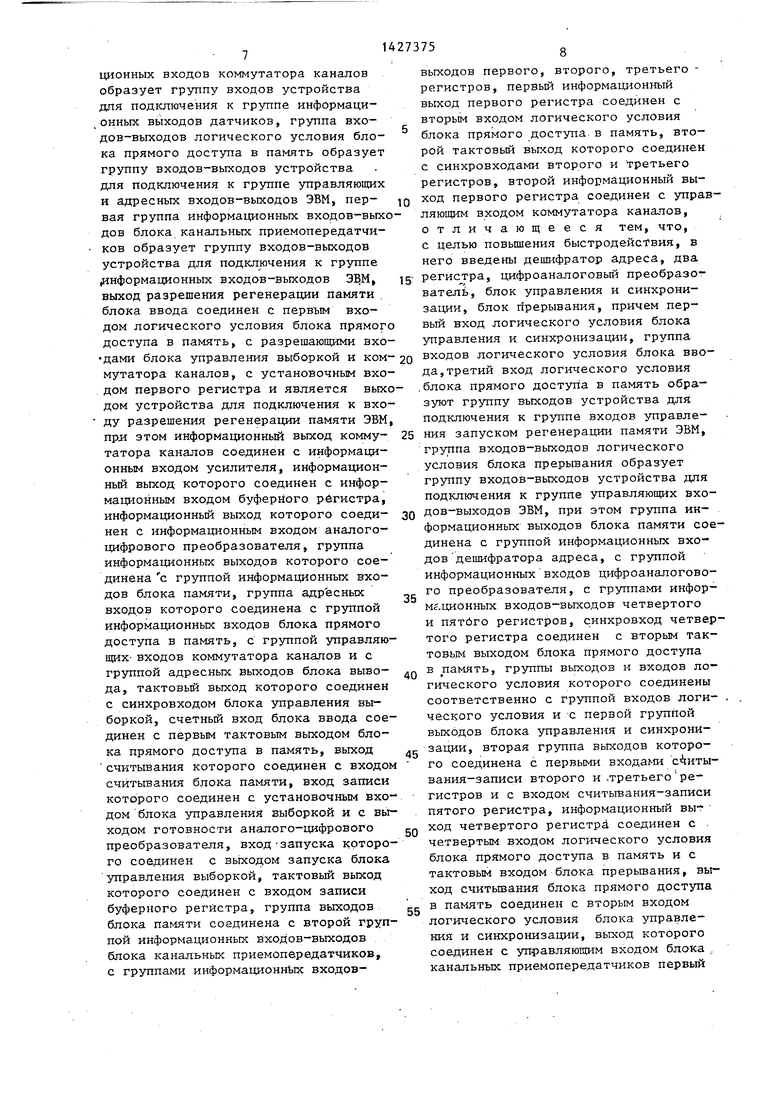

На фиг. 1 представлена блок-схема устройства для сопряжения ЭВМ с датчиками; на фиг. 2 - схема блока пря мого доступа в память; на фиг. 3 - схема блока прерывания; на фиг, 4 - схема блока ввода; на фиг. 5 - схема блока управления выборкой; на фиг. 7, 6, Sj 9 -временные диаграммы работы блока прямого доступа в память, блока прерывания, блока ввода, блока управления выборкой соответственно..

Устройство для сопряжения ЭВМ с датчиками содержит (фиг.1) коммутатор 1 каналов, усилитель 2,. буферный регистр 3, блок 4 управления выборкой аналого-цифровой преобразователь (АЦП) 5, блок 6 памяти, блок 7 прерывания, блок 8 ввода, дешифратор 9 адреса, блок 10 канальных приемопередатчиков, регистры 11-14, цифроанало- говьй преобразователь (ЦАЛ) 15, ре- гистр 16, блок 17 прямого доступа в память, блок 18 управления и синхро- 1-1изации, магистраль 19 ЭВМ, входы и . выходы (шины) 20-44 узлов и блоков устройства.

Блок 17 прямого доступа в память содержит .(фиг.2) канальный приемник 45, триггер 46, триггер 47, сдвиговый регистр 48, триггеры 49 - 52, канальные передатчики 53, 54, элементы И 55 - 59, элементы И-НЕ 60, 61, элементы ИЛИ 62, 63.

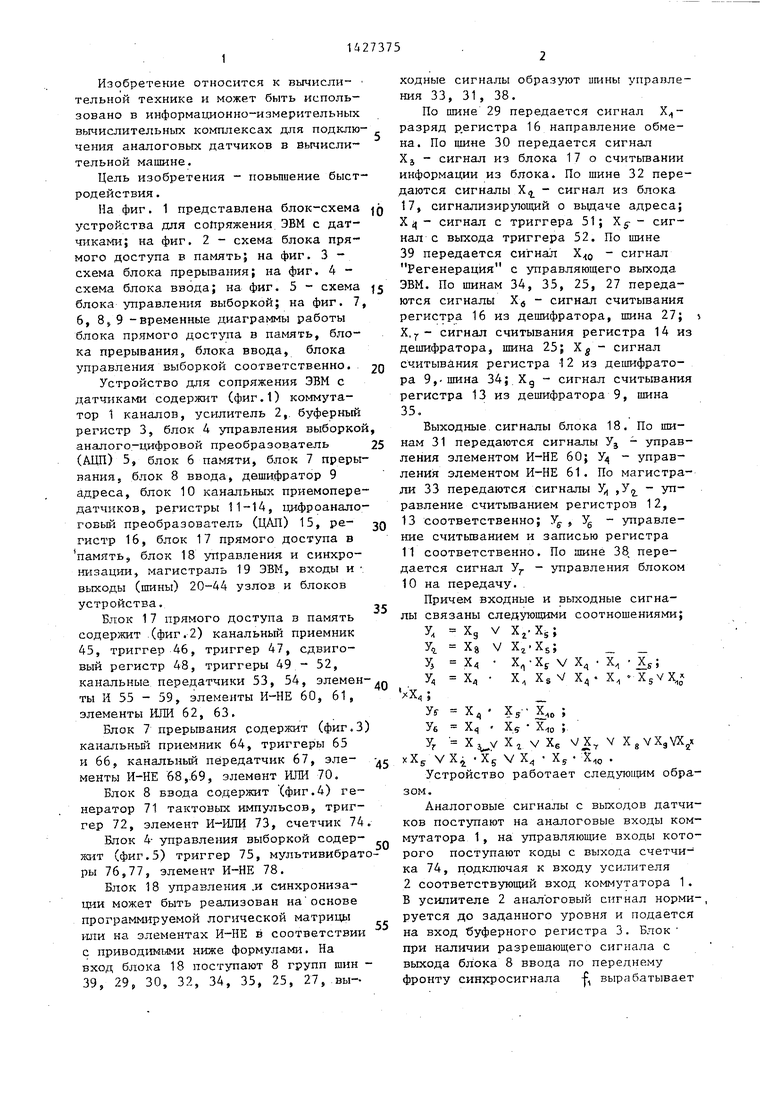

Блок 7 прерывания содержит (фиг.З) канальньй приемник 64, триггеры 65 и 66, канальный передатчик 67, эле- менты И-НЕ 68 ,.69, элемент ИЛИ 70.

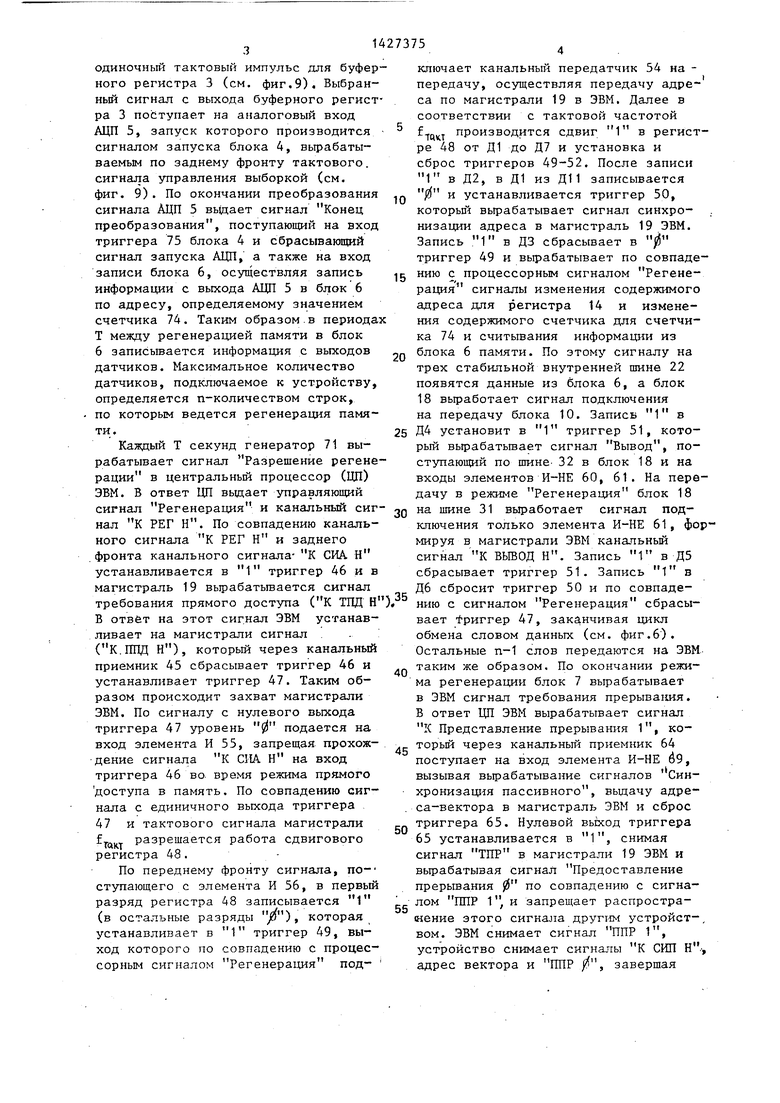

Блок 8 ввода содержит (фиг.4) генератор 71 тактовых импульсов, триггер 72, элемент И-ИЩ 73, счетчик 74

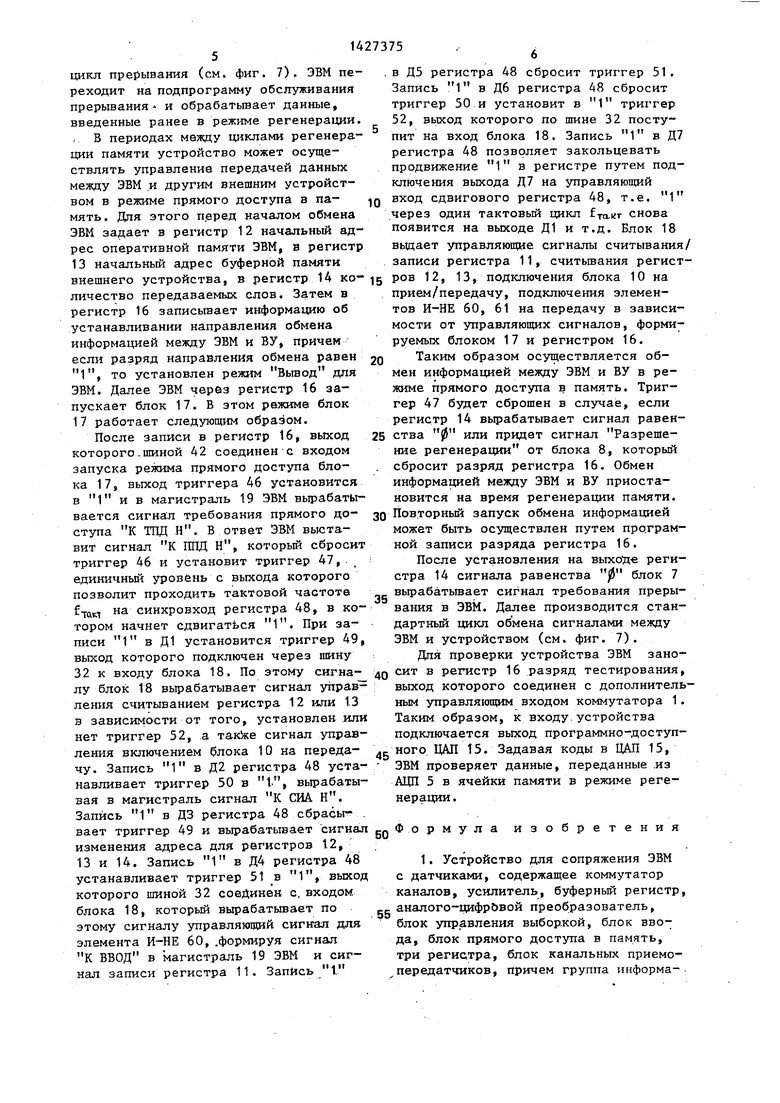

Блок 4- управления выборкой содержит (фиг.5) триггер 75, мультивибрато ры 76,77, элемент И-НЕ 78.

Блок 18 управления .и синхронизации может быть реализован на основе программируемой логической матрицы 1-ши на элементах И-НЕ в соответствии с приводимыми ниже формулами. На вход блока 18 поступают 8 групп шин - 39, 29, 30, 32, 34, 35, 25, 27, вы

Q j 0

5 Q

д

5

ходные сигналы образуют игины управления 33, 31, 38.

По шине 29 передается сигнал разряд регистра 16 направление обмена. По шине 30 передается сигнал Xj - сигнал из блока 17 о считьшании информации из блока. По шине 32 передаются сигналы Х - сигнал из блока 17, сигнализируюищй о выдаче адреса; X i - сигнал с триггера 51; - сигнал с выхода триггера 52, По шине 39 передается сигнал - сигнал Регенерация с управляющего выхода ЭВМ. По шинам 34, 35, 25, 27 передаются сигналы Xfl - сигнал считывания регистра 16 из дешифратора, шина 27; X,j. - сигнал считывания регистра 14 из дешифратора, шина 25; Х - сигнал считывания регистра 12 из дешифратора 9, шина 34; Хд - сигнал считывания регистра 13 из дешифратора 9, шина 35.

Выходные сигналы блока 18. По шинам 31 передаются сигналы Yj - управления элементом И-НЕ 60; У - управления элементом И-НЕ 61. По магистрали 33 передаются сигналы У ,J - управление считьгоанием регистров 12, 13 соответственно; У , Уд - управление считьшанием и записью регистра 11 соответственно. По пганё 38 передается сигнал У - управления блоком 10 на передачу.

Причем входные и выходные сигналы связаны следующими соотношениями;

У, Хд V X,.Xs;

Ха V

5

jj - Х Х Xf V Х Хх, Ху;

У, X, X, Xs V Х. X, ,

/Х,;

Уг X, х,о ; Уб - х( х Х-)о ;

г X X,, V Хб ч/Х V XgVXgVX xXj VX -X s V X Xg- X.o .

Устройство работает следующим образом.

Аналоговые сигналы с выходов датчиков поступают на аналоговые входы коммутатора 1, на управляющие входы которого поступают коды с выхода счетчика 74, подключая к входу усилителя 2 соответствующий вход коммутатора 1, В усилителе 2 аналоговый сигнал норми-, руется до заданного уровня и подается на вход буферного регистра 3. Блок при наличии разрешающего сигнала с выхода блока 8 ввода по переднему фронту синзсросигнала -р, выргабатывает

10

20

одиночный тактовый импульс для буферного регистра 3 (см. фиг.9). Выбранный сигнал с выхода буферного регистра 3 поступает на аналоговый вход АЦП 5, запуск которого производится сигналом запуска блока 4, вьфабаты- ваемым по заднему фронту тактового, сигнала управления выборкой (см. фиг. 9). По окончании преобразования сигнала АЦП 5 выдает сигнал Конец преобразования, поступающий на вход триггера 75 блока 4 и сбрасывающий сигнал запуска АЦП, а также на вход записи блока 6, осуществляя запись информации с выхода АЦП 5 в блок 6 по адресу, определяемому значением счетчика 74. Таким образом.в периодах Т между регенерацией памяти в блок 6 записывается информация с выходов датчиков. Максимальное количество датчиков, подключаемое к устройству, определяется п-количеством строк, по которым ведется регенерация памяти.

Каяздый Т секунд генератор 71 вырабатывает сигнал Разрешение регенерации в центральньм процессор (ЦП) ЭВМ. В ответ ЦП вьщает управляющий сигнал Регенерация и канальный сигнал К РЕГ Н. По совпадению канального сигнала К РЕГ Н и заднего фронта канального сигнала- К СИА Н устанавливается в 1 триггер 46 и в магистраль 19 вырабатьгоается сигнал требования прямого доступа (К ТПД Н), В ОТВЕТ на этот сиг.нал ЭВМ устанавливает на магистрали сигнал - (К.ППД Н), который через канальный приемник 45 сбрасывает триггер 46 и устанавливает триггер 47. Таким образом происходит захват магистрали ЭВМ. По сигналу с нулевого вькода триггера 47 уровень 0 подается на вход элемента И 55, запрещая прохождение сигнала К CIIA Н на вход триггера 46 во время режима прямого доступа в память. По совпадению сигнала с единичного выхода триггера 47 и тактового сигнала магистрали f разрешается работа сдвигового регистра 48.

По переднему фронту сигнала, по- ступающего с элемента И 56, в первый разряд регистра 48 записывается 1 (в остальные разряды 0), которая устанавливает в 1 триггер 49, выход которого по совпадению с процессорным сигналом Регенерация под-

g

25

30

40

45

50

55

0

0

ключает канальный передатчик 54 на - передачу, осуществляя передачу адреса по магистрали 19 в ЭВМ. Далее в соответствии с тактово1Ч частотой производится сдвиг 1 в регистре 48 от Д1 до Д7 и установка и сброс триггеров 49-52. После записи 1 в Д2, в Д1 из Д11 записывается f и устанавливается триггер 50, которьй вьфабатывает сигнал синхронизации адреса в магистраль 19 ЭВМ. Запись 1 в ДЗ сбрасывает в триггер 49 и вырабатывает по совпадеg нию с процессорным сигналом Регенерация сигналы изменения содержимого адреса для регистра 14 и изменения содержимого счетчика для счетчика 74 и считывания информации из блока 6 памяти. По этому сигналу на трех стабильной внутренней шине 22 появятся данные из блока 6, а блок 18 вьфаботает сигнал подключения на передачу блока 10. Запись 1 в

5 Д4 установит в 1 триггер 51, который вьфабатывает сигнал Вывод, поступающий по шине- 32 в блок 18 и на входы элементов И-НЕ 60, 61. На передачу в режиме Регенерация блок 18 на шине 31 выработает сигнал подключения только элемента И-НЕ 61, формируя в магистрали ЭВМ канальньй сигнал ВЬГООД Н. Запись 1 в Д5 сбрасывает триггер 51. Запись 1 в Д6 сбросит триггер 50 и по совпадению с сигналом Регенерация сбрасывает триггер 47, заканчивая цикл обмена словом данных (см. фиг.6). Остальные п-1 слов передаются на ЭВМ- таким же образом. По окончании режима регенерации блок 7 вьфабатывает в ЭВМ сигнал требования прерывания. В ответ ЦП ЭВМ вьфабатывает сигнал К Представление прерывания 1, ко- торьй через канальный приемник 64 поступает на вход элемента И-НЕ Й9, вызывая вьфабатывание сигналов Синхронизация пассивного, выдачу адреса-вектора в магистраль ЭВМ и сброс триггера 65. Нулевой вьЬсод триггера 65 устанавливается в 1, снимая сигнал ТПР в магистрали 19 ЭВМ и вьфабатывая сигнал Предоставление прерывания 0 по совпадению с сигналом ППР 1, и запрещает распространение этого сигнала другим устройст-, вом. ЭВМ снимает сигнал ППР 1, устройство снимает сигналы К СИП , адрес вектора и ППР , завершая

0

0

5

0

5

1427375

56

цикл пре15ынания (см, фиг. 7). ЭВМ пе- , в Д5 регистра А8 сбросит триггер 51. реходит на подпрограмму обслуживания Запись 1 в Дб регистра 48 сбросит прерывания- и обрабатьгеает данные, триггер 50 и установит в 1 триггер введенные ранее в режиме регенерации. 52, виход которого по шине 32 посту- , В периодах между циклами регенера- пит на вход блока 18. Запись 1 в Д7 ции памяти устройство может осуще- регистра 48 позволяет закольцевать ствлять управление передачей данных продвижение 1 в регистре путем под- между ЭВМ и другим внешним устройст- ключения вьпсода Д7 на управляющий вом в режиме прямого доступа в па- Q вход сдвигового регистра 48, т.е. 1 мять. Для этого п.еред началом обмена через один тактовый цикл frakr снова ЭВМ задает в регистр 12 начальный ад- появится на выходе Д1 и т.д. Блок 18 рее оперативной памяти ЭВМ, в регистр вьщает управляющие сигналы считывания/ 13 начальный адрес буферной памяти записи регистра 11, считьшания регист- внешнего устройства, в регистр ТА ко-щ ров 12, 13, подключения блока 10 на личество передаваемых слов. Затем в прием/передачу, подключения элемен- регистр 16 записывает информацию об тов И-НЕ 60, 61 на передачу в зависи- устанавливании направления обмена мости от управляющих сигналов, форми- информацией между ЭВМ и ВУ, причем руемых блоком 17 и регистром 16. если разряд направления обмена равен 20 Таким образом осуществляется об- 1, то установлен режим Вывод для мен информацией между ЭВМ и ВУ в ре- ЭВМ. Далее ЭВМ через регистр 16 за- жиме прямого доступа в память. Триг- пускает блок 17. В этом режиме блок гер 47 будет сброшен в случае, если 17 работает следующим образом. регистр 14 вырабатывает сигнал равенПосле записи в регистр 16, выход 25 ства 0 или придет сигнал Разреше- которого.шиной 42 соединен с входом ние регенерации от блока 8, которьй запуска режима прямого доступа бло- . сбросит разряд регистра 16. Обмен ка 17, выход триггера 46 установится информацией между ЭВМ и ВУ приоста- в 1 и в магистраль 19 ЭВМ вырабатЫ- новится на время регенерации памяти, вается сигна:л требования прямого до- зо Повторный запуск обмена информацией ступа К ТПД Н. В ответ ЭВМ выста- может быть осуществлен путем програм- вит сигнал К ППД Н, который сбросит ной записи разряда регистра 16. триггер 46 и установит триггер 47, После установления на выхо де реги- единичный уровень с выхода которого стра 14 сигнала равенства блок 7 позволит проходить тактовой частоте вырабатьтает сигнал требования преры- на синхровход регистра 48, в ко- вания в ЭВМ. Далее производится стан- тором начнет сдвигаться 1. При за- дартньй цикл обмена сигналами между писи 1 в Д1 установится триггер 49, ЭВМ и устройством (см. фиг. 7). выход которого подключен через шину Для проверки устройства ЭВМ зано- 32 к входу блока 18. По этому сигна- 0 регистр 16 разряд тестирования, лу блок 18 вырабатывает сигнал управ- ; выход которого соединен с дополнитель- ления считыванием регистра 12 или 1.3 ным управляющим входом коммутатора 1. в зависимости от того, установлен или Таким образом, к входу.устройства нет триггер 52, а сигнал управ- подключается выход программно-доступ- ления включением Олока 10 на переда- Лс ного ЦАП 15. Задавая коды в ЦАП 15, чу. Запись 1 в Д2 регистра 48 уста- ЭВМ проверяет данные, переданные .из навливает триггер 50 в t, вырабаты- АЦП 5 в ячейки памяти в режиме реге- вая в магистраль сигнал К СИА Н. нерагщи. Запись 1 в ДЗ регистра 48 сбрасы- .

вает триггер 49 и вьфабатывает сигнал gQ Формула изобретения изменения адреса для регистров t2, ;

13 и 14. Запись 1 в Д4 регистра 48 1. Устройство для сопряжения ЭВМ устанавливает триггер 51 в 1, выход с датчиками, содержащее коммутатор которого шиной 32 соединен с, входом каналов, усилитель, буферный регистр, блока 18, который вырабатывает по g аналого-цифр&вой преобразователь, этому сигналу управляющий сигнал для блок управления выборкой, блок вво- элемента И-НЕ 60, .формируя сигнал да, блок прямого доступа в память, К ВВОД в магистраль 19 ЭВМ и сиг- три регистра, блок канальных приемо- нал записи регистра 11. Запись 1 передатчиков, причем группа ннформа-.

ционных входов коммутатора каналов образует группу входов устройства для подключения к группе информаци- ,онных выходов датчиков, группа входов-выходов логического условия блока прямого доступа в память образует группу входов-выходов устройства для подключения к грзпппе управляющих и адресных входов-выходов ЭВМ, пер- Q вая группа информационных входов-выходов блока канальных приемопередатчиков образует группу входов-выходов устройства для подключения к группе информационных входов-выходов ЭВМ, is выход разрешения регенерации памяти блока ввода соединен с первым входом логического условия блока прямого доступа в память, с разрешающими вхо- дами блока управления выборкой и ком- 2о вводов логического условия блока вво- мутатора каналов, с установочным вхо- да,третий вход логического условия дом первого регистра и является выхо- .блока прямого доступа в память обравьгходов первого, второго, третьего - регистров, первьш информационный выход первого регистра соединен с вторым входом логического условия блока прямого доступа в память, второй тактовьш выход которого соединен с синхровходами второго и третьего регистров, второй информационный выход первого регистра соединен с управляющим входом коммутатора каналов, отличающееся тем, что, с целью повышения быстродействия, в него введены дешифратор адреса, два регистра, цифроаналоговый преобразователь, блок управления и синхронизации, блок прерывания, причем первый вход логического условия блока управления и синхронизации, группа

вводов логического условия блока вво да,третий вход логического условия блока прямого доступа в память обравьгходов первого, второго, третьего - регистров, первьш информационный выход первого регистра соединен с вторым входом логического условия блока прямого доступа в память, второй тактовьш выход которого соединен с синхровходами второго и третьего регистров, второй информационный выход первого регистра соединен с упраляющим входом коммутатора каналов, отличающееся тем, что, с целью повышения быстродействия, в него введены дешифратор адреса, два регистра, цифроаналоговый преобразователь, блок управления и синхронизации, блок прерывания, причем первый вход логического условия блока управления и синхронизации, группа

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения двух микроЭВМ с общим внешним устройством | 1985 |

|

SU1345206A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1534509A2 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Устройство для сопряжения двух ЭВМ с общим внешним устройством | 1986 |

|

SU1365089A1 |

| Устройство для сопряжения двух ЭВМ | 1986 |

|

SU1363230A1 |

| Устройство для регенерации динамической памяти | 1987 |

|

SU1434497A1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных вьмислительных комплексах для подклю-. чения аналоговых датчиков к вычислительной машине. Целью изобретения является повышение быстродействия. .Устройство содержит коммутатор кана лов, усилитель, буферньй регистр, аналого-цифровой преобразователь,блок памяти, блок управления выборкой,блок ввода, блок прямого доступа в память, блок канальных приемопередатчиков, пять регистров, цифроаналоговый преобразователь, дешифратор адреса,влек управления и синхронизации, блок прерывания. 4 з.п. ф-лы, 9 ил.

30

35

40

дом устройства для подключения к вхо- ду разрешения регенерации памяти ЭВМ, прл этом информационный выход коммутатора каналов соединен с информаци- онньм входом усилителя, информационный выход которого соединен с информационным входом буферного регистра, информационный выход которого соединен с информационным входом аналого- цифрового преобразователя, группа информационных выходов которого соединена с группой информационных входов блока памяти, группа адресных входов которого соединена с группой информационных входов блока прямого доступа в память, с группой управляющих- входов коммутатора каналов и с группой адресньпс выходов блока вывода, тактовый выход которого соединен с синхровходом блока управления выборкой, счетный вход блока ввода соединен с первым тактовым выходом блока прямого доступа в память, выход g

считывания которого соединен с входом считывания блока памяти, вход записи которого соединен с установочным входом блока управления выборкой и с выходом готовности аналого-цифрового преобразователя, вход-запуска которого соединен с выходом запуска блока

управления выборкой, тактовый выход которого соединен с входом записи буферного регистра, группа выходов блока памяти соединена с второй группой информационных входов-выходов блока канальных приемопередатчиков, с группами информационнЬпс входов25

50

55

зуют группу выходов устройства для подключения к группе входов управле- ния запуском регенерации памяти ЭВМ, группа входов-выходов логического условия блока прерывания образует группу входов-выходов устройства для подключения к группе управляющих входов-выходов ЭВМ, при этом группа информационных выходов блока памяти соединена с группой информационных входов дешифратора адреса, с группой информационных входов цифроаналогово- го преобразователя, с группами инфор- Мс.ционных входов-выходов четвертого и пятбго регистров, синхровход четвертого регистра соединен с вторым тактовым выходом блока прямого доступа в память, группы выходов и входов логического условия которого соединены соответственно с группой входов логи- . ческого условия и -с первой группой выходов блока управления и синхронизации, вторая группа выходов которого соединена с первыми входами вания-записи второго и-третьего регистров и с входом считьгеания-записи пятого регистра, информационный вы- ход четвертого регистра соединен с . четвертым входом логического условия блока прямого доступа в память и с тактовым входом блока прерьтания, выход считьтания блока прямого доступа в память соединен с вторым входом логического условия блока управления и синхронизации, выход которого соединен с управляющим входом блока , канальных приемопередатчиков первый

выход дешифратора адреса соединен с первым, вторым, третьим входами считывания первого регистра и с третьим входом логического условия блока управления и синхронизации, четвертый вход логического условия которого соединен с входом считывания четвертого регистра и с вторым выходом дешифратора адреса, третий выход которого соединен о вторым входом записи-считывания второго регистра и с пятым входом логического условия

мента И является первым тактовым выходом блока, первый вьпсод сдвигового регистра соединен с нулевым входом второго триггера, с вторым входом третьего элемента И и является вторы тактовым входом блока, единичный выход второго триггера, соединенный с вторым разрешающим входом первого ка нального передатчика, единичный выход первого триггера и единичньй выход третьего триггера, соединенный с первыми входами и- первого и второго элементов И-НЕ, образуют группу

блока управления и синхронизации,

шестой вход логического условия кото- 15 выходов логического условия блока,

рого .соединен с вторым входом записи- вторые входы первого и второго эласчитьгоания третьего регистра и с

четвертым выходом дешифратора адреса,

пятый выход которого соединен с вхоментов И-НЕ образуют группу входов логического условия блока, группа информационных входов первого каналь

дом запуска цифроаналогового преобра- 20 ного передатчика образует группу инзователя, информационный выход которого соединен с информационным входом коммутатора каналов И является выходом устройства для подключения к информационным входам датчиков, третий информационный выход первого регистра соединен с седьмым входом логического условия блока управления и синхронизации.

2, Устройство по П.1, о т л и- чающееся тем, что блок прямо- го доступа в память содержит сдвиговый регистр, два канальных передат-. чика, шесть триггеро.в, канальный приемник, пять элементов И, два элемента ИЛИ, два элемента И-НЕ, причем первые входы первого и второго элементов И, первый, второй информационные входы канального приемника.

формационных входов блока, выход четвертого элемента И является вькодом считьшания блока, при этом в блоке прямого доступа в память перв ый ин25 формационный вход второго канального передатчика соединен с единичным выходом четвертого триггера, синхро- вход которого соединен с вькодом первого элемента И, второй вход кото30 рого соединен с нулевым выходом пятого триггера, синхровход которого соединен с первым информационным выходом канального приемника, информационный выход которого-соединен с вторым входом второго элемента ИЛИ, выход которого соединен с информационным входом четвертого триггера, нулевой вход которого соединен с синхровходом пятого-триггера, единич35

группа информационных выходов перво- 4о иь й выход которого соединен с вторым го канального передатчика, первый, второй, третий информационные выходы второго канального передатчика, выходы первого, второго элементов И-НЕ

информационным входом второго канального передатчика и с вторым входом второго элемента И, выход которого соединен с синхровходом сдвигового

образуют группу входов-выходов логи- 45 Регистра, второй выход которого соеческого условия блока, первые входы первого и второго элементов ИЛИ являются соответственно первым и вторым входами лопгческого условия блока, второй вход первого элемента ИЛИ соединен с разрешающим входом первого триггера, с первым разрешающим входом первого канального передатчика, с первыми входами третьего,четвертого элементов И и является тре- тьим входом логического условия блока, третий,вход первого элемента ИЛИ является четвертым входом логического условия блока, выход третьего элединен с нулевым входом шестого триггера, с первым входом пятого элемента И и со Счетным .входом первого триг гера, нулевой выход которого соеди5Q нен с вторым входом пятого элемента И, третий вход и выход которого сое динены соответственно с выходом перв го элемента ИЛИ и с нулевым входом пятого триггера, информационный вход

55 которого подключен к шине единичного потенциала устройства, второй вход, четвертого элемента И соединен с нулевым выходом второго триггера, единичный вход которого соединен с тре

мента И является первым тактовым выходом блока, первый вьпсод сдвигового регистра соединен с нулевым входом второго триггера, с вторым входом третьего элемента И и является вторым тактовым входом блока, единичный выход второго триггера, соединенный с вторым разрешающим входом первого канального передатчика, единичный выход первого триггера и единичньй выход третьего триггера, соединенный с первыми входами и- первого и второго элементов И-НЕ, образуют группу

ментов И-НЕ образуют группу входов логического условия блока, группа информационных входов первого канальформационных входов блока, выход четвертого элемента И является вькодом считьшания блока, при этом в блоке прямого доступа в память перв ый ин5 формационный вход второго канального передатчика соединен с единичным выходом четвертого триггера, синхро- вход которого соединен с вькодом первого элемента И, второй вход кото0 рого соединен с нулевым выходом пятого триггера, синхровход которого соединен с первым информационным выходом канального приемника, информационный выход которого-соединен с вторым входом второго элемента ИЛИ, выход которого соединен с информационным входом четвертого триггера, нулевой вход которого соединен с синхровходом пятого-триггера, единич5

иь й выход которого соединен с вторым

информационным входом второго канального передатчика и с вторым входом второго элемента И, выход которого соединен с синхровходом сдвигового

динен с нулевым входом шестого триггера, с первым входом пятого элемента И и со Счетным .входом первого триггера, нулевой выход которого соеди5Q нен с вторым входом пятого элемента И, третий вход и выход которого соединены соответственно с выходом первого элемента ИЛИ и с нулевым входом пятого триггера, информационный вход

55 которого подключен к шине единичного потенциала устройства, второй вход, четвертого элемента И соединен с нулевым выходом второго триггера, единичный вход которого соединен с тре

тьим выходом сдвигового регистра, четвертый выход которого соединен с единичным входом третьего триггера, нулевой вход которого соединен с пятым выходом сдвигового регистра, шее той выход которого соединен с управляющим входом сдвигового регистра, . седьмой выход которого соединен с единичньм входом шестого триггера, единичный выход которого соединен с третьим информационным входом второго канального передатчика.

и является выходом разрешения регенерации памяти, первый синхровыход ге нарагора тактовых импульсов соединен с четвертым входом элемента И-ИЛИ и является тактовым выходом блока, при этом в блоке ввода второй синхровыход генератора тактовых импульсов соединен с синхровходом триггера, единичный выход которого соединен с пятым входом элемента И-ИПИ, выход которого соединен со счетным входом счетчика, выход переполнения соединен с нулевьм входом триггера, информационный вход которого подключен к шине единичного потенциала устройства,

элемент ИЛИ, два элемента И-НЕ, причем первый, второй, третий информационные входы канального приемника, шервый, второй, третий, четвертый информационные выходы канального

0

5

g

о

0

5

0

5

передатчика образуют группу входов- выходов логического условия блока, первый вход элемента ИЛИ является тактовьм входом блока, при этом в блоке прерывания первыт информационный выход канал ьного приемника соединен с вторым входом элемента ИЛИ, выход которого соединен с синхровходом первого триггера, нулевой выход которого соединен с информационным входом второго триггера, единичный выход которого соединен с первым входом первого элемента И-НЕ и с первым инфор мационным входом канального передатчика, второй информационный вход которого соединен с выходом первого элемента И-НЕ, второй вход которого соединен с первым входом второго элемента И-НЕ и с вторым информационным выходом канального приемника, третий информационньй выход которого соединен с синхровходом второго триггера, нулевой выход которого соединен с вторым входом второго элемента И-НЕ, выход которого соединен с третьим, четвертым информационными входами канального передатчика и с нулевым входом первого триггера, информационный вход которого подключен к шине единичного потенциала устройства.

КРЕГН

КППР1

КВВОДН

.

fi

ЧЧ fO

Фиг, 5

ТРВ

т КРШp.ptf

44

РСС 21

РЕГ д9

КСИДН КТПДН,

кппт

KffBH КВдОДН

штм лл

LI

дресХ Аанные )f dpe oim pe ffffffNe

37

TSdIX 32

КРЕГН

РСС0 КППРН

ХА1Ц). тора А

Г

1

П

гп гп

Фиг.б

АОр.век тора

фие. 7

РЕГ J9

V 37

/,

f П n-fiVi-fi П ri-fiti f П П

23

фи.З

(piva.S

| Устройство для сопряжения вычислительной машины с датчиками | 1982 |

|

SU1070540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чертов В.Г | |||

| Устройства ввода-вывода аналоговой информации для- цифровых систем.- Зарубежная радиоэлектроника, 1986, № 3, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1988-09-30—Публикация

1987-03-04—Подача