(54) УСТРОЙСТВО для ФУНКЦИОНАЛЬНОГО КОНТРОЛЯ МИКРОЭЛЕКТРОННЫХ УЗЛОВ

вход - с выходом формирователя сигнала отключения питания объекта контроля, управляющий вход которого подключен к выходу пульта управления, а тактовый вход - ко второму выходу генератора импульсов.

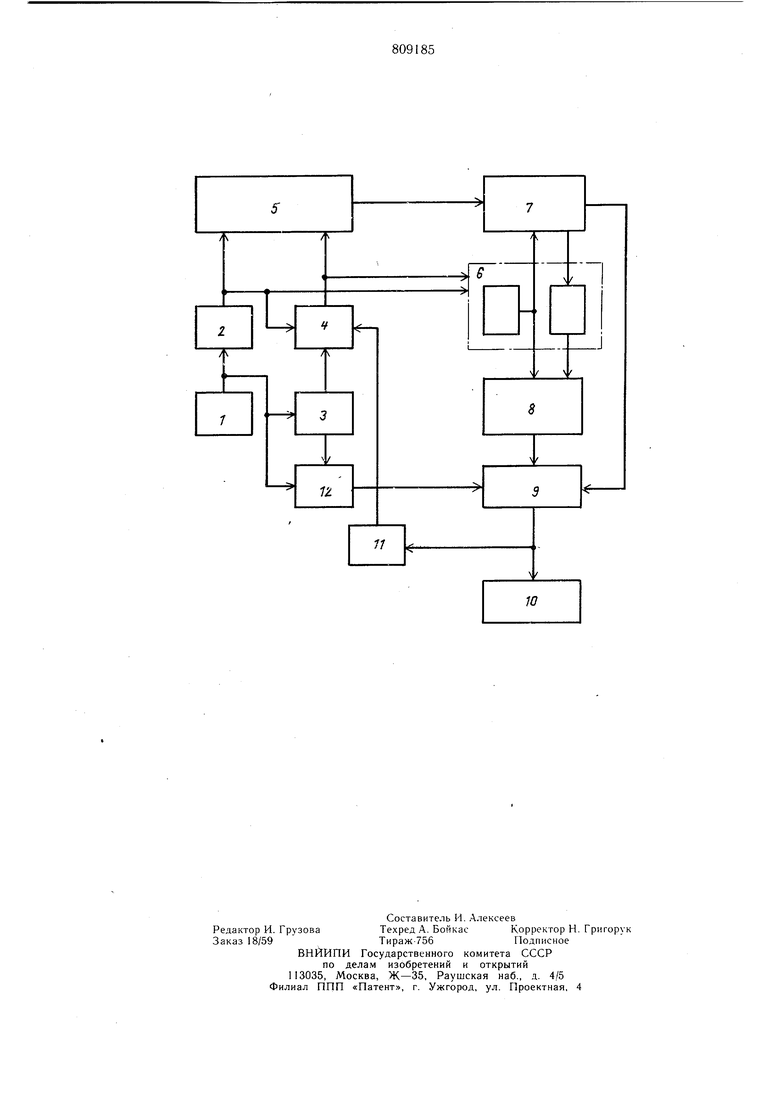

На чертеже изображена функциональная cxeivia устройства.

Она содержит пульт 1 управления, первый блок 2 памяти, генератор 3 импульсов, блок 4 управления, формирователь 5 адресов испытательных команд, формирователь 6 команд согласующий блок 7; блок 8 оценки результатов контроля, второй блок 9 памяти, блок 10 индикации, элемент И И, формирователь 12 сигнала отключения питания объекта контроля.

Устройство работает следующим образом.

Программа проверки с пульта 1 заносится в память блока 2. Проверяемая микросхема устанавливается в контактирующее устройство, расположенное на плате блока 7. По командам, поступающим из блока 2, блок 5 выбирает необходимые ячейки памяти контролируемой БИС, а блок 6 заносит контрольную информацию в регистр передачи информации, которая подается через блок согласования в проверяемую микросхему.

В устройстве остановка контроля происходит только при обнаружении ошибок сравнения во всех одновременно проверяемых микросхемах, что не требует повторения контрольных тестов для восстановления информации, потерянной при замене дефектных микросхем. Это объясняется тем, что результаты сравнения запоминаются блоком 9, выходы которого соединены со входами элемента И 11, выполняющего функции оценки совпадения сигналов ошибок контроля, выход которого соединен со входом блока 4. В данном устройстве только при обнаружении ошибок в процессе выполнения контрольного теста во всех одновремен но проверяемых микросхемах, т. е. при появлении единичных потенциалов на входах элемента И, с его выхода на вход логического блока подается сигнал низкого уровня, сигнализирующий о прекращении выполнения контрольного теста.

Блок 12 формирует сигнал на блокировку поступающих на микросхемы входных воздействий и снятие с них питающего напряжения по сигналу «Пуск устройства, что позволяет привести Б исходное состояние блок 9 переа началом проверки и хранить контрольную информацию до начала проверки новой партии микросхем. Это дает возможность организовать процесс контроля оптимальным образом относительно временных затрат.

Формула изобретения

Устройство для функционального контроля микроэлектронных узлов, содержащее блок управления, первый управляющий вход которого соединен с выходом первого блока памяти, информационным входом формирователя адресов испцтательных команд и первым информационным входом формирователя команд, тактовый вход - с первым выходом генератора импульсов, вход которого подключен к выходу пульта управления и входу первого блока памяти, выход блока управления соединен с управляющим

0 входом формирователя адресов испытательных команд и управляющим входом формирователя команд, выход формирователя адресов испытательных команд соединен с первым информационным входом согласующего блока, информационный выход ко торого соединен со вторым информационным входом формирователя команд, выходы которого соответственно соединены со входами блока сценки результатов контроля и вторым информационным входом соглаfl сующего блока, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит формирователь сигнала отключения питания объекта контроля, элемент И и второй блок питания, информационный вход которого соединен с

выходом блока оценки результатов контроля, управляющий вход - с управляющим выходом согласующего блока, выходы через элемент И - со вторым управляющим входом блока управления, а установочный вход - с выходом формирователя сигнала отключения питания объекта контроля, управляющий вход которого подключен к выходу пульта управления, а тактовый вход - ко второму выходу генератора импульсов.

5Источники информации,

принятые во внимание при экспертизе

1.Электроника № 23, 1973, с. 9-10.

2.Электронная промышленность, 1977, вып. 2, с. 20-24 (прототип)..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля интегральных микросхем памяти | 1983 |

|

SU1144154A1 |

| Аппаратура для автоматического контроля абонентских участков | 1978 |

|

SU769755A2 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля электронных изделий | 1978 |

|

SU951323A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

Авторы

Даты

1981-02-28—Публикация

1978-11-27—Подача