Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быт использовано в контрольно-испытательной аппаратуре, например, в пулте электротермотренировки постоянны запоминающих устройств (ПЗУ).

Цель изобретения - повьшение надежности и быстродействия устрой- ства.

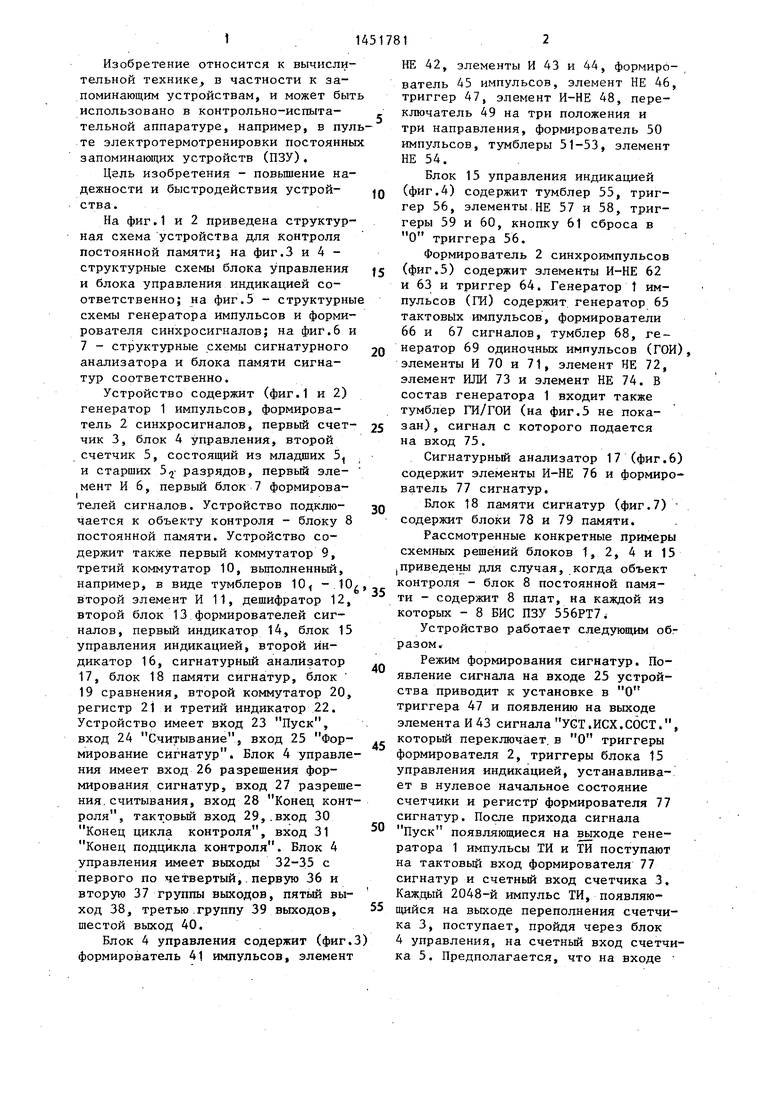

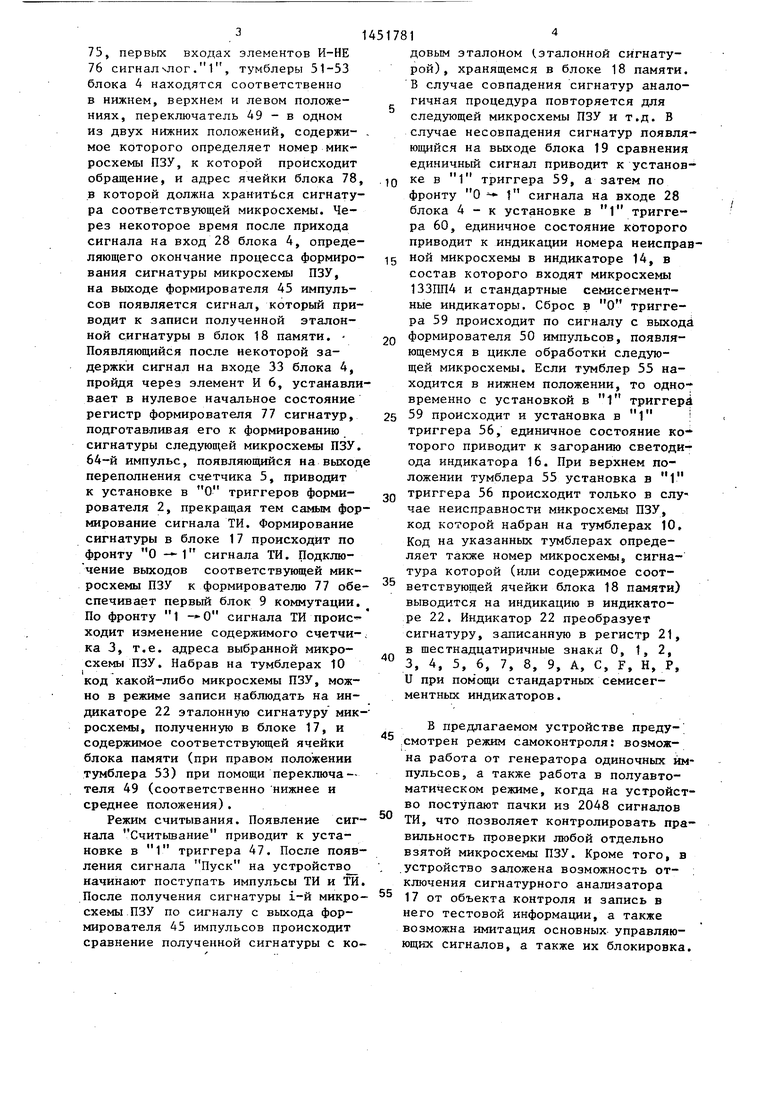

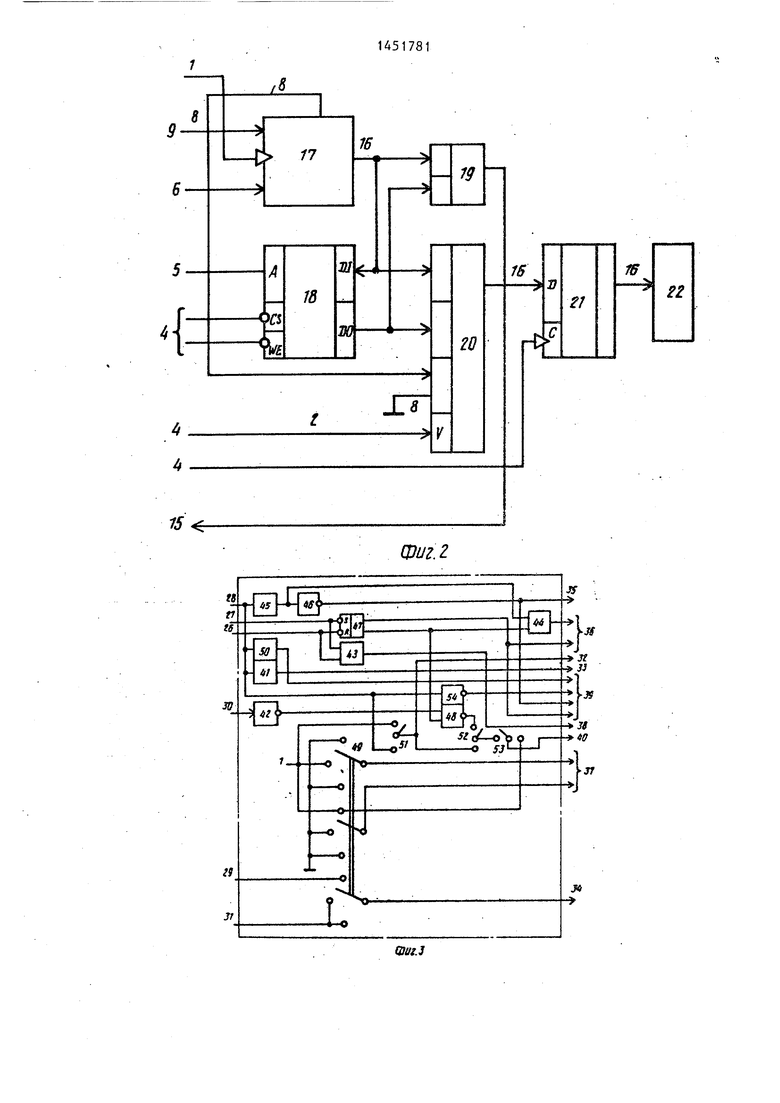

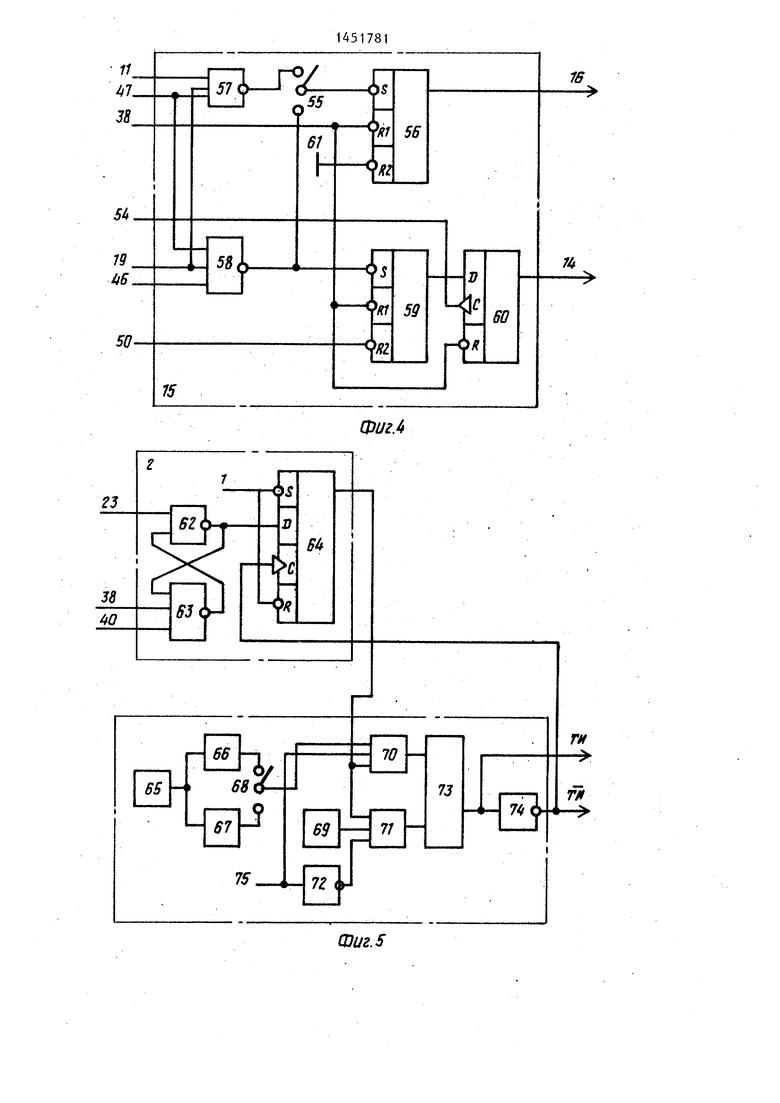

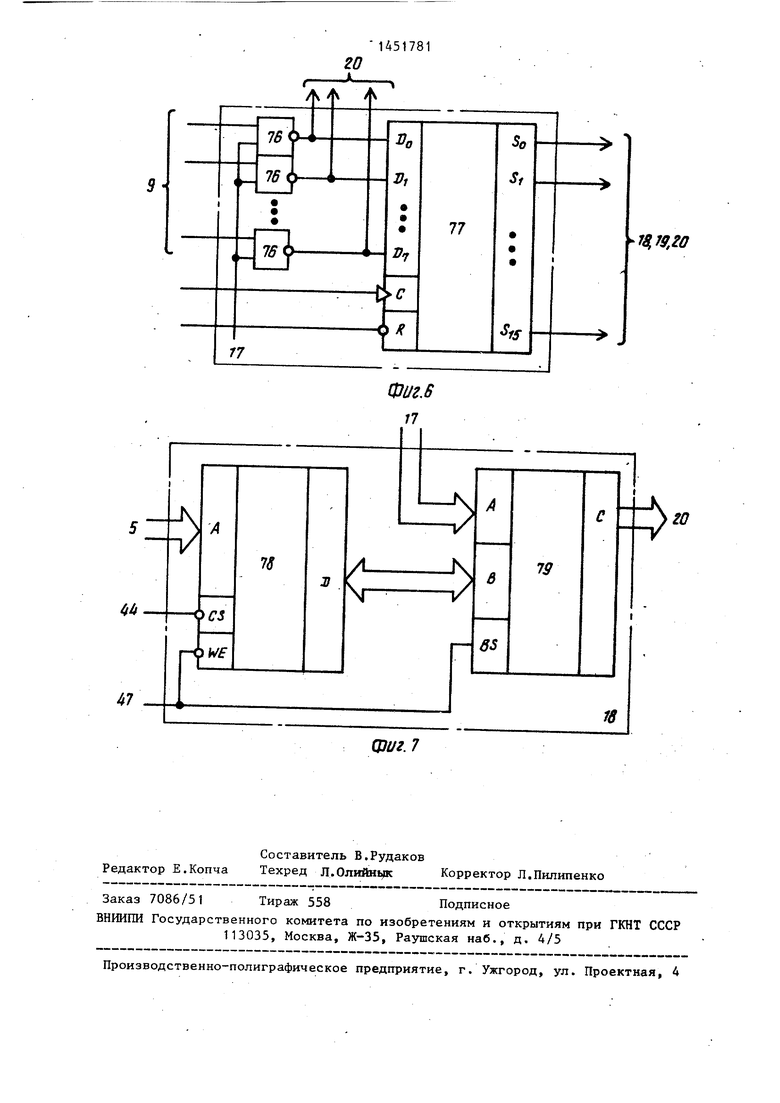

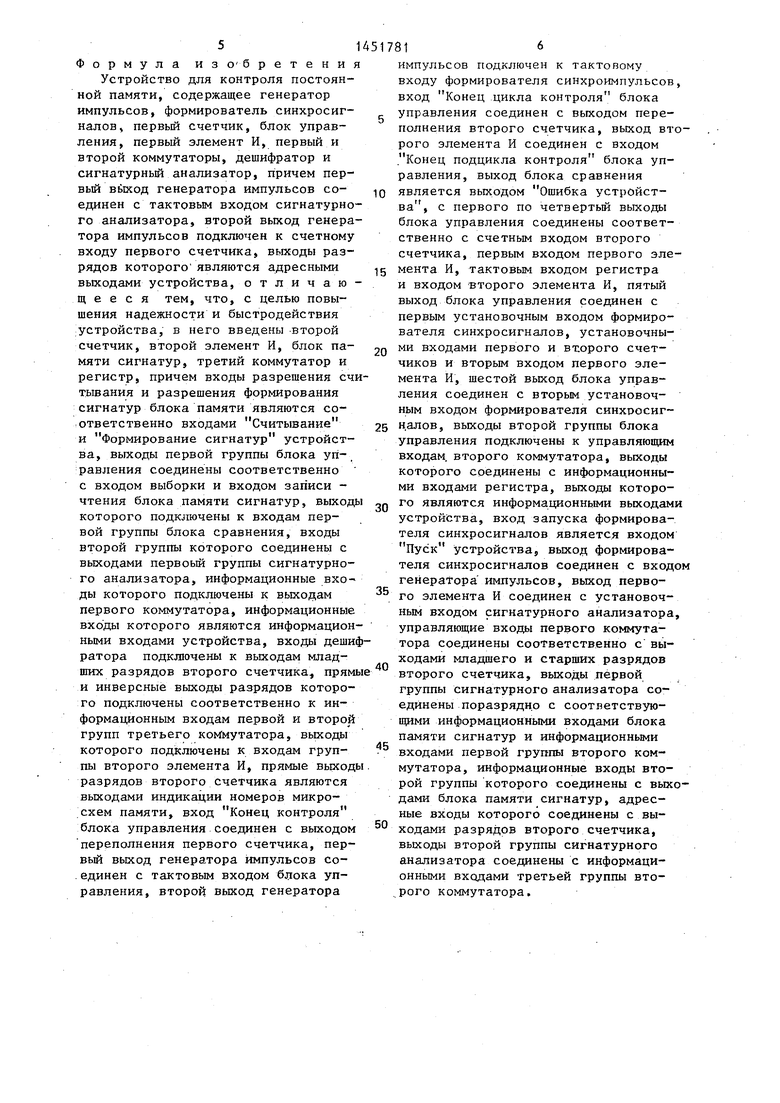

На фиг.1 и 2 приведена структурная схема устройства для Контроля постоянной памяти; на фиг.З и 4 - структурные схемы блока управления и блока управления индикацией соответственно; на фиг.5 - структурны схемы генератора импульсов и формирователя синхросигналов; на фиг.6 и 7 - структурные схемы сигнатурного анализатора и блока памяти сигнатур соответственно.

Устройство содержит (фиг.1 и 2) генератор 1 импульсов, формирователь 2 синхросигналов, первый счет- чик 3, блок 4 управления, второй счетчик 5, состоящий из младших 5 и старших разрядов, первый эле- мент И 6, первый блок 7 формирователей сигналов. Устройство подклю- чается к объекту контроля - блоку 8 постоянной памяти. Устройство содержит также первый коммутатор 9, третий коммутатор 10, вьшолненный, например, в виде тзт блеров 10 б второй элемент И 11, дешифратор 12, второй блок 13 формирователей сигналов, первый индикатор 14, блок 15 управления индикацией, второй индикатор 16, сигнатурный анализатор 17, блок 18 памяти сигнатур, блок 19 сравнения, второй коммутатор 20, регистр 21 и третий индикатор 22. Устройство имеет вход 23 Пуск, вход 24 Считывание, вход 25 Фор- мирование сигнатур. Блок 4 управления имеет вход 26 разрешения формирования сигнатур, вход 27 разрешения, считывания, вход 28 Конец контроля, тактовый вход 29,.вход 30 Конец цикла контроля, вход 31 Конец подцикла контроля. Блок 4 управления имеет выходы 32-35 с первого по четвертый,. первую 36 и вторую 37 группы выходов, пятый выход 38, третью.группу 39 выходов, шестой выход 40. .

Блок 4 управления содержит (фиг.З формирователь 41 импульсов, элемент

НЕ 42, элементы И 43 и 44, формирователь 45 импульсов, элемент НЕ 46, триггер 47, элемент И-НЕ 48, переключатель 49 на три положения и три направления, формирователь 50 импульсов, тумблеры 51-53, элемент НЕ 54.

Блок 15 управления индикацией (фиг.4) содержит тумблер 55, триггер 56, элементы.НЕ 57 и 58, триггеры 59 и 60, кнопку 61 сброса в О триггера 56.

Формирователь 2 синхроимпульсов (фиг.5) содержит элементы И-НЕ 62 и 63 и триггер 64. Генератор 1 импульсов (ГИ) содержит, генератор 65 тактовых импульсов, формирователи 66 и 67 сигналов, тумблер 68, генератор 69 одиночных импульсов (гон элементы И 70 и 71, элемент НЕ 72, элемент ИЛИ 73 и элемент НЕ 74. В состав генератора 1 входит также тумблер ГИ/ГОИ (на фиг.5 не показан), сигнал с которого подается на вход 75.

Сигнатурный анализатор 17 (фиг.6 содержит элементы И-НЕ 76 и формирователь 77 сигнатур.

Блок 18 памяти сигнатур (фиг.7) содержит блоки 78 и 79 памяти.

Рассмотренные конкретные примеры схемных решений блоков 1,2, 4 и 15 Iприведены для случая, когда объект контроля - блок 8 постоянной памяти - содержит 8 плат, на каждой из которых - 8 БИС ПЗУ 556РТ7

Устройство работает следующим обг разом.

Режим формирования сигнатур. Появление сигнала на входе 25 устройства приводит к установке в О триггера 47 и появлению на выходе элемента И 43 сигнала УСТ.ИСХ.СОСТ. который переключает, в О триггеры формирователя 2, триггеры блока 15 управления индикацией, устанавливает в нулевое начальное состояние счетчики и регистр формирователя 77 сигнатур. После прихода сигнала Пуск появляющиеся на выходе генератора 1 импульсы ТИ и ТИ поступают на тактовый вход формирователя 77 сигнатур и счетный вход счетчика 3. Каж,цый 2048-й импульс ТИ, появляющийся на выходе переполнения счетчика 3, поступает, пройдя через блок 4 управления, на счетньй вход счетчика 5. Предполагается, что на входе

75, первых входах элементов И-НЕ 76 сигнал лог . 1 , тумблеры 51-53 блока 4 находятся соответственно в нижнем, верхнем и левом положениях, переключатель 49 - в одном из двух нижних положений, содержи- мое которого определяет номер микросхемы ПЗУ, к которой происходит обращение, и адрес ячейки блока 78, в которой должна храниться сигнатура соответствующей микросхемы. Через некоторое время после прихода сигнала на вход 28 блока 4, определяющего окончание процесса формирования сигнатуры микросхемы ПЗУ, на выходе формирователя 45 импульсов появляется сигнал, который приводит к записи полученной эталонной сигнатуры в блок 18 памяти. Появляющийся после некоторой задержки сигнал на входе 33 блока 4, пройдя через элемент И 6, устанавливает в нулевое начальное состояние регистр формирователя 77 сигнатур, подготавливая его к формированию сигнатуры следующей микросхемы ПЗУ. 64-й импульс, появляющийся на выход переполнения счетчика 5, приводит к установке в О триггеров формирователя 2, прекращая тем самым формирование сигнала ТИ. Формирование сигнатуры в блоке 17 происходит по фронту О - 1 сигнала ТИ. Подключение выходов соответствующей микросхемы ПЗУ к формирователю 77 обеспечивает первый блок 9 коммутации. По фронту 1 сигнала ТИ пронс- ходит изменение содержимого счетчика 3, т.е. адреса выбранной микросхемы ПЗУ. Набрав на тумблерах 10 код какой-либо микросхемы ПЗУ, можно в режиме записи наблюдать на индикаторе 22 эталонную сигнатуру микросхемы, полученную в блоке 17, и содержимое соответствующей ячейки блока памяти (при правом положении тумблера 53) при помощи переключателя 49 (соответственно нижнее и среднее положения).

Режим считывания. Появление сигнала Считьтание приводит к установке в 1 триггера 47. После появления сигнала Пуск на устройство начинают поступать импульсы ТИ и ТИ После получения сигнатуры i-й микросхемы ПЗУ по сигналу с выхода формирователя 45 импульсов происходит сравнение полученной сигнатуры с кодовым эталоном (эталонной сигнатурой), хранящемся в блоке 18 памяти. В случае совпадения сигнатур аналогичная процедура повторяется для следующей микросхемы ПЗУ и т.д. В случае несовпадения сигнатур появляющийся на выходе блока 19 сравнения единичный сигнал приводит к установ0 ке в 1 триггера 59, а затем по фронту О 1 сигнала на входе 28 блока 4 - к установке в 1 триггера 60, единичное состояние которого приводит к индикации номера неисправ5 ной микросхемы в индикаторе 14, в состав которого входят микросхемы 133ПП4 и стандартные семисегмент- ные индикаторы. Сброс в О триггера 59 происходит по сигналу с выхода

Q формирователя 50 импульсов, появляющемуся в цикле обработки следующей микросхемы. Если тумблер 55 находится в нижнем положении, то одновременно с установкой в 1 триггера

5 59 происходит и установка в 1 i триггера 56, единичное состояние ко торого приводит к загоранию светоди- ода индикатора 16. При верхнем положении тумблера 55 установка в 1

Q триггера 56 происходит только в случае неисправности микросхемы ПЗУ, код которой набран на тумблерах 10, Код на указанных тумблерах определяет также номер микросхемы, сигнатура которой (или Содержимое соответствующей ячейки блока 18 памяти) выводится на индикацию в индикаторе 22. Индикатор 22 преобразует сигнатуру, записанную в регистр 21, в шестнадцатиричные знаки О, 1, 2, 3, 4, 5, 6, 7, 8, 9, А, С, F, Н, Р, и при помощи стандартных семисег- ментных индикаторов.

0

5

В предлагаемом устройстве преду- ,смотрен режим самоконтроля: возможна работа от генератора одиночных импульсов, а также работа в полуавтоматическом режиме, когда на устройство поступают пачки из 2048 сигналов ТИ, что позволяет контролировать правильность проверки любой отдельно взятой микросхемы ПЗУ. Кроме того, в устройство заложена возможность отключения сигнатурного анализатора 17 от объекта контроля и запись в него тестовой информации, а также возможна имитация основных управляю- ющих сигналов, а также их блокировка.

Формула из О б р е т е н и я Устройство для контроля постоянной памяти, содержащее генератор импульсов, формирователь синхросигналов, первьй счетчик, блок управления, первый элемент И, первый и второй коммутаторы, дешифратор и сигнатурньй анализатор, причем первьй вькод генератора импульсов соединен с тактовым входом сигнатурного анализатора, второй выход генератора импульсов подключен к счетному входу первого счетчика, выходы разрядов которого являются адресными выходами устройства, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены второй счетчик, второй элемент И, блок памяти сигнатур, третий коммутатор и регистр, причем входы разрешения считывания и разрешения формирования сигнатур блока памяти являются соответственно входами Считывание и Формирование сигнатур устройства, выходы первой группы блока управления соединены соответственно с входом выборки и входом записи - чтения блока памяти сигнатур, выходы которого подключены к входам первой группы блока сравнения, входы второй группы которого соединены с выходами первоый группы сигнатурного анализатора, информационные входы которого подключены к выходам первого коммутатора, информационные входы которого являются информационными входами устройства, входы дешифратора подключены к выходам младших разрядов второго счетчика прямы и инверсные выходы разрядов которого подключены соответственно к информационным входам первой и второй групп третьего коммутатора, выходы которого подключены к входам группы второго элемента И, прямые выходы разрядов второго счетчика являются выходами индикации номеров микросхем памяти, вход Конец контроля блока управления соединен с выходом переполнения первого счетчика, первьй выход генератора импульсов со- .единен с тактовым входом блока управления, второй выход генератора

5

0

5

0

5

0

5

0

импульсов подключен к тактовому входу формирователя синхроимпульсов, вход Конец цикла контроля блока управления соединен с выходом переполнения второго счетчика, выход второго элемента И соединен с входом Конец подцикла контроля блока управления, выход блока сравнения является выходом Ошибка устройства, с первого по четвертьй выходы блока управления соединены соответственно с счетным входом второго счетчика, первым входом первого элемента И, тактовым входом регистра и входом второго элемента И, пятый выход блока управления соединен с первым установочным входом формирователя синхросигналов, установочными входами первого и второго счетчиков и вторым входом первого элемента И, шестой выход блока управления соединен с вторым установочным входом формирователя синхросигналов, выходы второй группы блока управления подключены к управляющим входам, второго коммутатора, выходы которого соединены с информационными входами регистра, выходы которого являются информационными выходами устройства, вход запуска формирователя синхросигналов является входом Пуск устройства, выход формирователя синхросигналов соединен с входом генератора импульсов, выход первого элемента И соединен с установочным входом сигнатурного анализатора, управляющие входы первого коммутатора соединены соответственно с выходами младшего и старших разрядов второго счетчика, выходы первой группы сигнатурного анализатора соединены поразрядно с соответствующими информационными входами блока памяти сигнатур и информационньми входами первой группы второго коммутатора, информационные входы второй группы которого соединены с выходами блока памяти сигнатур, адресные входы которого соединены с выходами разрядов второго счетчика, выходы второй группы сигнатурного анализатора соединены с информационными входами третьей группы вто- .рого коммутатора.

фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для обучения построению логических структур | 1986 |

|

SU1449990A1 |

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Сигнатурный анализатор | 1985 |

|

SU1363210A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

Изобретение относится к вычислительной технике и может быть использовано в контрольно-испытательной -аппаратуре, например в пульте элек- ш тротермотренировки постоянных запоминающих устройств. Цель изобретения - повышение надежности и быстродействия устройства. Устройство содержит генератор 1 импульсов, формирователь 2 синхросигналов, первый 3 и второй 5 счетчики, блок 4 управления, первый 6 и второй-11 элементы И, блоки 7 и 13 формирователей сигналов, коммутаторы, дешифратор 12, индикаторы, блок 15 управления инди-. кацией, сигнатурный анализатор,блок памяти сигнатур, блок сравнения, регистр. Устройство работает в режимах формирования сигнатур, считьюания и самоконтроля. 7 ил. $ Б-Г1РЧ п hllMLhD (Л СП 00

31

38

54

79 «ff.

75

и

S

Фиг. 5

Фиг.4

18,19.го

Щи г л

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU968856A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-01-15—Публикация

1987-03-06—Подача