I Изобретение относится к вычисли тельной технике. Известно устройство для контроля блоков памяти, в котором генера ция эталонных данных и адресация . проверяемого блока памяти осуществ ляется блоком управления, вырабатывающим совокупность команд специального назначения, определяющих программу теста для проверки блока памяти, причем блок управления позволяет формировать специальные для данного типа блоков памяти тяжелые кодовые последовательности и адресные переходы il.. . Недостатком этого устройства яв ляется однозначность определения работоспособности проверяемого бло ка памяти для решения поставленной задачи по принципу годен-брак- С по мощью этого устройства невозможно также проводить достоверные испытания современных больших интегральных микросхем запоминающих устройст так как отсутствует возможность создавать внешние условия проверки характерные для проявления дефектов. Наиболее близким техническим решением к изобретению является устро ство для контроля блоков памяти, содержащее генераторы импульсов, подключенные к первому блоку управления, последовательно соединенные формирователи управляющих сигналов входы первого из которых соединены с выходами первого блока управления и генераторов импульсов, а выход второго формирователя управляющих сигналов подключен к первому выходу устройства-, вход .которого соединен с входом одного из генераторов импульсов, блок питания и дат чик температуры, выходы которых подключены соответственно к второму и третьему выходам устройства-, второй блок управления, выходы кото рого соединены с входом триггера, подключенного к третьему блоку управления, печатающий блок, пульт управления, соединенный с первым и вторым блоками управления, счетчи ки, информационные которых подключены соответственно к управляющим входам формирователей управляющих сигналов, блока питания, дат чика температуры и информационным входам печатающего блока, управляющие входы и выходы счетчиков соединены с выходами и входами второго блока управления, а выход третьего блока управления соединен с управляют щим входом печатающего блока f2j. Это устройство устанавливает пригодность проверяемой памяти для применения в заданных условиях эксплуатации и позволяет оценивать его работоспособность по следующим параметрам: временные соотношения и амплитуда управляющих сигналов, частота обращения, напряжения питания, температурный диапазон Однако это устройство не позволяет проводить испытания блоков памяти с требуемой степенью достоверности. Это объясняется тем, что тенденция к повьш1ению быстродействия, информационной емкости и увеличению плотности компоновки современных больших интегральных микросхем запоминающих устройств (БИС ЗУ) приводят к появлению новых типов дефектов, которые возникают при функционировании элементов субмикронных размеров в монолитном кристалле. Специфика контроля БИС ЗУ состоит в том, что необходимо выявить не только явные отказы элементов, входящих, в состав запоминающего устройства, но и дефекты, обусловленные паразитными связями, которые возникают в процессе функционирования при изменении внешних воздействий, в частности, величины питающих напряжений. Известное устройство осуществляет построение области работоспособности по точкам при фиксированных значениях напряжения питания. Такой режим испытания не гарантирует работоспособности проверяемой памяти в условиях, когда будет происходить плавное изменение уровня напряжения питания даже в допустимом диапазоне, что имеет место при нестабильности источника питания или постепенном выходе его из строя. Изменение питания в процессе функционирования БИС ЗУ приводит к перезаряду паразитных емкостей, изменению параметров протекающих токов, возникают сбои в работе усилителей записи-считывания и происходит потеря информации в ячейках памяти. Кроме того, известное устройство в процессе построения области рабо3

тоспособности не оценивает такой параметр как время, в течении которого можно гарантировать работоспособность проверяемой памяти в случае катастрофического отказа источника питания, когда он выходит из строя и происходит постепенный разряд фильтрующих емкостей-. Такой параметр является важным в том cлyf чае, когда необходимо избежать потери информации, записанной в память. Величина времени хранения информации позволяет рассчитать схему аварийного подключения резервного истоника питания или произвести перезапись информации в другой массив памяти.

Целью изобретения является повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство для контроля интегральных микросхем памяти, содежаа;ее генераторы импульсов, подключенные к первому блоку управления, последовательно соединенные первый и второй формирователи управляющих сигналов, входы первого из которых соединены с выходами генераторов импульсов и одним из выходов первого блока управления, выход второго формирователя управляющих сигналов является первым выходом устройства, первым входом которого является вход одного из генераторов импульсов, программируемый блок питания и датчик температуры, выходы которых являются соответственно вторым и третьим выходами устройства, триггер, выход которого подключен к входу третьего формирователя управляющих сигналов, пульт управления, соединенный с первым и вторым блоками управления, первый счетчик и группы счетчиков, одни из вьпсодов которых подключены соответственно к управляющим входам первого и второго формирователей управляющих сигналов, программируемого блока питания и датчика температуры и к информационному входу печатающего блока, один из управляющих входов которого соединен с выходом третьего формирователя управляющих сигналов, выходы второго блока управления подключены соответственно к входам триггера, первого счетчика, счетчиков групп, одному из входов первого

4415А4

блока управления и другому управляющему входу печатающего блока, а входы - к другим выходам первого счетчика и счетчиков групп, введены регистр, элемент ИЛИ, элементы И-Шта и второй счетчик, тактовый вход которого соединен с одним из выходов первого формирователя управляющих сигналов, информационный

10 вход - с выходом регистра, вход управления параллельной записью с выходом элемента ИЛИ, информационный выход - с информационным входом печатающего блока, выход переноса 15 с одним из входов элемента И-ИЖ, выходы которых соединены с тактовыми входами счетчиков одной из групп, вход регистра и другие входы элемента ИЛИ и элементов И-ИЛИ подключены к одним из выходов второго блока управления.

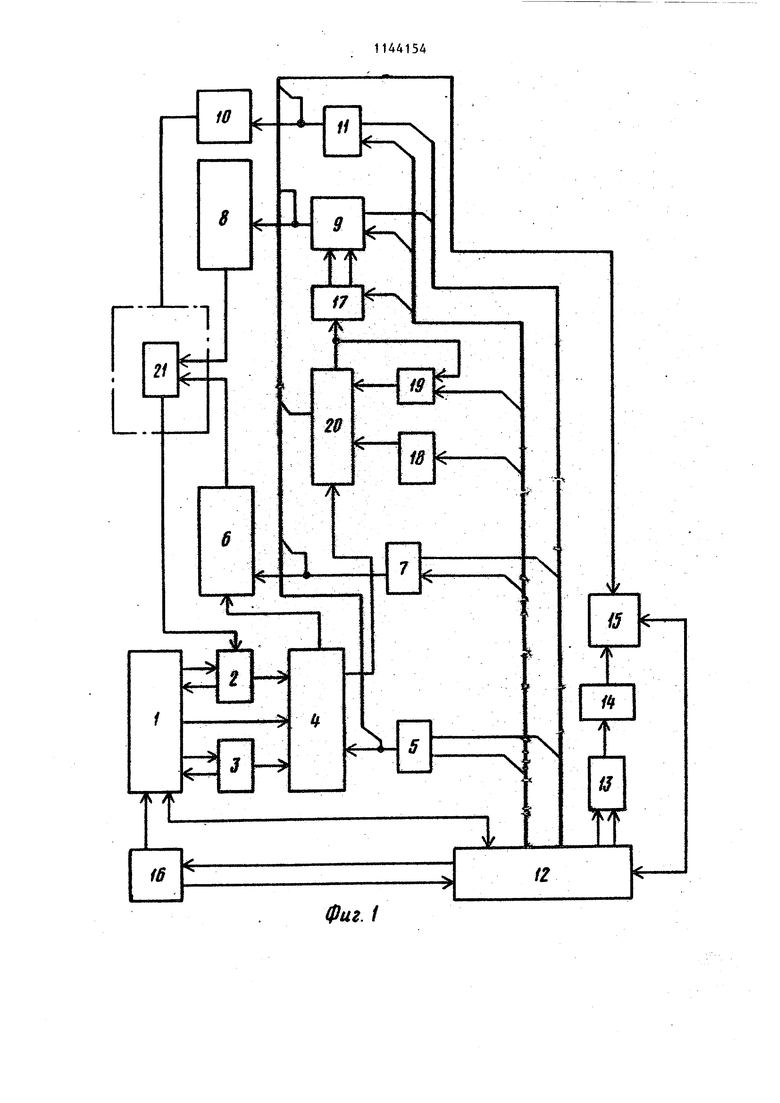

На фиг. 1 изображена структурная схема устройства для контроля интегральных микросхем памяти, на

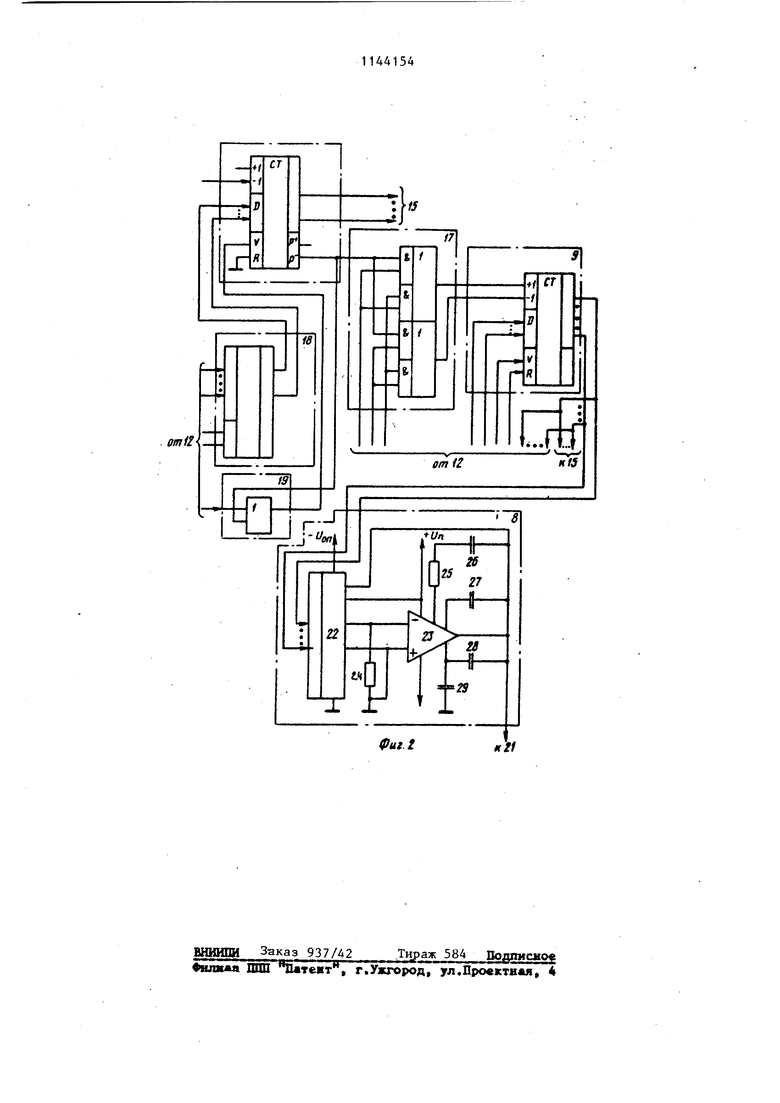

5 фиг. 2 - схема отдельных блоков устройства.

Устройство содержит (фиг. 1) первый блок t управления, генераторы 2 и 3 импульсов, первый формироваQ тель 4 управляющих сигналов, группу счетчиков 5, второй формирователь 6 управляющих сигналов, группу счетчиков 7, программируемый блок 8 питания, группу счетчиков 9, датчик 10 температуры, первый счетчик 11, второй блок 12 управления. Триггер 13, третий формирователь 14 управляющих сигналов, печатающий блок 15, пульт 16 управления, элементы

И-ИЛИ 17, регистр 18, элемент ИЛИ 19, второй счетчик 20.

Устройство подключается к контролируемой интегральной микросхеме 21 памяти.

Программируемь1й блок 8 питания (фиг. 2) содержит цифроаналоговый преобразователь 22, операционный усилитель 23, резисторы 24 и 25, конденсаторы 26-29.

Устройство работает следующим образом.

Для построения многомерных областей работоспособности микросхем памяти устройство имеет два режима функционирования: режим задания управляющих воздействий и режим тестирования.

В режиме задания управляющих воздействий из пульта 16 управления в блок 1 управления вводится программа генерации теста. Блок 12 управления в соответствии с программой также записанной с пульта 16 управления задает исходное значение параметров, определяяядах область работоспособности проверяемой микросхемы. Таким образом, временное положение и длительность управляющих сигналов, которые будут реализованы формирователем 4, соответствуют кодам, занесенньм в счетчики 5 Амплитуда управляюпщх сигналов определяется кодами счетчиков 7. Зада ние температуры окружающей среды, когда проверяемая микросхема 21 загружена в термостат, осуществляется датчиком 10 температуры в соответствии с кодами счетчика 11. Исходный уровень напряжения тштания задается кодом счетчика 9, который записывается из блока 12 управления, при этом тактовые импульсы поступают на счетчики 9 через элементы И-ИЖ 17.

Для реализации изменения напряжения питания в режиме тестирования блок 12 управления задает число К, которое заносится в регистр 18 в двоичном коде, а затем через элемент ИЛИ 19 записывает его в счетчик 20. Значение числа К определяется из условия, что счетчик 9 за время прохождения проверякицего теста должен изменить свое состояние на Р импульсов. Соответственно изменяется и напряжение питания, задаваемое блоком 12.

После установления исходных условий блок 12 управления по команде с пульта 16 управления переводит триггер 13 из 1 в О. При этом формирователь 14 разрешает работу печатающего блока 15, который фиксирует исходное состояние счетчиков 5, 7, 9, 11, 20. После чего триггер 13 вновь переводится в 1.

В режиме тестирования блок 1 управления в соответствии с введенной программой вьфабатьгоает совокупность управляющих сигналов для генераторов 2 и 3 импульсов и формирователя 4 управляющих сигналов. Данная совокупность управляющих сигналов определяет реализацию теста проверки и задает код данных, адрес и род работы для проверяемой микросхемы в каждом цикле обращения. Генератор 2 импульсов формирует эталонный код данных для записи в проверяемую микросхему 12 или для сравнения со cчитanны ш из микросхемы 21 данньми. Результаты сравнения считанного и эталонного кодов

поступают в блок 7 управления. Генератор 3 импульсов формирует код адреса проверяемой микpocxe ш 21. Информация о СОСТОЯНИИ счетчика адреса генератора 3 поступает в

блок 1 управления, задавая условные переходы в алгоритме проверяющего теста. Формирователь 4 управляющих сигналов в зависимости от заданного блоком 1 управления режима формирует временную диаграмму

записи, считывания или регенерации. I

С момента начала и до окончания генерации теста проверки импульсы

Выбор микросхем (ВМ) (наличие импульса соответствует обращению к проверяемой микросхеме) поступают с выхода форш1рователя 4 на тактовый вход 1 счетчика 20. После каждых к импульсов счетчик 20 оказьгоается в состоянии нуль и на выходе обратного переноса появляется импульс, КОТ01И11Й через элемент ИЛИ 19 поступает на вход параллельНой записи счетчика 20 и осуществляет очередную запись числа К из регистра 18 в счетчик 20. Если за-.дан рея;ш4 изменения напряжения питания, то импульс переноса с выхода счетчика 20 поступает через элементы И-ИЛИ 17 (фиг. 2). на один из тактовых входов счетчика 9. В результате состояние счетчика 9 изменится на Р импульсов за время проверки микросхемы даиньм тестом, а напряжение питания будет линейно изменяться относительно исходного в сторону увеличения или уменьшения. Блок 16 управления информирует блок 12 управления о результате тестирования. По окончании теста или в случае отказа проверяемой микросхемы блок 12 управления останавливает работу блока 1 управления и через триггер 13 и формирователь 14 разрешает работу печатаю«чего блока 15, который фиксирует состояние счетчика 5, 7, 9, 11 и 20 в момент останова. Блок 12 управления изменяет исходное состояние счетчиков 5, 7, 9, 11 и содержимое регистра 18, меняя тем самым значения параметров управляющих воздействий. В свою очередь счетчики информируют блок 12 управления о своем текущем состоянии, формируя условия переходов алгоритма построения области работоспособности.

Таким образом, предлагаемое устройство дпя контроля интегральных Ш11{росхем памяти позволяет реализовать режим изменения напряжения питания 1фоверяемой микросхемы зо время прохождения проверяемого тес та, что повышает достдверность контроля интегральных микросхем памяти

в процессе построения многомерных областей работоспособности, так как создаются условия для проявления скрытых дефектов интегральных струкТУР, которые могут щ ивести к нарушени}Ш исправного функционирования запоминающего устройстваt Количественнаяоценка интервала времени, в течении которого проверяемая микросхема сохраняет информацию при отказе источника питания, расщиряет область применения предлагаемого устройства, поскольку этот параметр является необходимым в том случае

когда требуется избежать потери

информации при аварийном отключении питания.

Фиг. f

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ ШКРОСХЕМ ПАМЯТИ, содержащее генераторы импульсов, подключенные к первому блоку управления , последовательно соединенные первьй и второй формирователи управляющих сигналов, входы первого из которых соединены с выходами генераторов импульсов и одним из выходов первого блока управления, выход второго формирователя управляютЕих сигналов является первым выходом устрой ства, первым входом которого является вход одного из генераторов импульсов, программируемый блок питания и датчик температуры-, вккоды которых являются соответственно вторым и третьим выходами устройства, триггер, выход которого подключен к входу третьего формирователя управляющих сигналов, пульт управления , соединенный с первым и вторым блоками управления, первый счетчик и группы счетчиков, одни из выходов которых подключень соответственно к управлякщим вхЬдам первого и второго формирователей управляющих сигналов , программируемого блока пита- i ния и датчика температуры и к информационному входу печатающего блока, один из управляющих входов которого соединен с выходом третьего формирователя управляющих сигналов, выходы второго блока управления подключены соответственно к входам триггера, первого счетчика, счетчиков групп, одному из входов первого блока управления и другому управляющему входу печатающего блока, а входы - к другим выходам первого счет(Л С чика и счетчиков групп, о т л и- . чающееся тем, что, с целью повьшения достоверности контроля, в него введены регистр, элемент ИЛИ, элементы И-ИЛИ и второй счетчик, тактовый вход которого соединен с одним из выходов первого формирователя управлякшщх сигналов, информационн вход - с выходой регистра, rtb вход управления параллельной запи7 СЬЮ - с выходом элемента ИЖ, информационньй.выход - с информационным входом печатающего блока, выход переноса - с одними, из входов элемента ИЛИ и элементов И-ИЛИ, выхода которьпЕ соединены с тактовыми входами счетчиков одной из групп, вход регистра и другие входы элемента ИШ и элементов И-ИЛИ подключены к одним из выходов- второго блока управления..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3751649, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля блоков памяти | 1976 |

|

SU646375A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-03-07—Публикация

1983-04-11—Подача