Изобретение относится к аналогоцифровой вычислительной технике и может быть использовано в гибридной вычислительной системе для сбора, предварительной обработки информации и передачи ее с сеточной электро модели в цифровую вычислительную машину. Известно устройство сбора информа ции, включающее входной коммутатор, блоки развязки, аналого-цифровые пре образователи и выходной коммутатор, позволяющие снимать ранение с электр модели, преобразовать его и передать в цифровую вычислительную машину l Однако это устройство не обеспечивает достаточную точность работы и быстродействие. Наиболее близким к предлагаемому по технической сущностей является коммутатор сеточной модели, содержа щий блок селекции, связанный с аналого-цифровыми преобразователями и дешифратором выборки, соединенным с блоком коррекции и блоком программного управления, соединенным с блоком управления, связанным с аналого-цифровыми преобразователями, соединенными с ключами 2. Известный коммутатор также не Обеспечивает достаточную точность и быстродействие. Цель предлагаемого изобрете- ния - повышение точности. Поставленная цель достигается тем, что в устройство, содержгоцее блок селекции, выходы которого соединены с первыми входами аналогоцифровых преобразователей, вторые входы которых подключены соотьетственно к первому и второму вь ходам блока управления, вход блока селекции является входом устройства, регистры, выходной коммутатор, выход которого является выходом устройства, введены регистры сдвига, счетчики, элементы И и первый и второй триггеры, первые входы которых соединены с третьим выходом блока управления, второй вход каждого из триггеров подключен к первому, выходу одноиме ного аналого-цифрового преобразователя, выходы первого триггера соединены с первыми входами первого и второго элементов И, вторые входы которых подключены ко второму выходу первого аналого-цифрового преобразователя, второй выход которого соединен с первым входом

блока управления и с первым входом первого регистра сдвига, второй вход которого подключен к выходу второго элемента И, выход перйого элемента И через первый счетчик соединен с первым входом выходного коммутатора,, выходы второго триггера подключены к первым входам третьего к четвертого элементов И, вторые входы которых соединены с выходом второго аналого-цифрового преобразователя, второй выход которого под ключен ко второму входу блока управления и к первому входу второго регистра сдвига, второй вход которюго соединен с выходом четвертого элемента И, выход третьего элемента И через второй счетчик подключен ко второму входу выходного коммутатора, выходы первого и второго регистров сдвига соединены со входами одноименных регистров, выходы которых подключены соответственно к третьему и четвертому входам выходного коммутатора, управляющий вход которого соединен с четвертым выходом блока управления, пятый выход которого подключен к управляющем входу блока селекции.

Кроме того, блок управления содержит дешифраторы, узел коррекции, счетчики, регистры, элемент памяти, коммутатор и генератор импульсов, первый выход которого непосредственн а .второй - через первый счетчик соединены со входами первого дешифратора, выходы которого подключены к первым входам второго дешифратора, регистров и ком лутатора, выход которого соединен со вторым входом первого регистра, ВЕЛХОД которого подключен ко входу элемента памяти, выходы которого соединены соответственно со вторыми входами коммутатора и второго регистра, выходы которого подключены соответственно ко второму входу второго дешифратора,входу третьего дешифратора, третьему входу коммутатора и к первой группе входов узла коррекции, вторая группа входов которого соединена с группой выходов второго дешиф ратора, первый выход которого подключен к первому входу второго счетчика, выход которого соединен со входом четвертого дешифратора, первый и второй выходы которог являются одноименными выходами блока а третий выход четвертого дешифратора подключен ко второму входу второго счетчика и к четвертому входу коммутатора, группа входов которюго соединена с первой группой выходов узла коррекций, вторая группа выходов которого подключена к группе входов третьего-дешифратора, выход которого является пятым выходом блока управления, первым и вторым входами которого являются соответственно третий и четвертый входы узла коррекции

второй и третий выходы второго дешифратора являются соответственно третьим и четвертым выходами блока управления.

Причем узел коррекции содержит регистры. Элементы сравнения, счетчи и элемент ИЛИ, входы которого являются соответстпеннб третьим и четвертым входами узла коррекции, выход элемента ИЛИ соединен с первым вхо|дом первого регистра, выход которого подключен к первому входу первого элемента сравнения, второй вход которого подключен к выходу второго регистра, второй вход первого регистра и первые входы второго и третьего регистров являются первой группой входов узла, второй группой входов которого являются третий вход первого регистра, вторые входы второго и третьего регистров и первый вход счетчика, второй вход которого соединен с выходом второго элемента сравнения, входы которого подключены соответственно к выходам счетчика и третьего регистра, выходы элементов сравнения являются первой группой выходов узла, второй группой выходов которого являются выходы первого и второго регистров,

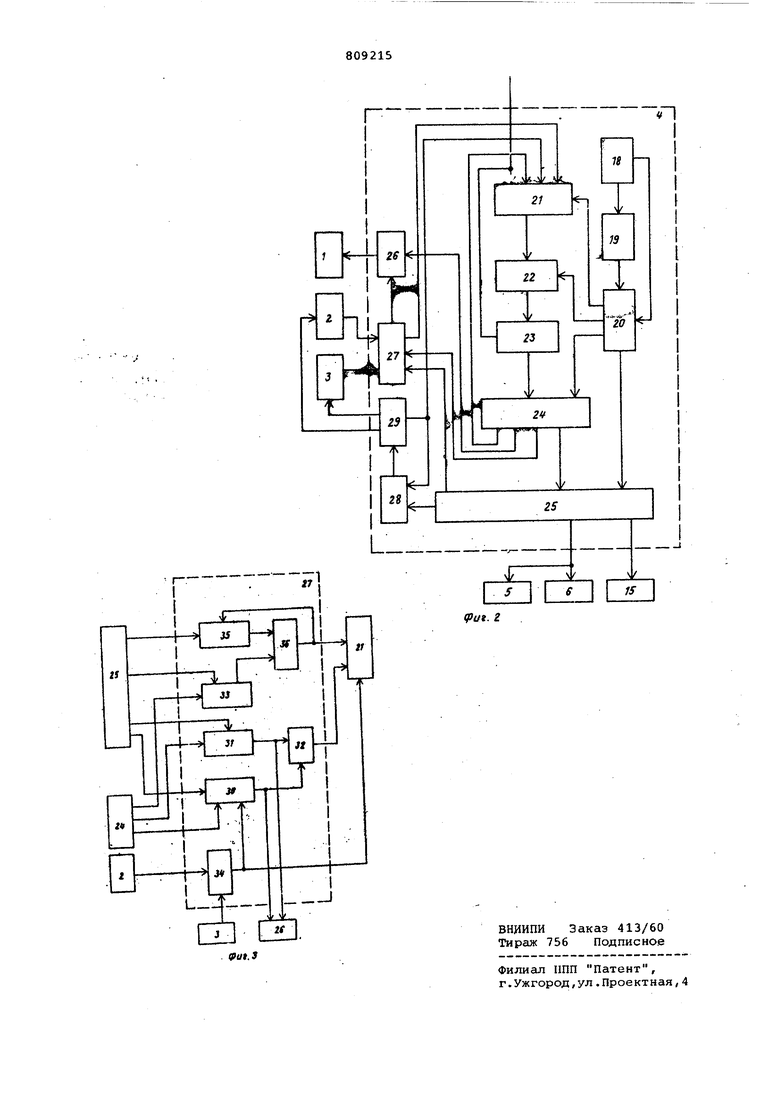

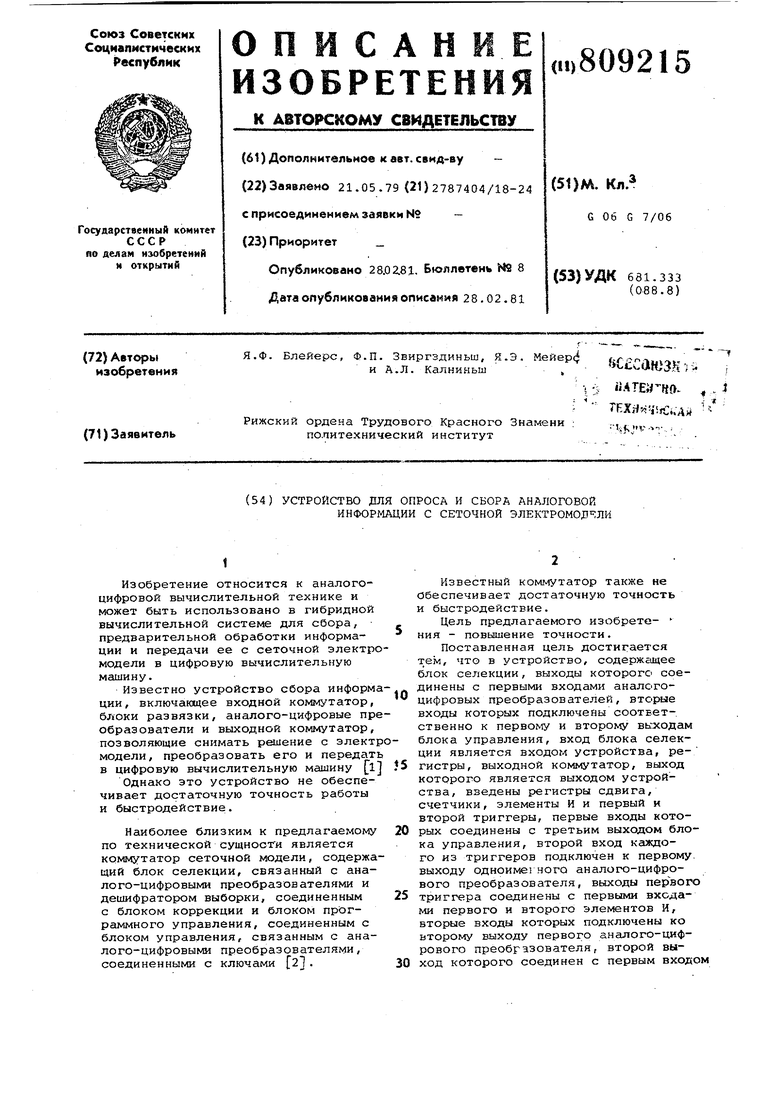

На фиг. 1 изображено ус:ройство, функциональная схема;на фиг. 2 - схема блока управления; на фиг. 3 - схема узла коррекции.

Устройство содержит блок 1 селекции , выходы которого соединены со входами аналого-цифровых преобразователей 2 и 3, управляющие входы которых подключены к первому и второму выходам блока 4 управления, связанного третьим выходом с блоком 1 селекции . Входы блока 4 управления подключены к первым выходам аналого-цифровых преобразователей (АЦП) 2 и 3, к первым входам триггеров 5 и б и регистров 7 и 8 сдвига. Вторые входы триггеров 5 и б связаны с четвертым выходом блока 4 управления. Второй .выход аналого-цифрового преобразова;теля 2 соединен с первыми входами первого и второго элементов И 9 и 10 Второй выход аналого-цифрового преобразователя 3 связан с первыми входами третьего и четвертого элемента И 11 и 12. Вторые входы элементов И 9 и 10, 11 и 12 подключены соответственно к выходам триггеров 5 и 6 Выходы элементов И 10 и 12 соединены соответственно со счетчика &1 13, 14 (порядка), связанными с выходным коммутатором 15. Выходы элементов И 9 и 11 соответственно подключены ко входам регистров 7 и 8 сдвига,связанных с регистрами 16 и 1 (числа), соединенными выходами с выходным коммутатором 15, подключенным к блоку 4 управления. Количество .аналого-цифровых преобразователей в общем случае может быть п. Для упрощения чертежа и описания принято

два аналого-цифровых преобразователя

Блок 4 управления (фиг.2) содержи генератор 18 импульсов, первый выход которого соединен со входом счетчика 19, выход счетчика 19 подключен к первому входу дешифратора 20, второй вход которого связан с вторым выходом генератора 18. Первый выход деширатора 20 соединен с вторым входом коммутатора 21, связанного выходом с первым входом регистра 22. Второй вход регистра 22 подключен к второму 1ВЫХОДУ дешифратора 20, выход - к первому входу элемента 23 памяти,второй вход которого соединен с четвертым входом коммутатора 21. Выход элемента 23 памяти связан с первым входом регистра 24, второй вход которого подключен к третьему выходу дешифратора 20, а первый выход - к первоNV входу коммутатора 21. Третий выход регистра 24 соединен с первым входом дешифратора 25, второй вход которого связан с четвертым выходом дешифратора 20. Первый выход дешифратора 25 соединен с первым входом дешифратора 26, второй вход которого связан с первым выходом узла 27 коррекции, а выход - с блоком 1 селекции. Второй выход узла 27 коррекции соединен с третьим входом коммутатора 21, а первый, второй, третий и четвертый входы подключены к первому выходу АЦП 2,первому выходу АЦП 3, второму выходу регистра 24 и второму выходу дешифратора 25 соответственно. Третий выход дешифратора 25 связан с первым входом счетчика 28, соединенного выходом с дешифратором 29, первый выход которого подключен к второму входу счетчика 28 и к пятому входу коммутатора 21, а второй и третий выходы. - к управляющим входам АЦП 2 и АЦП 3 соответственно. Четвертый выход дешифратора 25 соединен со входами триггеров 5 и 6, а пятый выход - со входом коммутатора 15.

Работу блока 4 управления синхронизируют импульсами, вырабатываемыми с помощью генератора 18, счетчика 19 и дешифратора 20. Узел 27 коррекции (фиг.З) содержит регистры 30 и 31, элемент 32 сравнения, регистр 33, элемент ИЛИ 34, счетчик 35 и элемент 36 сравнения.

Устройство для опроса и сбора аналоговой информации работает следующим образом.

Блок 1 селекции подключают к сеточной электромодели (не показана). Блок 4 управления и синхронизации и выходной коммутатор 15 соединяют с цифровой вычислительной машиной и ее блоком памяти (не показано).

Из. ЦВМ в.элемент 23 памяти записывают nporpaMT-iy работы устройства сбора аналоговой информации. Начальная команда из Ц Ш через коммутатор 21 поступает в регистр 22 адреса микрокоманд, который определяет первую микрокоманду в элементе 23 памяти. Микрокоманда из элемента

23пймяти считывается в регистр

24микрокоманд. G первого выхода регистра 24 микрокоманд по тактовому сигналу с дешифратора 20 на первый вход коммутатора 21 поступает сигнал, служащий для передачи адреса следующей микрокоманды в регистр

24микрокоманд. Со второго выхода регистра 24 микрокоманд на .третий вход узла 27 коррекции поступает код адреса узловой точки и по синхросиг5налам, поступсиощим с выхода дешифратора 25 микроопераций записывается в соответствующие регистры 30 и 31 (фиг.З). Кроме того, со второго выхода регистра 24 микрокоманд на

0 вход узла 27 коррекции записывают код времени запуска АЦП 2 и 3.

С третьего выхода регистра 24 микрокоманд по тактовому сигналу с дешифратора 20 на вход дешифратора

25микроопераций поступает код

5 микроопераций. Со второго выхода дешифратора 25 микроопераций на установочные входы триггеров 5 и 6 режима поступает сигнал-, устанавливая

их в 1 или О, в зависимости от

0 режима (с нормализацией или без нормализации результатов измерений). С первого выхода дешифратора 25 на вход дешифратора 26 поступает сигнал выборки и АЦП 2 и 3 оказываются подключенными к ранее выбранным точкам сеточной электромодели. С третьего выхода дешифратора 25 на вход счетчика 28 поступают синхроимпульсы, определяющие паузу времени между запусками АЦП 2

0 и 3. Когда содержимое счетчика 2о соответствует времени паузы между запусками АЦП 2 и 3, с выхода дешифратора запуска 29 на вход АЦП 2 и - 3 поступает сигнал Пуск АЦП.

5

Кроме того, с выхода дешифратора 29 на вход коммутатора 21 и на установочный вход счетчика 28 поступает сигнал, устанавливая счетчик в исходное состояние. После оконча0ния преобразования и нормализации результата по сигналу с выхода деимфратора 25 на вход коммутатора -15 поступает сигнал считывания результата в ЦВМ.

5

Из регистра 24 коды выбранных групп и адреса выбранной точки по сигналу записи от дииифратора 25 п ступшот на управляющие входы регистров 30, 31.

С выходов регистров 30, 31 коды

0 поступают на вход дешифратора 26 и входы элемента 32 сравнения кодов, где хранятся предыдущие значения кода выбранных групп и кода узловой точки. При ПС ступлении следу ощих

5

кодов предыдущее значение сравнива. ется с последующим на четность и нечетность. В случае четности или нечетности предыдущего и последую- Щ€;го значений кодов в коммутатор 21 с выхода элемента 32 сравнения поступает сигнал коррекции времени включения следу(ощей группы или узловой точки и запускается счетчик .28, который определяет интервалы времени между запуском ЛЦП 2 и 3. В случае следования четного кода за нечетным или нечетного за четным условие коррекции в коммутатор 21 не поступает.

Из регистра 24 по сигналу записи с дешифратора 25 в регистр 33 записывают опорный код.

S процессе съема решения с сеточnoti электромодели сигнал конца преобразования с выхода ЛЦП 2 поступает на вход ком гутатора 21 и вход регистра 30. С выхода последнего на вход дешифратора 26 выборки поступает сигн;.1Л подключения очередной узловой точки к АЦП 2. Сигнал конца преобразова5-:кя от АЦП 3 поступает через элемент ИЛИ 34 на вход коммутатора 21. С выхода дешифратора 25 на вход счетчика (времени паузы) 35 поступают синхроимпульсы: содержимое счетчика 35 срглвнивается элементом 36 сравнения и опорным кодом, хранящимся в регистре 33. При совпадении кодов с выхода элемента 35 сравнения на вход коммутатора 21 и на вход счетчика 35 поступает сигнал установления его-в :.сходное состояние. С выхода дешифратора 25 на вход счетчика 28 поступает сигнал запуска,и через задан HHII интервал задержки с выхода дешифратора 29 происходит запуск АЦП 2 ,

Сигнал окончания преобразования ЛЦП 3 через элемент ИЛИ 34 поступает на вход коммутатора 21 и на вход регистра 30. Формирование запуска АЦП 3 осуществляется в описанном выше порядке.

По окончании опроса группы с выхода регистра 24 на вход счетчика 31 поступает сигнал выборки следующей группы.

Предлагаемое устройство по сравнению с известным обеспечивает более высокую точность работы и быстродействие.

Формула изобретения

Устройство для опроса и сбора аналоговой информации с сеточной электромодели, содержащее блок селекции, выходы которого соединены с Первыми входами аналого-цифровых преобразователей, вторые входы которых подключены соответственно X первому и втором выходам блока

управления, вход блока селекции является входом устройства,регистры выходной коммут тор, выход которого является выходом устройства, с тличающееся тем, что, с целью повьиения точности, в устройство введены регистры сдвига, счетчики, элементыИ, первый и второй триггеры, первые входы которых соединены с третьим выходом блока управления, второй вход каждого из триггеров подключен к первому выходу одноименного аналогоцифрового преобразователя, выходы первого триггера соединены с пер,выми входами первого и второго элементов И, вторые входы которых подключены ко второму выходу первого аналого-цифрового преобразователя, второй выход которого соединен q первым входом блока управления и с первым входом первого регистра сдвига второй вход которого подключен к выходу второго элемента И, выход первого элемента И через первый счетчик соединен с первым входом выходного кoм yтaтopa, выходы второго триггера подключены к первым входам третьего и четвертого элементов И, вторые входы которых соединены с выходом второго аналого-цифрового преобразователя, второй выход которого подключен ко второму входу блока управления и к первому входу второго регистра сдвига, второй вход которого соединен с выходом четвертого элемента И, выход третьего элемента И через второй счетчик подключен ко второму входу выходного KOfvKviyTaTOpa, выходы первого и второго регистров сдвига соединены со входами одноименных регистров, выходы которых подключены соответственно к третьему и четвертому входам выходного коммутатора, управляющий вход которого соединен с четвертым выходо блока управления, плтый выход которого подключен к управлякщему входу блока селекции.

2. Устройство по П.1, о т л ичающееся тем, что блок управления содержит дешифраторы, узел коррекций, счетчики, регистры,элемент памяти, коммутатор и генератор импульсов, первый выход которого непосредственно, U второй - через первый счетчик соединены со входгьми. первого дешифратора, выходы которого подключены к первым входам второго дешифратора и коммутатора/ выход которого соединен со вторым входом первого регистра, выход которого подключен ко входу элемента памяти, .выходы которого соединены соответветственно со вторыми входами коммутатора и второго регистра, выходы которого соединены соответственно со вторыми входами коммутатора и второго регистра, выходы которого подключены соответственно ко второму входу второго дешифратора, входу третьего дешифратора, третьему входу коммутатора и к первой группе входов узла коррекции, вторая группа входов которого соединена с группой выходов второго дешифратора, первый выход которого подключен к первому входу второго счетчика, выход которого соединен со входом четвертого дешифратора, первый и второй выходы которого являются одноименными выходами блока а третий выход четвертого дешифратора подключен ко второму входу вторго счетчика и к четвертому входу коммутатора, группа входов которого соединена с первой группой выходов )узла коррекции, вторая группа выходо которого подключена к группе входов третьего дешифратора, выход которого является пятым выходом блока, первым и вторым входами которого являются соответственно третий и четвертый входы узла коррекции, второй и третий выходы второго де 11ифратора являются соответственно третьим и четвертым выходами блока.

3. Устройство по ПП.2 и 3, отличающееся тем, что узел коррекции содержит регистры, элементы сравнения, счетчик и элемент ИЛИ, входы которого являются соответственно третьим и четвертым входами узла, выход элемента ИЛИ соединен с первым входом парвого регистра, выход котор го подключен к первому входу первого элемента сравнения, второй вход которого подключен к выходу второго регистра, второй вход первого регистра и первые входы второго и третьего регистр являются первой группой входов узла, второй группой входов которого являются третий вход первого регистра, вторые входы второго и третьего регистров и первый вход счетчика, второй вход которого соединен с выходом второго элемента сравнения,входы которого подключены соответственн к выходам счетчика и третьего регистра, выходы элементов сравнения являются первой группой выходов узла, второй группоГ: выходов которого являйтся выходы первого и второго регистров.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 399882, кл. G 06 G 7/06, 1971.

2.Авторское свидетельство СССР по заявке Ь 2421907/18-24 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для съема информации с сеточной электромодели | 1980 |

|

SU962985A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Устройство для сбора аналоговой информации с сеточной электромодели | 1979 |

|

SU911547A1 |

| Устройство для контроля состояния объекта | 1983 |

|

SU1119055A1 |

| Цифровой анализатор спектра Уолша речевых сигналов | 1987 |

|

SU1425710A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для измерения температуры | 1984 |

|

SU1281921A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-21—Подача