1 . 13

Изобретение относится к вычислительной технике, а именно к гибриднь м вычислительным устройствам для длительного, быстрого и точного интегрирования произвольно меняющихся аналоговых напряжений.

Целью изобретения является повьше- ние точности интегрирования и быстродействия устройства.

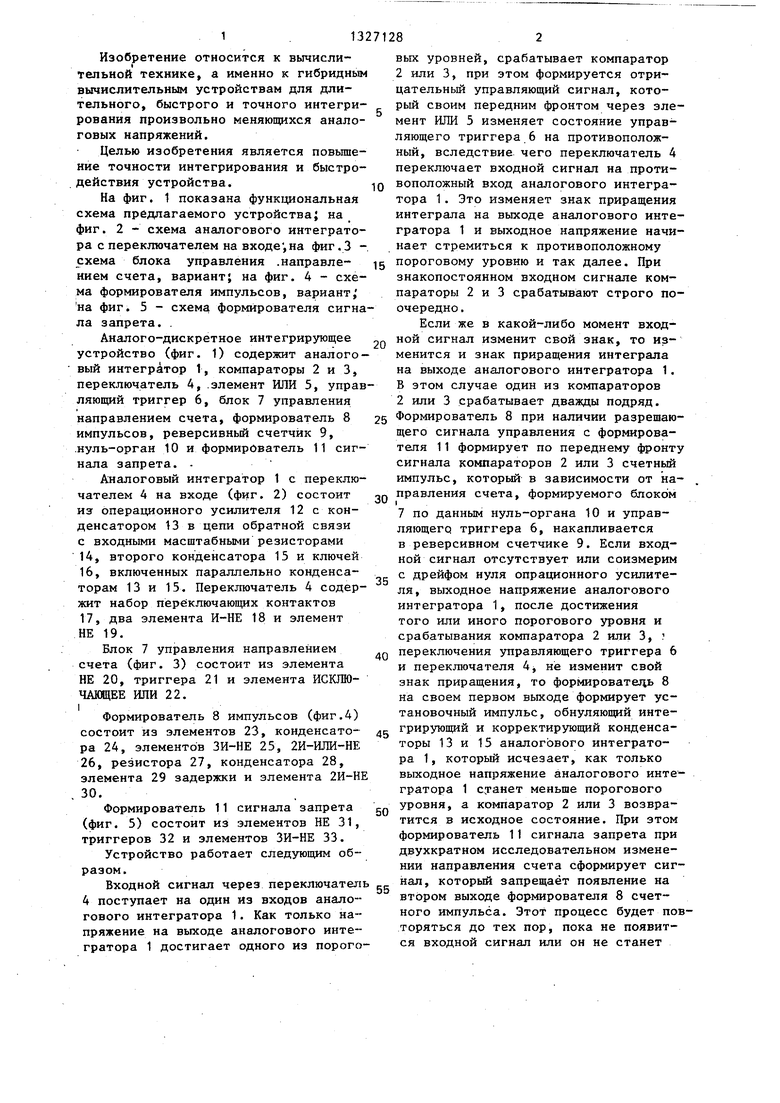

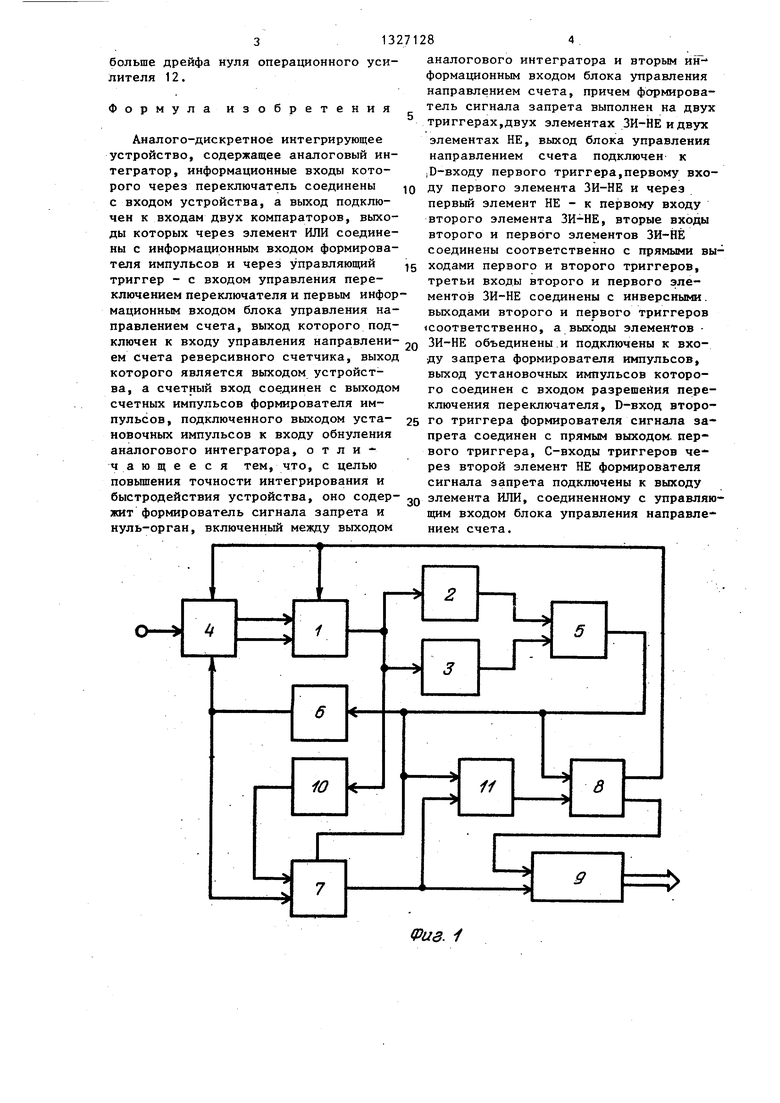

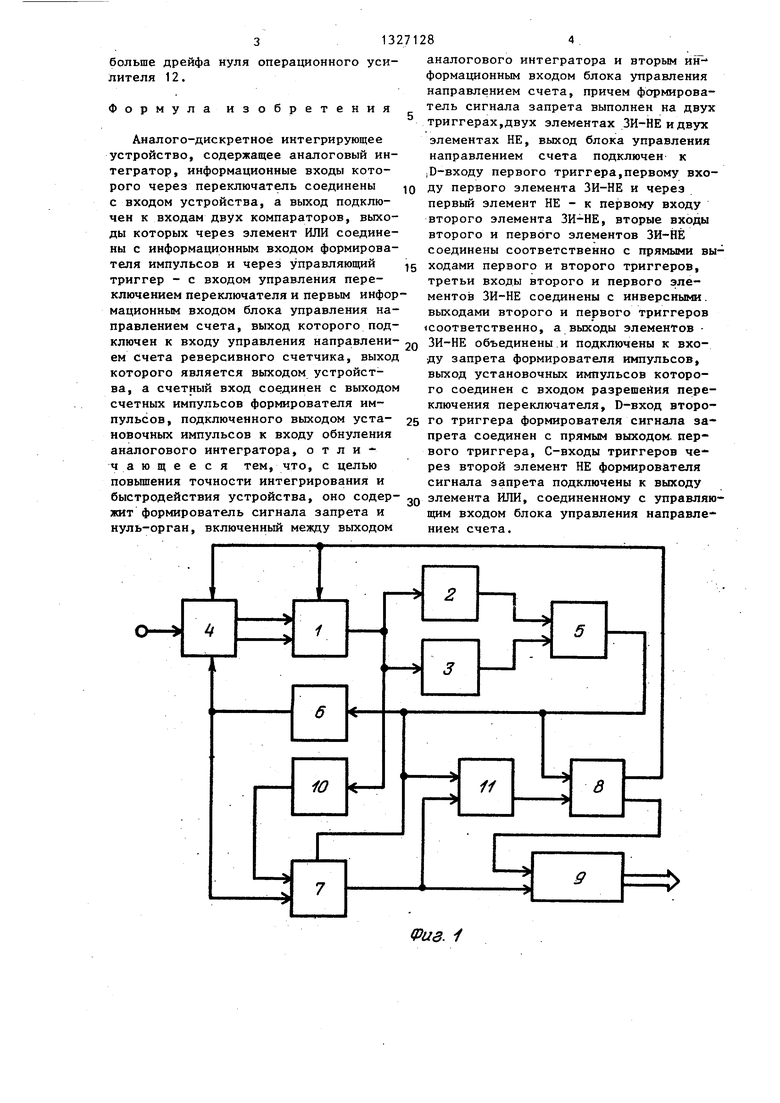

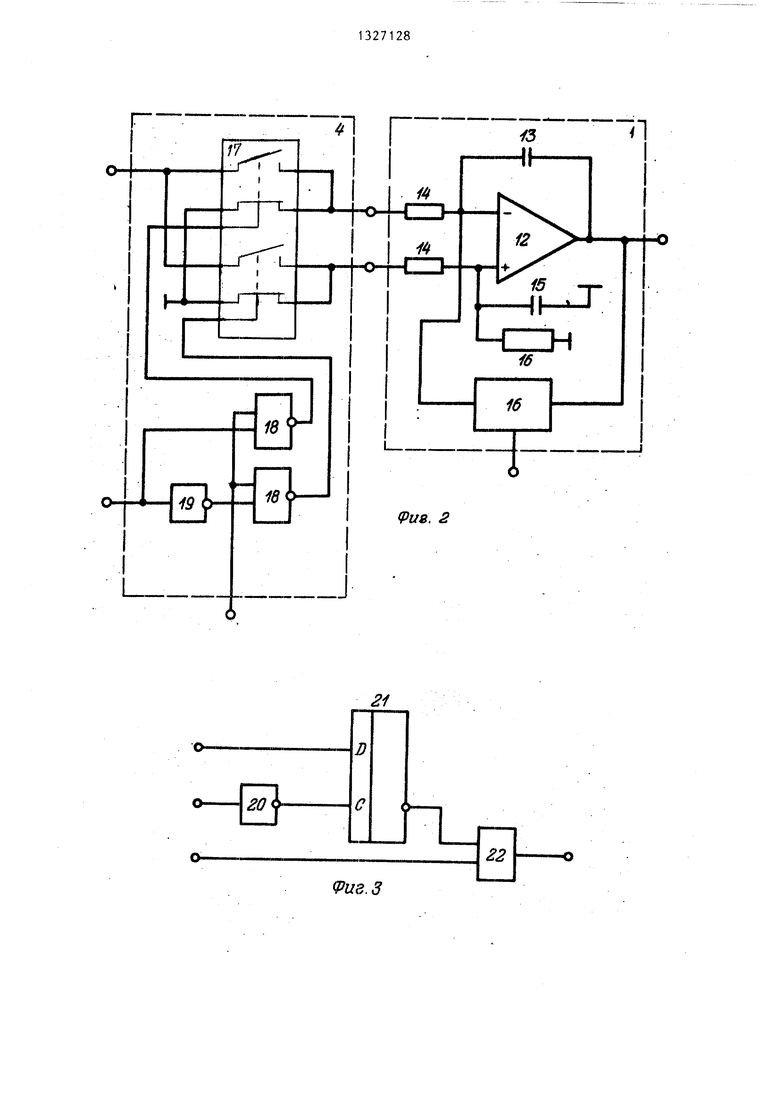

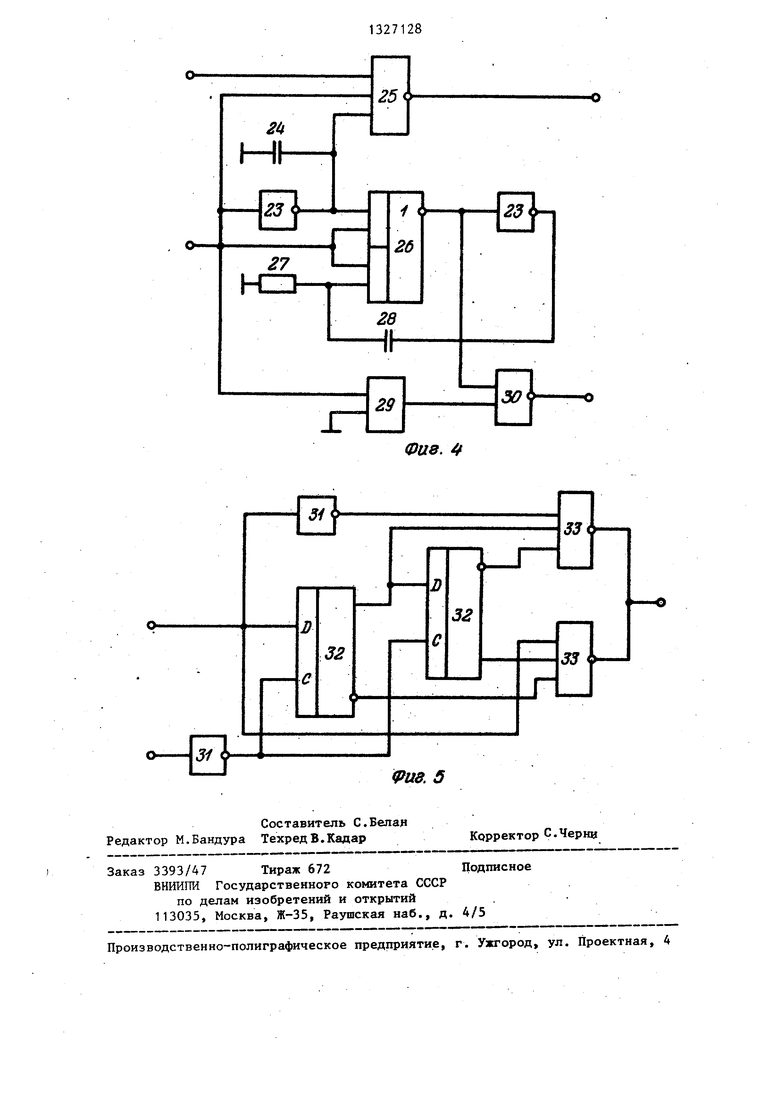

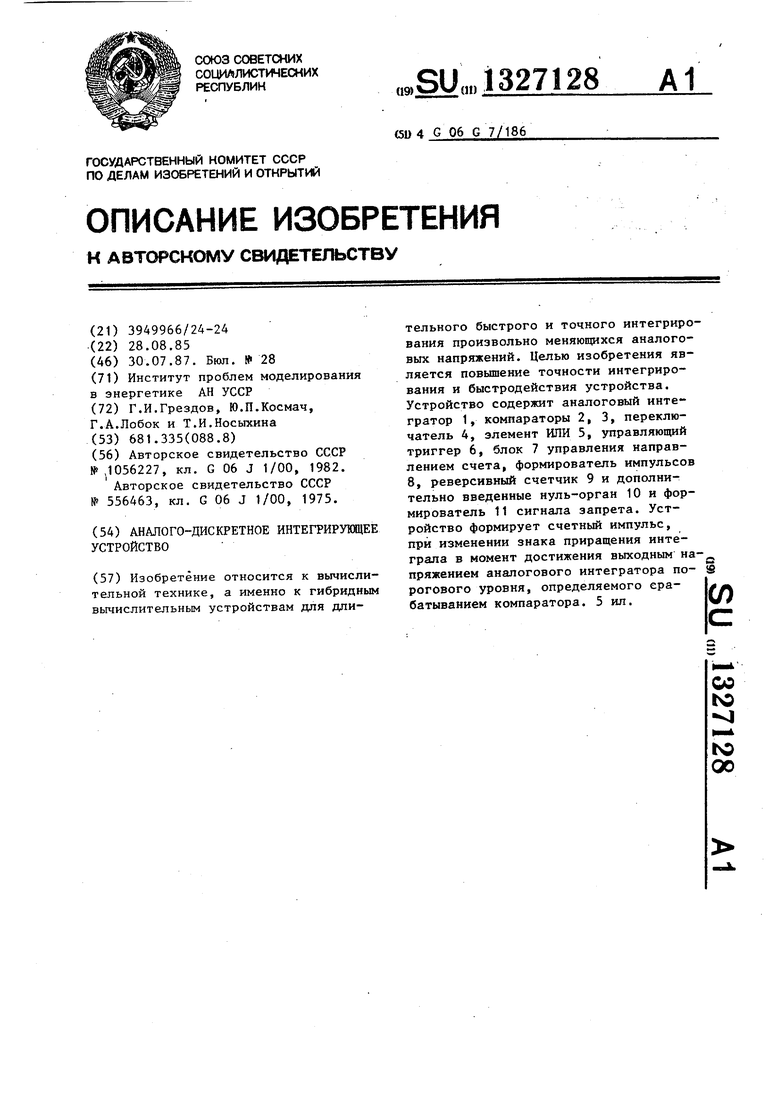

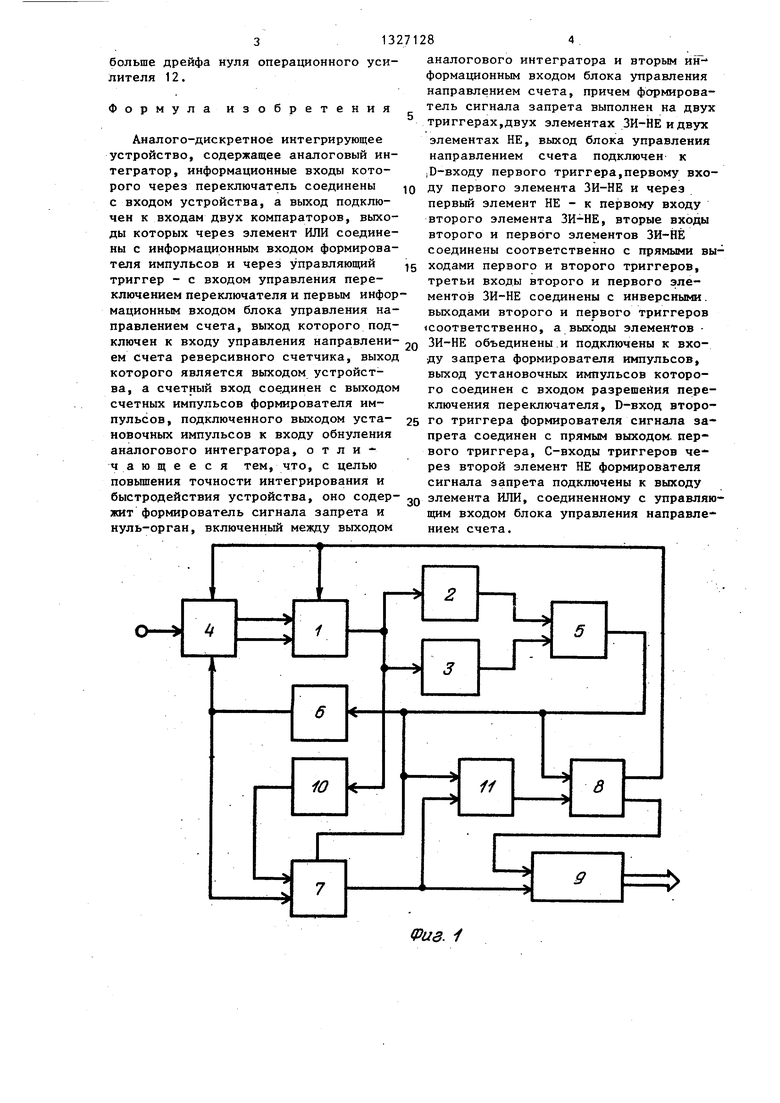

На фиг. 1 показана фунюдиональная схема предлагаемого устройства; на фиг. 2 - схема аналогового интегратора с переключателем на входе ,на фиг.З - схема блока управления .направлением счета, вариант; на фиг. 4 - схема формирователя импульсов, вариант, на фиг. 5 - схема формирователя сигнала запрета. .

Аналого-дискретное интегрирующее устройство (фиг. 1) содержит аналоговый интегратор 1, компараторы 2 и 3, переключатель 4, .элемент ИЛИ 5, управляющий триггер 6, блок 7 управления направлением счета, формирователь 8 импульсов, реверсивный счетчик 9, .нуль-орган 10 и формирователь 11 сигнала запрета. -

Аналоговый интегратор 1 с переключателем 4 на входе (фиг. 2) состоит ИЗ операционного усилителя 12 с конденсатором 13 в цепи обратной связи с входными масштабными резисторами 14, второго конденсатора 15 и ключей

16,включенных параллельно конденсаторам 13 и 15. Переключатель 4 содержит набор переключающих контактов

17,два элемента И-НЕ 18 и элемент НЕ 19.

Блок 7 управления направлением счета (фиг. 3) состоит из элемента НЕ 20, триггера 21 и элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ 22.

Формирователь 8 импульсов (фиг.4) состоит из элементов 23, конденсатора 24, элементов ЗИ-НЕ 25, 2И-ИЛИ-НЕ 26, резистора 27, конденсатора 28, элемента 29 задержки и элемента 2И-НЕ 30.

Формирователь 11 сигнала запрета (фиг. 5) состоит из элементов НЕ 31, триггеров 32 и элементов ЗИ-НЕ 33.

Устройство работает следующим образом.

7 по данным нуль-органа 10 и управляющего триггера 6, накапливается в реверсивном счетчике 9. Если входной сигнал отсутствует или соизмерим с дрейфом нуля опрационного усилителя, выходное напряжение аналогового интегратора 1, после достижения того или иного порогового уровня и срабатывания компаратора 2 или 3, переключения управляющего триггера 6 и переключателя 4, не изменит свой знак приращения, то формироватедь 8 на своем первом выходе формирует установочный импульс, обнуляющий интегрирующий и корректирующий конденсаторы 13 и 15 аналогового интегратора 1, который исчезает, как только выходное напряжение аналогового интегратора 1 станет меньше порогового уровня, а компаратор 2 или 3 возвратится в исходное состояние. При этом формирователь 11 сигнала запрета при двухкратном исследовательном изменении направления счета сформирует сиг- , который запрещает появление на

45

50

Входной сигнал через переключатель gg нал,

втором выходе формирователя 8 счетного импульса. Этот процесс будет повторяться до тех пор, пока не появится входной сигнал или он не станет

4 поступает на один из входов анало гового интегратора 1. Как только напряжение на выходе аналогового интегратора 1 достигает одного из порого0

15

„вьЕХ уровней, срабатывает компаратор 2 или 3, при этом формируется отрицательный управляющий сигнал, который своим передним фронтом через элемент ИЛИ 5 изменяет состояние управляющего триггера 6 на противоположный, вследствие чего переключатель 4 переключает входной сигнал на противоположный вход аналогового интегратора 1. Это изменяет знак приращения интеграла на выходе аналогового интегратора 1 и выходное напряжение начинает стремиться к противоположному пороговому уровню и так далее. При знакопостоянном входном сигнале компараторы 2 и 3 срабатывают строго поочередно .

Если же в какой-либо момент входной сигнал изменит свой знак, то изменится и знак приращения интеграла на выходе ангшогового интегратора 1. В этом случае один из компараторов 2 или 3 срабатывает дважды подряд. 25 Формирователь 8 при наличии разрешающего сигнала управления с формирователя 11 формирует по переднему фронту сигнала компараторов 2 или 3 счетный импульс, который в зависимости от направления счета, формируемого блоком I

7 по данным нуль-органа 10 и управляющего триггера 6, накапливается в реверсивном счетчике 9. Если входной сигнал отсутствует или соизмерим с дрейфом нуля опрационного усилителя, выходное напряжение аналогового интегратора 1, после достижения того или иного порогового уровня и срабатывания компаратора 2 или 3, переключения управляющего триггера 6 и переключателя 4, не изменит свой знак приращения, то формироватедь 8 на своем первом выходе формирует установочный импульс, обнуляющий интегрирующий и корректирующий конденсаторы 13 и 15 аналогового интегратора 1, который исчезает, как только выходное напряжение аналогового интегратора 1 станет меньше порогового уровня, а компаратор 2 или 3 возвратится в исходное состояние. При этом формирователь 11 сигнала запрета при двухкратном исследовательном изменении направления счета сформирует сиг- , который запрещает появление на

30

35

40

45

50

gg нал,

больше дрейфа нуля операционного усилителя 12.

Формула изобретения

Аналого-дискретное интегрирующее устройство, содержащее аналоговый интегратор, информационные входы которого через переключатель соединены с входом устройства, а выход подключен к входам двух компараторов, выходы которых через элемент ИЛИ соединены с информационным входом формирователя импульсов и через управляющий триггер - с входом управления переключением переключателя и первым информационным входом блока управления на15 ходами первого и второго триггеров, третьи входы второго и первого элементов ЗИ-НЕ соединены с инверсными. выходами второго и первого триггеров (Соответственно, а выходы элементов правлением счета, выход которого подключен к входу управления направлени-jg ЗИ-НЕ объединены и подключены к вхо- ем счета реверсивного счетчика, выход ду запрета формирователя импульсов,

выход установочных импульсов которого соединен с входом разрешения переключения переключателя, D-вход второ- 25 го триггера формирователя сигнала запрета соединен с прямым выходом, перкоторого является выходом устройства, а счетный вход соединен с выходом

счетных импульсов формирователя импульсов, подключенного выходом установочных импульсов к входу обнуления аналогового интегратора, отличающееся тем, что, с целью повьппения точности интегрирования и

вого триггера, С-входы триггеров через второй элемент НЕ формирователя сигнала запрета подключены к выходу

быстродействия устройства, оно содер- элемента РиШ, соединенному с управляю- жит формирователь сигнала запрета и щим входом блока управления направле- нуль-орган, включенный между выходом нием счета.

аналогового интегратора и вторым ин- формационным входом блока управления направлением счета, причем формирователь сигнала запрета выполнен на двух

триггерах,двух элементах ЗИ-НЕ и двух элементах НЕ, выход блока управления направлением счета подключен к |В-входу первого триггера,первому входу первого элемента ЗИ-НЕ и через первый элемент НЕ - к первому входу второго элемента ЗИ-НЕ, вторые входы второго и первого элементов ЗИ-НЁ соединены соответственно с прямыми выходами первого и второго триггеров, третьи входы второго и первого элементов ЗИ-НЕ соединены с инверсными. выходами второго и первого триггеров (Соответственно, а выходы элементов ЗИ-НЕ объединены и подключены к вхо- ду запрета формирователя импульсов,

вого триггера, С-входы триггеров через второй элемент НЕ формирователя сигнала запрета подключены к выходу

ие. i

Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| ЭЛЕКТРОННЫЙ ИЗМЕРИТЕЛЬ ЭЛЕКТРОЭНЕРГИИ | 1995 |

|

RU2097773C1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Интегратор | 1978 |

|

SU748438A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1418768A1 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Электромагнитный расходомер | 1987 |

|

SU1578481A1 |

| Система управления мощностью турбины | 1984 |

|

SU1227823A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU849236A1 |

Изобретение относится к вычислительной технике, а именно к гибридным вычислительным устройствам для длительного быстрого и точного интегрирования произвольно меняющихся аналоговых напряжений. Целью изобретения является повышение точности интегрирования и быстродействия устройства. Устройство содержит аналоговый интегратор 1, компараторы 2, 3, переключатель 4, элемент ИЛИ 5, управляющий триггер 6, блок 7 управления направлением счета, формирователь импульсов 8, реверсивный счетчик 9 и дополнительно введенные нуль-орган 10 и формирователь 11 сигнала запрета. Устройство формирует счетный импульс, при изменении знака приращения интеграла в момент достижения выходным на- пряжением аналогового интегратора по- рогового уровня, определяемого срабатыванием компаратора. 5 ил. (Л СА9 to Ю 00

Ри.. 3

5

32

Составитель С.Белан Редактор М. Бандур а Техред В. Кадар

Заказ 3393/47 Тираж 672Подписное

ВИИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фив.

33

33

U8. 5

Корректор С,Черни

| Аналого-цифровой интегратор | 1982 |

|

SU1056227A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1985-08-28—Подача