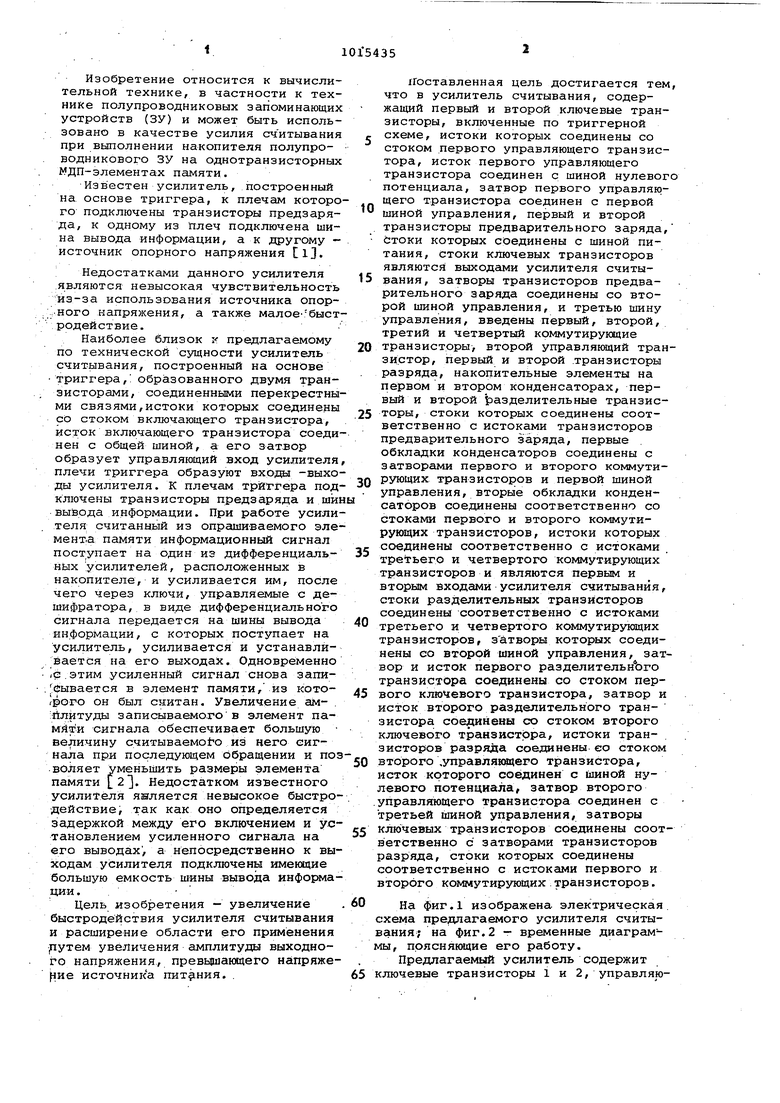

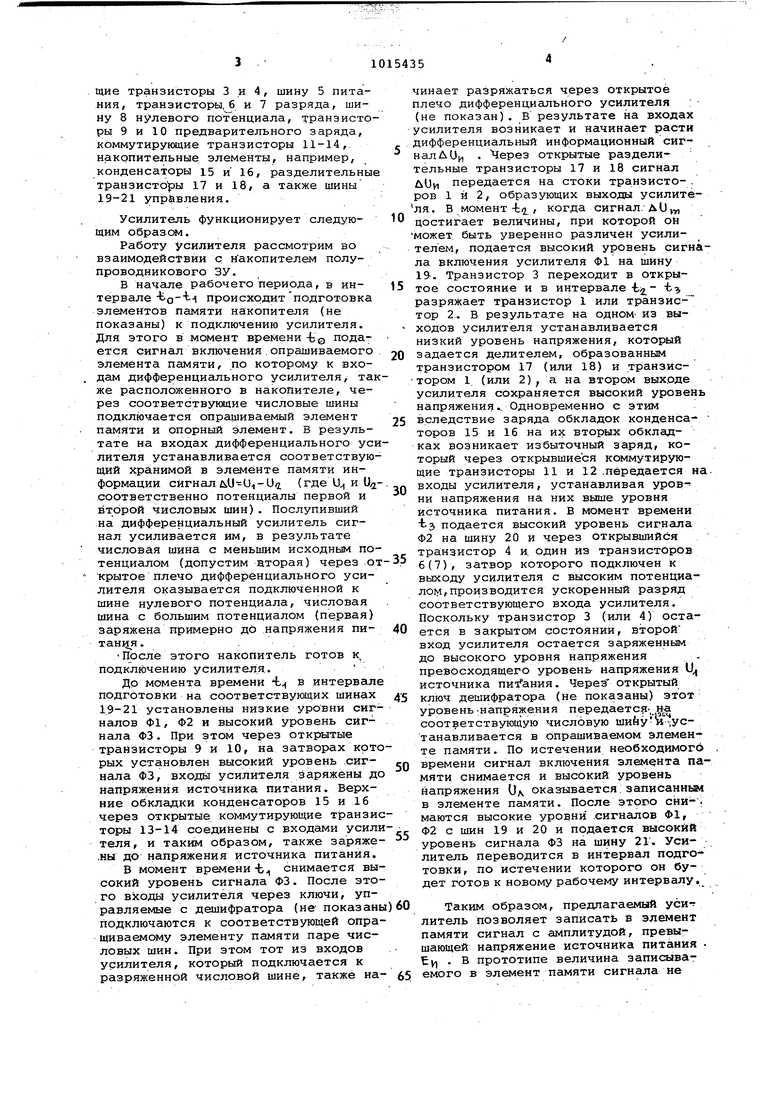

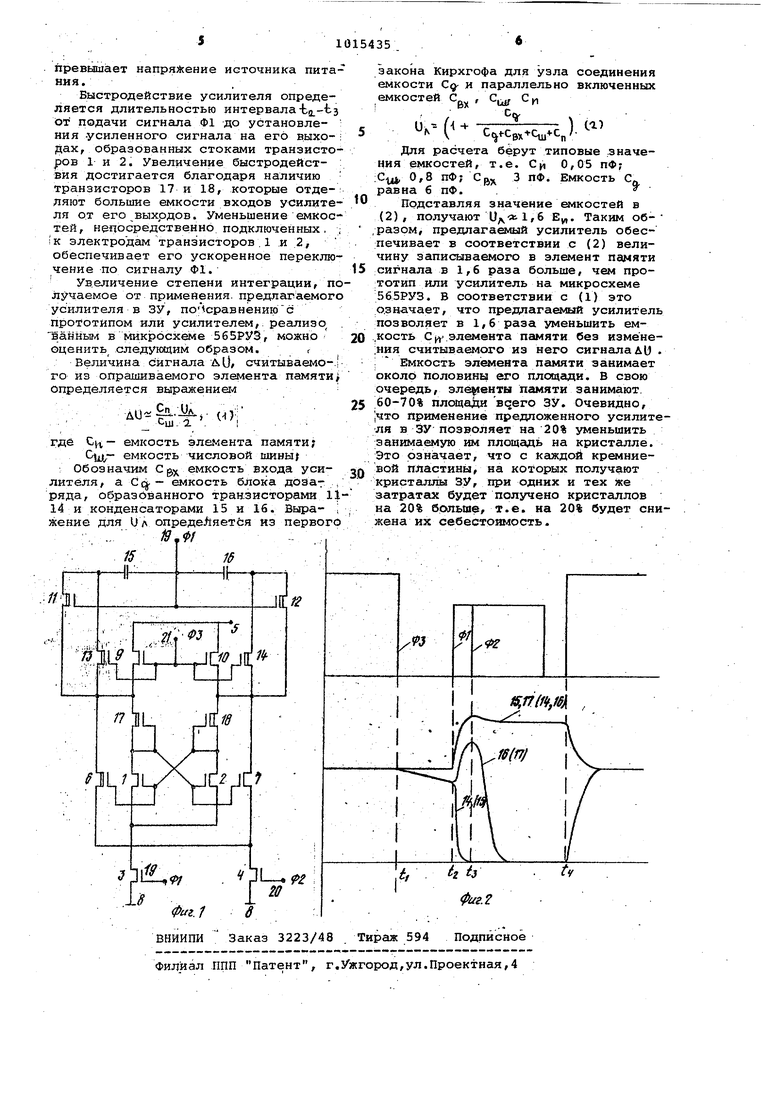

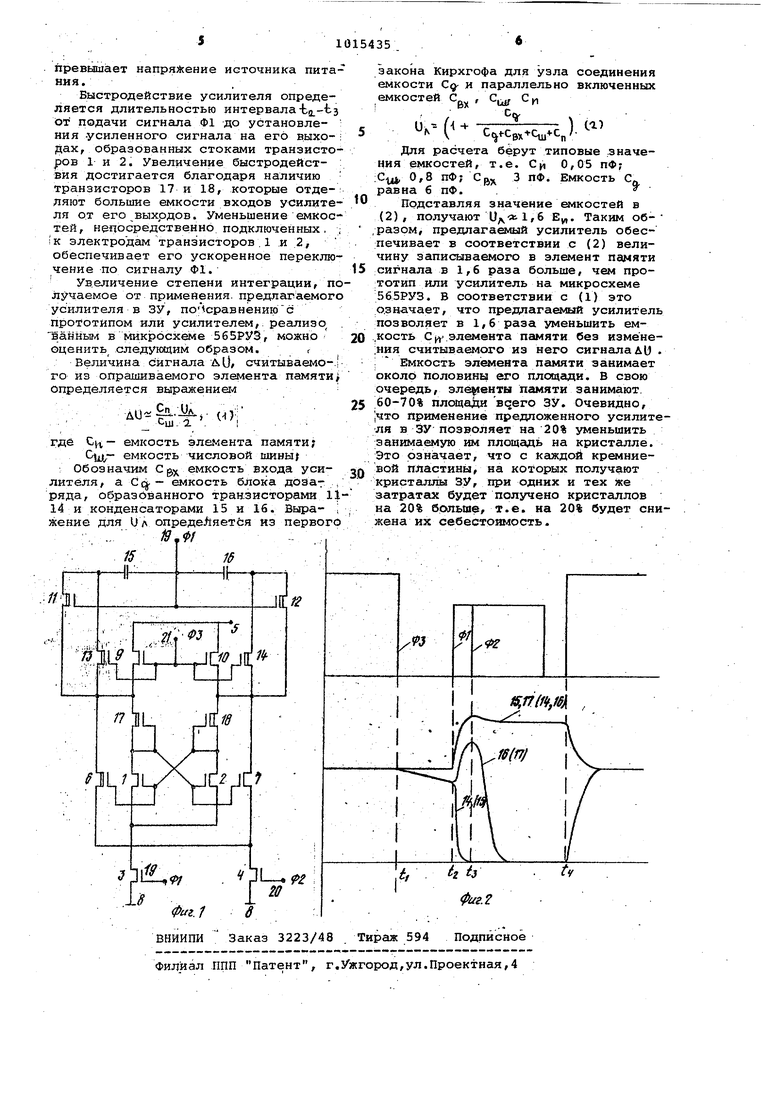

Изобретение относится к вычислительной технике, в частности к технике полупроводниковых запоминающих устройств (ЗУ) и может быть использовано в качестве усилия считывания при выполнении накопителя полупроводникового ЗУ на однотранзисторных МДП-элементах памяти. Известен усилитель, построенный на основе триггера, к плечам которо го подключены транзисторы предзаряда, к одному из Плеч подключена шина вывода информации, а к другому - источник опорного напряжения tlj. Недостатками данного усилителя являются невысокая чувствительность из-за использования источника опор,-ного напряжения, а также малое-быст родействие.Наиболее близок у предлагаемому по технической сущности усилитель считывания, построенный на основе триггера, образованного двумя транзисторами, соединенными перекрестны ми связями,истоки которых соединены со стоком включающего транзистора, исток включающего транзистора соеди нен с общей шиной, а его затвор образует управляющий вход усилителя плечи триггера образуют входы -выхо ды усилителя. К плечам триггера под ключены транзисторы предзаряда и ши вывода информации. При работе усили теля считанный из опрашиваемого эле мента памяти информационный сигнал поступает на один из дифференциальных усилителей, расположенных в накопителе, и усиливается им, после чего через ключи, управляемые с дешифратора, в виде дифференциального сигнала передается на шины вывода информации, с которых поступает на усилитель, усиливается и устанавливается на его выходах. Одновременно 1с.этим усиленный сигнал снова запи.еывается в элемент памяти, из кото) он был снитан. Увеличение ам- . ;йлитуды записываемогов элемент памяти сигнала обеспечивает большую величину считываемо1о из него сигНала при последующем Обращении и поэ воляет уменьшить размеры элемента памяти . Недостатком известного усилителя является невысокое быстродействие, так как оно определяется задержкой между его включением и установлением усиленного сигнала на его выводах , а непосредственно к выходам усилителя подключены имекадие большую емкость шины вывода информации. , . Цель изобретения - увеличение быстродействия усилителя считывания и расширение области его применения рутем увеличения амплитуды выходного напряжения, превышающего напряже 1ие источника питания. . яоставленная цель достигается тем, что в усилитель считывания, содержащий первый и второй ключевые транзисторы, включенные по триггерной схеме, истоки которых соединены со стоком первого управляющего транзистора, исток первого управляющего транзистора соединен с шиной нулевого потенциала, затвор первого управляющего транзистора соединен с первой шиной управления, первый и второй транзисторы предварительного заряда, йтоки которых соединены с шиной питания, стоки ключевых транзисторов являются выходами усилителя считывания, затворы транзисторов предварительного заряда соединены со второй шиной управления, и третью шину управления, введены первый, второй, третий и четвертьй коммутирующие транзисторы, второй управляющий транзистор, первый и второй .транзисторы разряда, накопительные элементы на первом и втором конденсаторах, первый и второй разделительные транзисторы, стоки которых соединены соответственно с истоками транзисторов предварительного заряда, первые обкладки конденсаторов соединены с затворами первого и второго коммутирующих транзисторов и первой шиной управления, вторые обкладки конденсаторов соединены соответственно со стоками первого и второго коммутирующих транзисторов, истоки которых соединены соответственно с истоками третьего и четвертого коммутирующих транзисторов и являются первым и вторым входами усилителя считывания, стоки разделительных транзисторов соединены соответственно с истоками третьего и четвертого коммутирующих транзисторов, затворы которых соединены со второй шиной управления, затвор и исток первого разделительнЪго транзистора соединены со стоком первого ключевого транзистора, затвор и исток второго разделительного транзистора, соединены со стоком второго ключевого транзистора, истоки транзисторов разряда соединены ео стоком второго ,управляющего транзистора, исток которого соединен с шиной нулевого потенциала, затвор второго управляющего транзистора соединен с третьей шиной управления, затворы ключевых транзисторов соединены соответственно с затворами транзисторов разряда, стоки которых соединены соответственно с истоками первого и второго коммутирующих .транзисторов. На фиг.1 изображена электрическая, схема предлагаемого усилителя считывания; на фиг.2 - временные диагргдаы, поясняющие его работу. Предлагаемый усилитель содержит лючевые транзисторы 1 и 2, управляющие транзисторы 3 и 4, шину 5 питания, транзисторы, 6 и 7 разряда, шину 8 нулевого потенциала, транзисторы 9 и 10 предварительного заряда, коммутирующие транзисторы И-14, накопительные элементы, например, конденсаторы 15 и 16, разделительные транзисторы 17 и 18, а также шины 19-21 управления. Усилитель функционирует следующим образс 4. Работу усилителя рассмотрим во взаимодействии с накопителем полупроводникового ЗУ. В начсше рабочего периода, в интервале -to-t происходитподготовка элементов памяти накопителя (не показаны) к подключению усилителя. Для этого в момент времени-Ь0 подается сигнал включения.опрашиваемого элемента памяти, по которому к входам дифференциального усилителя, так же расположенного в накопителе, через соответствуквдие числовые шины подключается опрашиваемый элемент памяти и опорный элемент. В результате на входах дифференциального уси лителя устанавливается соответствующий хранимой в элементе памяти информации сигнал . (где и и 0 соответственно потенциалы первой и второй числовых шин). Послупивший на дифференциальный усилитель сигнал усиливается им, в результате числовая шина с меньшим исходным потенциалом (допустим вторая) через от крытое плечо дифференциального усилителя оказывается подключенной к шине нулевого потенциала, числовая шина с большим потенциалом (первая) заряжена примерно до напряжения питания.. . После этого накопитель готов к, подключению усилителя. До момента времени Ч в интервал подготовки на соответствующих шинах 1.9-21 установлены низкие уровни сиг налов Ф1, Ф2 и высокий уровень сигнала ФЗ. При этом через открытые транзисторы 9 и 10, на затворах кото рых установлен высокий уровень .сигнала ФЗ, входы усилителя заряжены д напряжения источника питания. Верхние обкладки конденсаторов 15 и 16 через открытые коммутирующие транзи торы 13-14 соединены с входами усил теля, и таким образом, также заряже .ны до напряжения источника питания. В момент времени-fc снимается вы сокий уровень сигнала ФЗ. После это го входы усилителя через ключи, управляемые с дешифратора (не показан подключаются к соответствующей опра шиваемому элементу памяти паре числовых шин. При этом тот из входов усилителя, который подключается к разряженной числовой шине, также на чинает разряжаться через открытое плечо дифференциального усилителя : (не показан). В результате на входах усилителя возникает и начинает расти дифференциальный информационный сигнал А (J, . Через открытые разделительные транзисторы 17 и 18 сигнал i(jy, передается на стоки транзисто-. ров 1 и 2, образующих выходы усилителя. В момент-fc. / когда сигнал. АUv, достигает величины, при которой он может быть уверенно различен усилителем, подается высокий уровень сигнала включения усилителя Ф1 на шину 19. Транзистор 3 переходит в открытое состояние и в интервале разряжает транзистор 1 или транзис- тор 2. в результа.те на одном- из выходов усилителя устанавливается низкий уровень напряжения, который задается делителем, образованным транзистором 17 (или 18) и транзистором 1 (или 2) , а на втором вых.оде усилителя сохраняется высокий уровень напряжения.. Одновременно с этим вследствие заряда обкладок конденса- торов 15 и 16 на их вторых обкладках возникает избыточный заряд, который через открывшиеся коммутирующие транзисторы 11 и 12 .передается на. входы усилителя, устанавливая уровни напряжения на них выше уровня источника питания. В момент времени bj, подается высокий уровень сигнала Ф2 на шину 20 и через открывшийся транзистор 4 и. один из транзисторов 6(7), затвор которого подключен к выходу усилителя с высоким потенциалом, производится ускоренный разряд соответствующего входа усилителя. Поскольку транзистор 3 (или 4) остается в закрытом состоянии, второй вход усилителя остается заряженным до высокого уровня напряжения . превосходящего уровень- напряжения Ц источника . Через открытый ключ дешифратора (не показаны;) этот уровень :напряжения передается-на соответствующую числовую шийуи устанавлнвается в опрашиваемом элементе памяти. По истечении необходимого времени сигнал включения элемента памяти снимается и высокий уровень напряжения 0 оказывается.записанным в элементе памяти. После этого сни-. маются высокие уровни .сигналов Ф1, Ф2 с шин 19 и 20 и подается высокий уровень сигнала ФЗ на шину 2Г, Усилитель переводится в интервал подготовки, по истечении которого он будет готов к новому рабочему интервалу. Таким образом, предлагаемый уси-г литель позволяет записать в элемент памяти сигнал с амплитудой, превышающей напряжение источника питания . tv/l . В прототипе величина записываемого в элемент памяти сигнала не

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

| Адресный формирователь | 1979 |

|

SU955192A1 |

| Усилитель считывания | 1978 |

|

SU769617A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Устройство для записи информации в блоки памяти с произвольной выборкой | 1984 |

|

SU1156136A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содер жащий первый и второй ключевые транзисторы, включенные по триггерной схеме, ИСТО5КИ которых соединены со стоком первого управляющего транзистора, .исток первого управляющего транзистора соединен с шиной нулевог потенциала, затвор первого управляющего транзистора соединен с первой шиной управления, первый и второй ;транзисторы предварительного заряда стоки которых соединены-с шиной пита ния , стоки ключевьлх транзисторо являются выходами усилителя считывания, затворы транзисторов предварит тельного заряда соединены со второй иданой управления, и третью шину управления, о т л и ч а ю щи и с я тем, что, с целью повьоаения быстродействия и расширения области qro применения путем увеличения выходного нгшряжения, превышаемого напряж ние источника питанияj в него введены первый, второй, третий и четвертый коммутирующие траиэйстоЕИ, второй управляющий транзистор, первый и транзисторы разряда, накрпн тельные элементы на первом и втором конденсаторах, первый и второй разделительные транзистс а стоки которых соединены соответственно с истоками транзисторов предварительного заряда, первые обкладки койдексаторов соединены с затворами первого и второго коммутирующих транзисторов и первой шиной управления, вторые обкладки конденсаторов соединены соответственно со стоками первого и второго коммутирукюих транзисторов, истоки которых соединены соответственно с истоками третьего и четвертого коммутирующих транзисторов и являются nepBbiM и вторш, усилителя счиилаания CTOICH разделительных транзисторов соединены COOT-I ветственно с истоками третьего и четвертого коммутирующих транзисто ров затворы кото1зых соединены со второй шиной управления, затвор и исток первого разделителзьного транзистора соединены со стоком nepBojro ключевого транзистора, .затвор и исток второго разделительного транзистора соединены со стоком второго ключевого транзистора, истоки транзисторов разряда соединены со стоком второго управля- ющего транзистора, исток соединен с шиной нулевого потейциаЛа, затвор второго улравляквдегв транёистора соединен с третьей шиной управления, затворы .ключевых транзисторов соединены соответственно с затво рами транзисторов разряда. Стоки. которых соединены соответственно с истоками первого и второго коммутирующих транзисторов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4003035, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| . | |||

Авторы

Даты

1983-04-30—Публикация

1981-12-23—Подача