(54) РЕГИСТР СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр сдвига | 1982 |

|

SU1111207A1 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Адаптивный классификатор | 1984 |

|

SU1220004A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| УСТРОЙСТВО ВЫБОРА ОПТИМАЛЬНОГО МАРШРУТА МАНЕВРА | 1992 |

|

RU2045773C1 |

| Автоматизированный класс для контроля знаний обучаемых | 1984 |

|

SU1196938A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство трансляции | 1986 |

|

SU1390629A1 |

| Устройство для обмена информацией | 1986 |

|

SU1424001A1 |

I

Изобретение относится к автоматике н может быть использовано при построении автоматических устройств различного назначения, в частносуги систем управления процессом сортировки штучньгх грузов, например лесоматериалов в лесной промышленности.

Известен регистр сдвига, состоящий из нескольких одинаковых ячеек бесконтактных элементов памяти, поразрядно соединенных между собой через сдвигающие элементы типа Запрет 1 .

Наиболее близким к предлагаемому по технической сущности является регист сдвига, содержащий ячейки элементе памяти с раздельными входами зааиси и их сгирания, между которыми поразрядно подключены сдвигающие элементы Запрет с раздельными вводами возбуждения и объединенным входом запрета. Выходы элементов памяти данной ячейки поразрядно соединены со входами возбуждения сдвигающих элементов Запрет последующей ячейки, а через диоды обьединены между собой. Выходы сдвигающие элементов Загфет данной ячейки поразрядно соединены со входами записи элементов памяти данной ячейки и со входйми стирания элементов памяти предыдущей ячейки. Питается регистр от соотвегствующих источников напряжения 12.

Недостатком известных регистров является низкая надежность сдвига кодов.

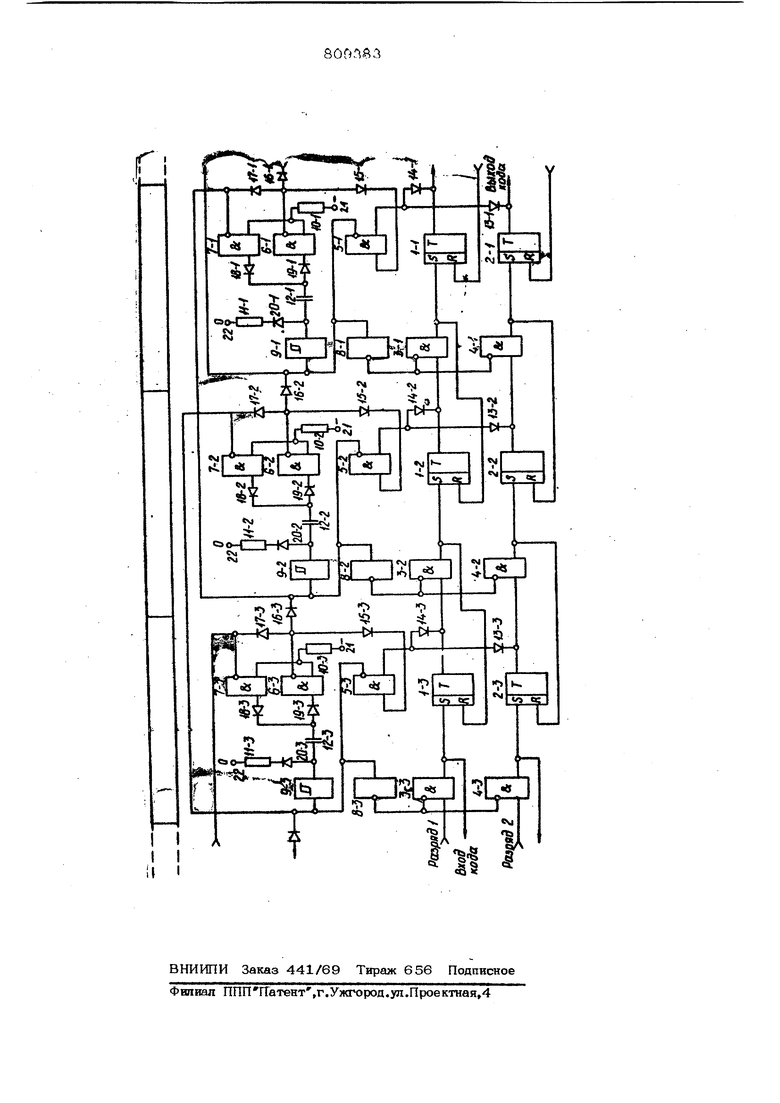

0 Объясняется это тем, что в результате диодного объединения выходов элементов памяти и общего входа запрета сдвигаю-. щих элементов Запрет элемент памятв, возбудивщийся при сдвиге первым, закры5вает путь для прохождения отставщих единиц кода. Поэтому часть единиц данKOFO кода оказьюается на предназначавшемся ей месте, а другая, отставшая, часть единшх данного кода, оказывается не в той ячейке. Код как бы разбивается на два кода, каждый из которых искажен в сравнении с введенным в регистр кодом. К тому же два кода занимают две 36 ячейки вместо одной, в результате чего работа регистра нарушается. Цепь изобретения - повышение надежности регистров сдвига. Поставленная цель достигаемся тем, что в регистр сдвига, содержащий в каждом разряде иоследовательно соединенные первый элемент памяти и первый элемент Запрет и втезрой элемент Запрет и второй элемент памяти, причем выходы элементов памяти каждого разряда соединены соответственно с одним из входов элементов Запрет последующего разряда, выходы элементов Запрет каждого разряда подключены соответственно к другим входам элементов памяти последу ющего разряда, выход первого элемента памяти каждого .разряда соединен через последовательно включенные первый и второй нелинейные элементы, например диоды, с выходом второго элемента памя ти каждого разряда, и шины питания, в каждый его разряд введены третий, четвертый и пятый элементы Запрет, поро говый элемент, третий, четвертый пятыйгшесгай,седьмой и восьмой нелинейные элементы, например дноды, два пассивных элемента, например резисторы, накопительный элемент, например конден сатор, и инвертор, выход KOTqioro соеди нен с другими входами первого и второго элементов Запрет данного разряда, вход инвертора соединен с одним из входов третьего элемента Запрет входом порогового элемента данного разряда, катодом четвертого диода предыдущего разряда и одним из входов четвертого элемента Запрет последующего разряда, другой вход третьего элемента Запрет подключен к анодам первого и вто рого диодов данного разряда, выход третьего элемента Запрет данного разряда соединен через последовательно включенные третий и четверть(й диоды со входом порогового элемента, один из вхо дов пятого элемента Запрет данного соединен с анодами гретьего и четвертого диодов и через пятый диод с одним из входов четвертого элемента Запрет данного разряда и со входом порогового элемента предыдущего разряда, другие входы чегверуого и пятого элементов Запрет каждого разряда сое динены через первый резистор с первой шинсЛ питания, выходы четвертого и пятого элеменгов Запрет каждого разряда через шестой и седьмой противополож но вк/ооченные диоды соединены с одной из обкладок конденсатора. Другая обклад 3 а которого соединена с выходом пороового элемента и через последовательо вклкэченные восьмой диод и второй езистс со .второй шиной питания, На чертеже представлена электричесая схема предлагаемого регистра сдвига {только три разряда). Регистр сдвига содержит первые элементы 1.1-1.3, втфые элементы памяти 2.1-2.3, первые элементы Запрет 3.13.3, вторые элементы Запрет 4.1-4.3, третьи элементы Запрет 5.1-5.3, четвертые элементы Запрет 6.1-6.3, пятые элементы Запрет 7.1-7.3, инверторы 8.1-8.3, пороговые элементы 9.19.3, первые пассивные элементы, например резисторы 1.0.1-10.3, вторые пассивные элементы, например резисторы 11,1-11.3, накопительные элементы, например конденсаторы 12.1-12.3, нелинейные элементы, например первые диоды 13,1-13.3, вторые диоды 14.1-14.3, третьи диоды 15.1-15.3, четвертые дноДЬ1 16.1-16.3, пятые диоды 17.1-17.3, шестые диоды 18.1-18.3, седьмые диоды 19,1-19,3, восьмые диоды 20.120,3, шины питания 21 и 22. Пороговый элемент превращает конденсаторный импульс непрямоугольной формы. создаюший благодаря такой форме возможность для неодновременного открытия элементов Запрет (одна из причин неправильного сдвига) в импульс прямоугольной формы, благодаря чему неодновременность открытия исключается. Инвертор . преобразует указанный импульс ненулевой амплитуды в импульс той же длительности, но с нулевой амплитудой, как раз к нужна для открытия элемента Запрет. Регистр сдвига работаев, следующим образом, В исходном состоянии регистра конденсатс эы 12,1-12.3 заряжены, на выходе инверторов 8.1-8.3 присутствуют сигналы, элементы Запрет 3.1-3.3 и 4.1-4.3 закрыты и в разрядах отсутствует информация. В начале поступления первого кода на входных шинах появляется комбинация статичных сигналов , а на входах элемвнгоБ 6,3 и 7.3 - один импульсный сигнал, вырабатываемый в четвертом разряде (не показан). Благодаря импульсному сигналу, через низкоомный резистор 11.3 и элемент 7.3 конденсатор 12.3 быстро разряжается, В момент исчезновения импульсного сигнала от заряд-. ного гока конденсатора 12.3 появляется такой же импульсный сигнал на выходе элемента 9,3, в результате чего напряжение на выходе инвертора 8,3 пропадает и единицы кода с входных шин проходят на элементы памяти 1.3 и 2,3. Вы ходкой импульсный сигнал элемента 9.3 поступает также на входы элементов 6,2 и 7,2, вследствие чего разряжается конденсатор 12.2. После чего исчезнсже ния такой же сигнал формирует элемент 9,2, под действием которого код с элементов памяти 1,3 и 2.3 поступает на элементы памяти 1.2 ji 2.2, и одновременно разряжается конденсатор 12.1. После завершения импульсов инвертера 9,2 такой же имлульс генерирует инвертор 9,1 и код с элементов памяти 1.2 и 2.2 сдвигается на элементы памяти 1,1 и 2.1, таким образом первый код поступает в первый разряд. Аналогично второйкод поступает во второй, а третий - в третий разряд, причём конденсаторы 12.1-12.3 оказьшаются разряженными. После изъятия первого кода потребите лем (роль потребителя кодов в принципе может играть нулевой разряд того же построения, что и остальные, но дополненный соответствующим набором дешифраторов) исчезает сигнал на объединенном выходе элементов памяти 1,1 и 2,1 запрет с элемента. 6,1 снимается, в результате чего элемент 9.1 формирует новый импульс и второй код сдвигается с элементов памяти 1,2 и 2,2 на элемен ты памяти 1.1 и 2.1, становясь теперь уже первым, то есть готовым к изъятию потребителем. После завершения этого импульса очередной импуЛьс выдает элемент 9,2 и третий код сдвигается с элементов памяти 1.3 и 2.3 на элементы 1,2 и 2,2, становясь теперь уже вторым, В зависимости от порядка поступления и изъятия кодов возможны самые разнообразные варианты заполнения регистра «одами, однако в любом случае взаимодействие элементов регистра в принципе остается тем, что указано выше. Временные параметры элементов, составляющих регистр, мотут меняться в связи с различиями технологии изготов- ления элементов, их монтажа, температур ными изменениями, с явлением засыпания полупроводниковых элементов и т.д. Все эти отклонения могут быть учтены путем увеличения емкости конденсаторов. Тогда правильность сдвига кодов не может быть нарушена в течение всего времени эксплуатации регистра. Предлагаемый регистр сдввга позволяет повысить надежность сдвига кодов при естественных колебаниях временных параметров элементов, составляющих регистр. Формул, а изобретенвя Регистр сдвига, содержащий в каждом разряде последовательно соединенные оер- вый элемент Запрет н первый элемент памятя и втсфой элемент Запрет и второй элемент памяти, причем выходы элементов памяти: каждого разряда соединены соответственно с одним из входсю элементов Запрет последующего разряда, выходы элементов Запрет каждого разряда подключены соответственно к другим входам элементов памяти последующего разряда, выход первого элемента памяти каждого разряда соединен через последовательно включенные первый и второй нелинейные элементы, наприм дводы, с выходом второго элемента памяти каждого разряда, и шины питания, отличающийся тем, что, с целью повышения надежности регистра сдвига, в каждый его разряд введены третий, чет- чертый и пятый элементы Затфет пороговый элемент, третий, четвертый, пятый, шестой, седьмой и восьмой непинейHbie элементы, например диоды, два иассивных элемента, иаприм резистс ы, накопительный элемент, например конденсатор, и инвертор, выход которого соединен с другими входами первого и второго элементов Запрет данного разряда, вход инвертора соединен с одним из входов третьего элемента Запрет входом порсяовото элемента данного разряда, катодом четвертого диода предыдущего разряда и ОД1ИМ из входов четвертого элемента Запрет последующего разряда, другой вход третьего элемента Запрет подключен к анодам первого и второго диодов данного разряда, выход третьего элемента Запрет данного разряда -соединен через последовательно вклооченвые третий и четвертый диоды со входом йорогового элемента, один из входов пятого элемента Запрет данного разряда соединен с анодами третьего и четвертого диодов и через пятый диод с одним из входов четвертого элемента Запрет данного разряда и со входом порогового элемента предыдущего разр.яда другве 78 входы четвертого и пятого элементов Запрет каждого разряда соединены через первый рез кстор с первой шиной питанвя, выходы четвертого и пятого элементов Запрет каждого taзpядa через шестой и седьмой противоположно включенные диодь соединены с одной из обкладок конденсатора, другая обкладка ко торого соединена с выходом порогового элемента и через последсвательно включенные восьмой диод и второй резкстор со второй шиной питания. Источники информации, принятые во внимание при экспертизе 1,Вильке i. А., Автоматизация производственных прочессов лесопромышленных предприятий. М., Лесная промышленность, 1972, с. 248, рис. 119. 2.Штольцер Н. Г, Автоматизация управления сортировками штучных тел. .М., Лесная 1фомышленность-, 1972, с. 41, рис. 13 (прототип).

Авторы

Даты

1981-02-28—Публикация

1978-06-08—Подача