(54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель отношения временных интервалов | 1990 |

|

SU1723562A1 |

| Устройство для измерения низких частот | 1981 |

|

SU966618A1 |

| Цифровой измеритель отношения временных интервалов | 1986 |

|

SU1322223A1 |

| Делитель частоты с дробным коэффициентом деления | 1978 |

|

SU750744A1 |

| Цифровой измеритель отношения временных интервалов | 1981 |

|

SU983644A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Цифровой управляемый генератор | 1987 |

|

SU1415448A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| Цифровой управляемый генератор | 1986 |

|

SU1378022A1 |

| Устройство для измерения скорости вращения асинхронного электродвигателя | 1976 |

|

SU648909A1 |

1

Изобретение относится к импульсной технике и может использоваться в дискретно корректируемых автоматических системах регулирования скорости шагового двигателя.

По основному авт.св. 520713 известен управляемый делитель частоты, . соде ржащийс блок записи кода, на вход которого подается сигнал ввода коэффициента деления, а выход соединен с разрядными входами счетчика импульсов, элемент ИЛИ, блок разре а кя деления, на вход которого подается сигнал разрешения и два элемента И-НЕ, первый вход первого из которых соединен с первым выходом блока разрешения деления, второй - с 1 еммой источника входного сигнеш а выход - со счетным входом счетчика импульсов, разрядные выходеа которого подключены ко входам второго элемента И-НЕ, выход которого соединен с первым входом элемента ИЛИ второй вход которого подключен ко . второму выходу блока разрешения деления, а выход - к входу блока за. писи. кода L11.

Недостатком данного устройства является то, что его функциональные возможности ограничены лишь делением на заранее введенный коэффициент деления. Однако в ряде случаев для повышения точности регулирования, возникает необходимость автоматической коррекции частоты на выходе управляемого делителя частоты в соответствии с показаниями датчика обратной связи. При этом возникает задача вычисления скорректированного

0 значения коэффициента деления.

Цель изобретения - расширение функциональных возможностей.

Указанная цель достигается тем, что в управляемый делитель частоты,

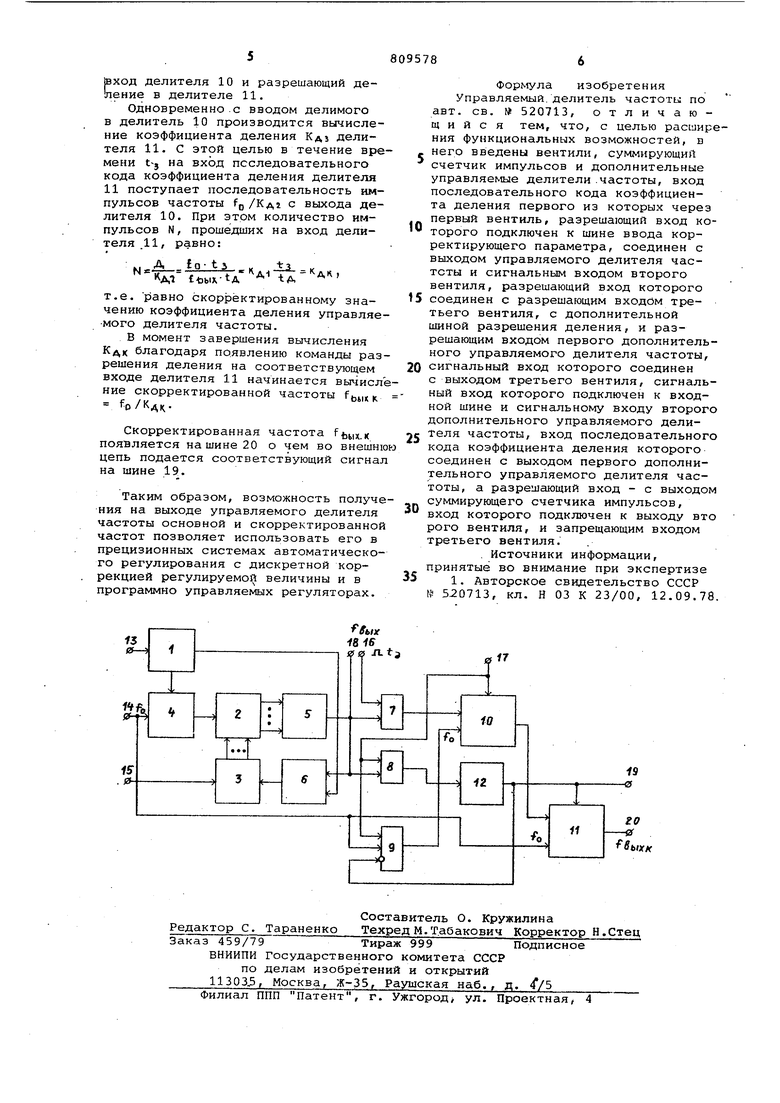

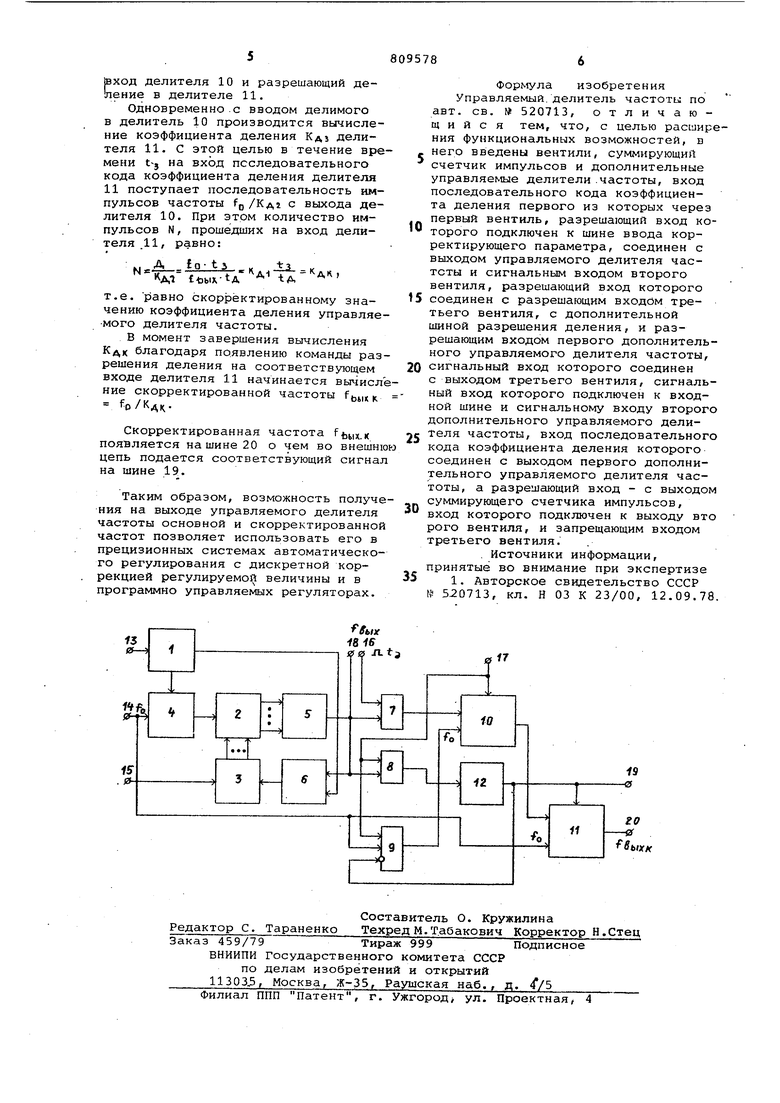

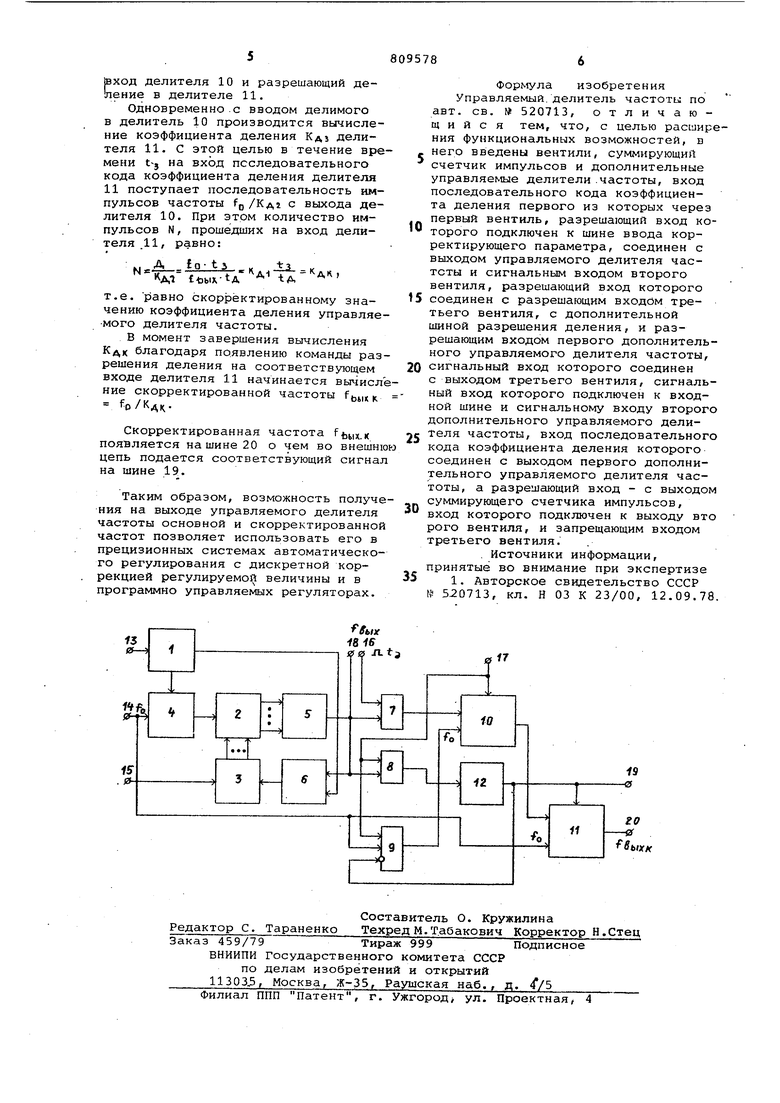

5 содержащий блок записи кода, на . вход которого подается сигнал ввода коэффициента деления, а выход соединен с разрядными входами счетчика импульсов, элемент ИЛИ, блок ,разре0шения деления, на вход которого подается сигнал разрешения и два элемента И-НЕ, первый вход первого из которых соединен с первым выходом блока разрешения деления, второй 5с шиной источника входного сигнала, а выход - с.о счетным -входом счетчика импульсов, разрядные выходы которого подключены ко входам второго элемента И-НЕ, выход которого соеди0нен с первым входом элемента ИЛИ, нторой вход которого подключен ко второму выходу блока разрешения деления, а выход - к входу блока записи кода, введены вентили, суммирующий счетчик импульсов и дополнительные управляемые делители частоты, вход последовательного кода коэффициента деления первоко из которых через первый вентиль, разрешающий вход которого подключен к шине ввода корректирующего параметра, соединен с выходом управляемого делителя частоты и сигнальным входом второго вентиля, разрешающий вход которого соединен с разрешающим вхо дом третьего вентиля с дополнительной шиной разрешения деления, и раз решающим входом первого дополнитель ного управляемого делителя частоты, сигнальный вход которого соединен с выходом третьего вентиля, сигналь ный вход которого подключен к входной шине и сигнальному входу допол нительного управляемого делителя ча тоты, вход последовательного кода к эффициента деления которого соединен с выходом первого дополнительно го управляемого делителя частоты, а разрешающий вход - с выходом суммирующего счетчика импульсов, вход которого подключен к выходу второго вентиля, и запрещающим входом третьего вентиля. На чертеже изображена структурная электрическая схема устройства. схема содержит блок 1 разрешения деления, счетчик 2 импульсов, блок 3 записи кода, элементы 4 и 5 И-НЕ, элемент 6 ИЛИ, вентили 7-9, дополнительные управляемые делители 10 и 11 частоты, счетчик 12 суммиру щих импульсов, шину 13 разрешения деления, шину 14 входной частоты, шину 15 кода коэффициента деления, шину 16 ввода корректирующего параметра, входную шину 17, выходную шину 18 основной частоты f,biA / шину 19, выдающую сигнал об окончании вычисления скорректированного коэффициента деления, выходную шину 20 скорректированной частоты. При определении частот f, , fbbij решается следующий алгоритм f ,.., о ,1 3 частоты соответственно на шине 14 и щине 18; коэффициент деления управляемого делите ля частоты; заданное значение корректирующего параметра;- коэффициент пропорциональностиKA2-ft)biX--tA-K7T7 A l1 коэффициент деления управляемого делителя 10; действительное значение корректирующего параметра, равное 1д tj iut; отклонение действительного значения корре1 тирующего параметра от заданного. (см. раK,j(ftobix ) Д fo венство 1 ), - где Д - делимое, вводимое в делитель 10, равное количеству импульсов частоты следования fд, прошедших за время его вход делимой частоты. к л -Ь-кз.:, с) , inH.ix-Ki -tA где Кд5 - коэффициент деления делителя 11, равный скорректированному значению коэффициента деления )с о fo I л fcbuk K l :;Ti t) (5) где ffcbix.K скорректированная частота на выходе делителя 11 (шина 20). Перед началом деления через шину 15 вводится код коэффициента деления К/,1 в блок 3. При поступлении через шину 13 команды Разрешение деления входная последовательность импульсов частоты fg делится на коэффициент деления Кд, пропорциональный заданному значению корректирующего параметра, напримервременной установке tj. В результате деления на шине 18 получим последовательность импульсов основной частоты ffebu Далее вычисляется коэффициент, деления Кдгделителя 10. С этой целью импульсы частоты fbbix с выхода элемента 5 через вентиль 7, открытый-в течение времени Ьд сигналом с шины 16, подаются на вход последовательного кода делителя 10. Для ввода делимого Д в делитель 10 на его сигнальный вход необходимо в течение времени t подать последовательность импульсов частоты f(j, для чего с шины 14 подаются на вход вентиля 9, открываемого сигналом с шины 17 в момент завершения импульса, длительностью Ьд на время tj. Для формирования интервала времени tj, равного tj Ka/fbbix, в схему устройства введены вентиль 8 и счетчик 12, емкость которого равна. Kj.. Суммирование импульсов частоты в счетчике 12 начинается с приходбм разрешающей команды с шины 17 на вентиль 8 одновременно с отпиранием вентиля 9. Время полного заполнения суммирующего счетчика 12 ЕЗДП равно: tjAn Ki/fbiix KJ/KI j 13, после чего на выходе счетчика 12 появляется сигнал о.завершении вычисления ско рректированного коэффициента деления, закрывающий вентиль 9, прекрывающий по хождение импульсов на

(вход делителя 10 и разрешающий деление в делителе 11.

Одновременно.с вводом делимого в делитель 10 производится вычисление коэффициента деления KAJ делителя 11. С этой целью в течение временк t-j на вход последовательного кода коэффициента деления делителя 11 поступает последовательность импульсов частоты fp /KAI с выхода делителя 10. При этом количество импульсов N, прошедших на вход делителя .11, равно:

ta

.А-

к

АК

tA

t)

т.е. равно скор эёктированному значению коэффициента деления управляемого делителя частоты.

В момент завершения вычисления Кдк благодаря появлению команды разрешения деления на соответствующем входе делителя 11 начинается вычисление скорректированной частоты fьикк о /К/ кСкорректированная частота ftinn.K появляется на шине 20 о чем во внешню цепь подается соответствующий сигнал на шине 19.

Таким образом, возможность получения на выходе управляемого делителя частоты основной и скорректированной частот позволяет использовать его в прецизионных системах автоматического регулирования с дискретной коррекцией регулируемой величины и в программно управляемых регуляторах.

Формула изобретения Управляемый, делитель частоты по авт. св. 520713, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены вентили, суммирующий счетчик импульсов и дополнительные управляемые делители.частоты, вход последовательного кода коэффициента деления первого из которых через первый вентиль, разрешающий вход ко0торого подключен к шине ввода корректирующего параметра, соединен с выходом управляемого делителя частоты и сигнальным входом второго вентиля, разрешающий вход которого

5 соединен с разрешающим входом третьего вентиля, с дополнительной шиной разрешения деления, и разрешающим входом первого дополнительного управляемого делителя частоты,

0 сигнальный вход которого соединен с выходом третьего вентиля, сигнальный вход которого подключен к входной шине и сигнальному входу второго дополнительного управляемого делителя частоты, вход последовательного

5 кода коэффициента деления которого соединен с выходом первого дополнительного управляемого делителя частоты, а разрешающий вход - с выходом суммирующего счетчика импульсов,

D

вход которого подключен к выходу ВТО

рого вентиля, и запрещающим входом третьего вентиля.

. Источники информации, принятые во внимание при экспертизе

5

Авторы

Даты

1981-02-28—Публикация

1978-09-12—Подача