СП

4 4

сх

Изобретение относится к имГ :.льс- ной технике и может быть использовано для построения устройств синхронизации с дискретным управлением.

Цель изобретения - повышение точности подстройки фазы выходного сигнала цифрового управляемого генератора.

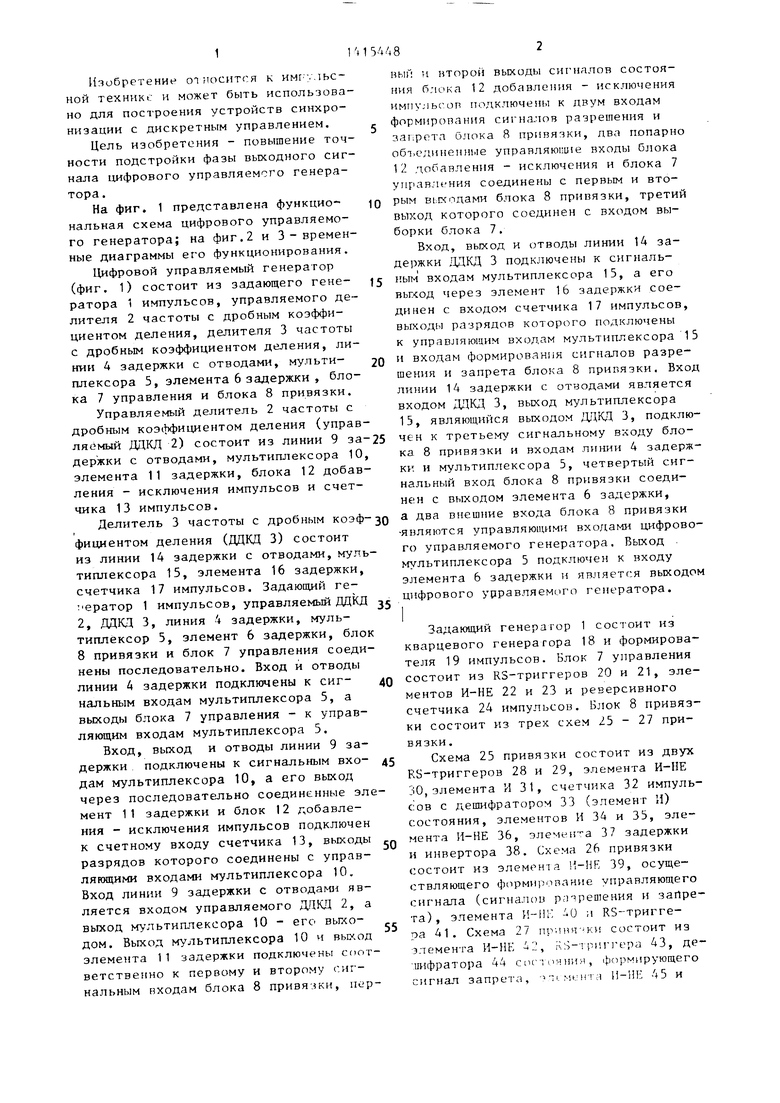

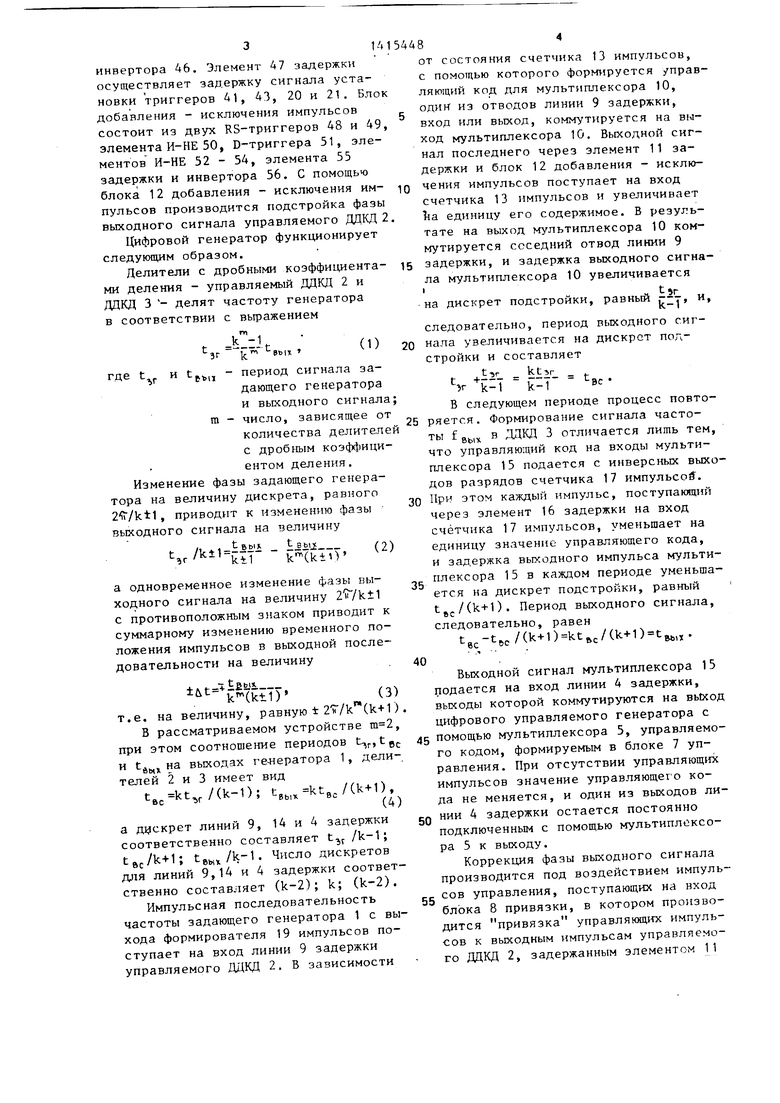

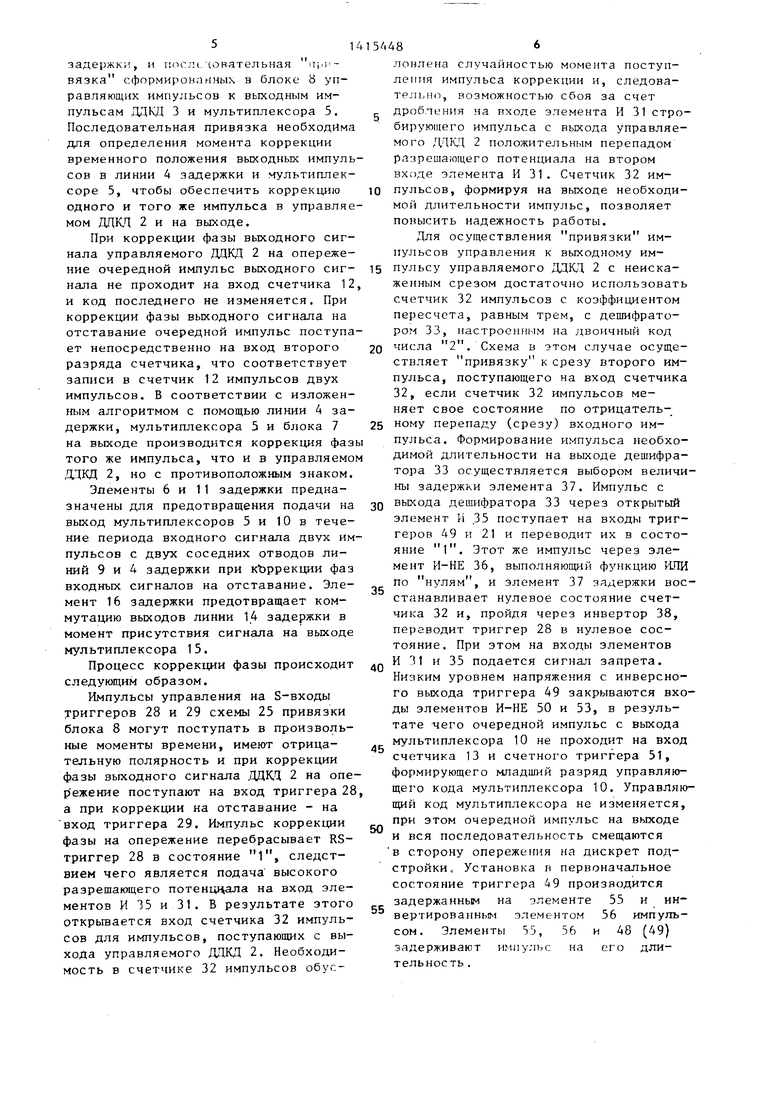

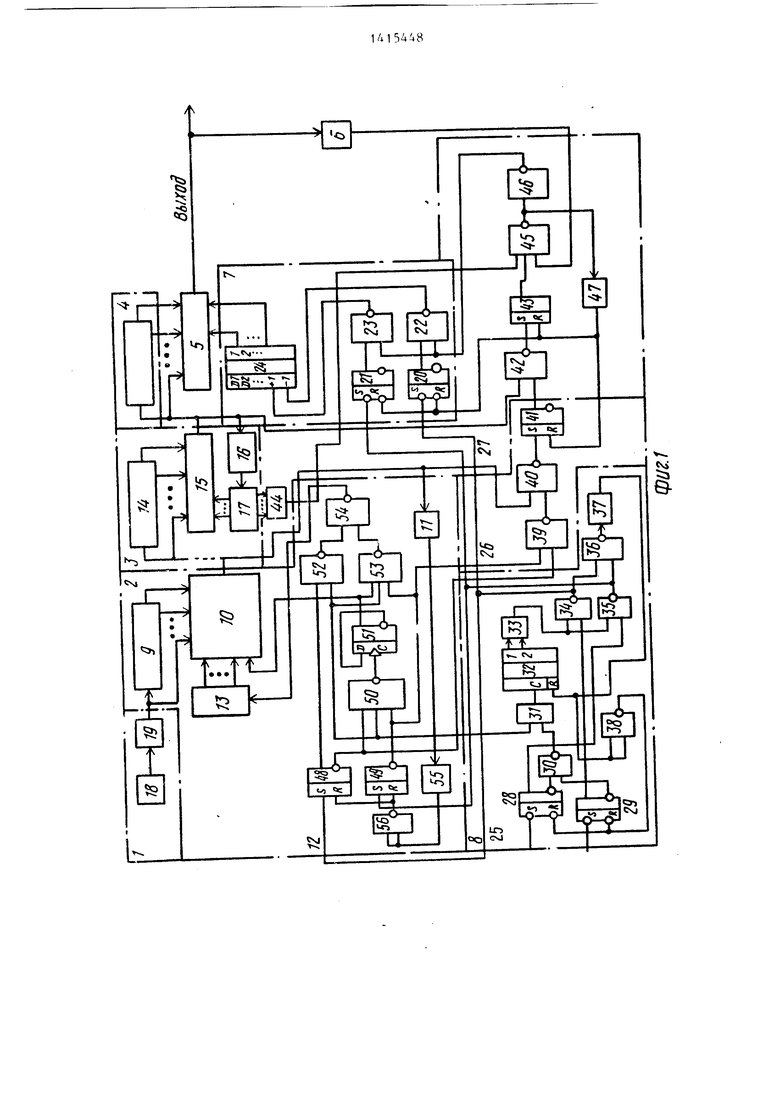

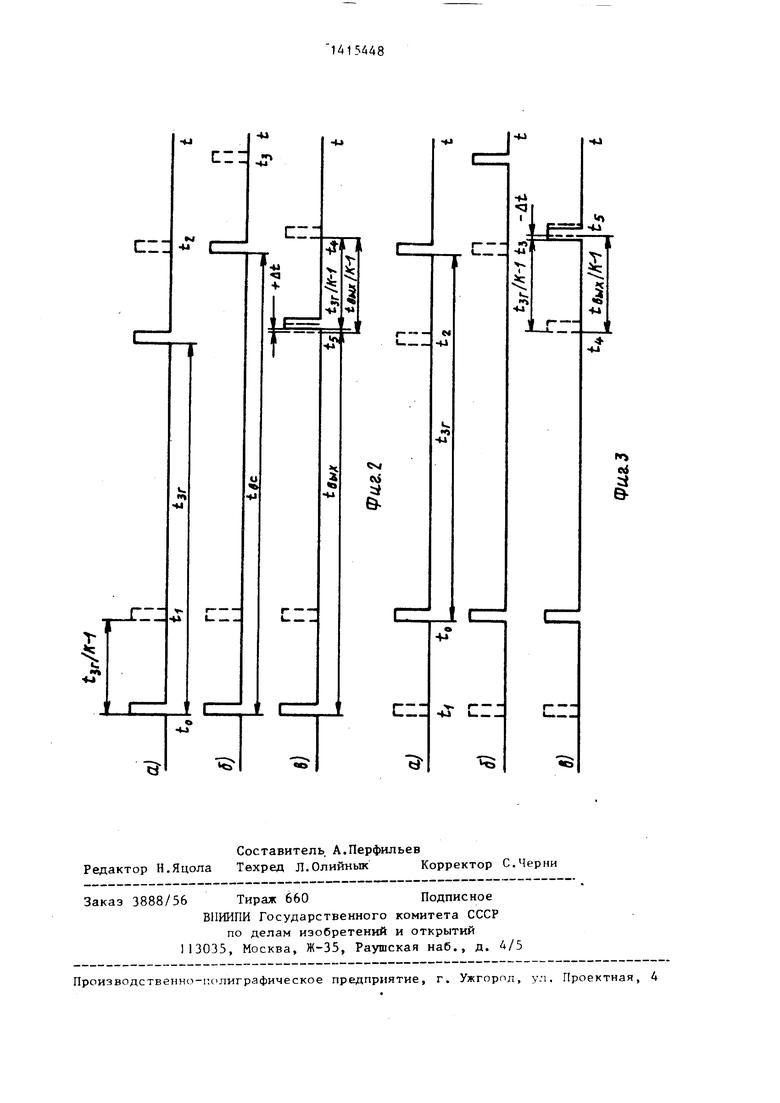

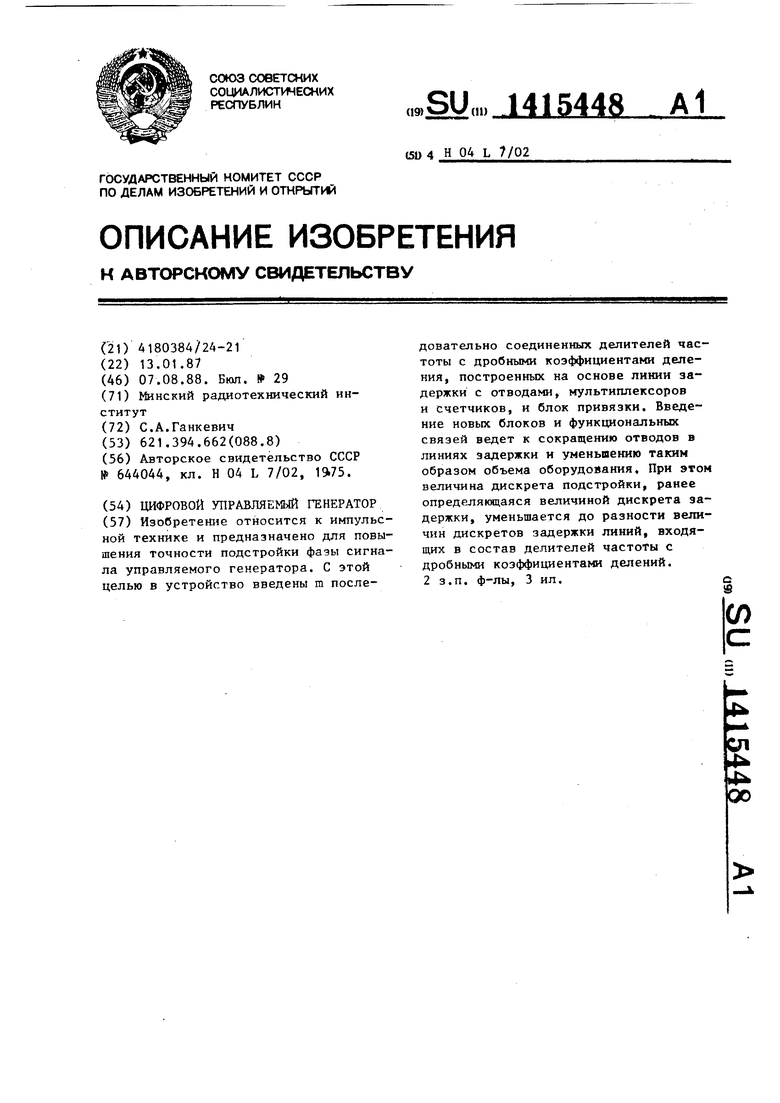

На фиг. 1 представлена функциональная схема цифрового управляемого генератора; на фиг.2 и 3 - временные диаграммы его функционирования.

Цифровой управляемый генератор (фиг. 1) состоит из задающего генератора 1 импульсов, управляемого делителя 2 частоты с дробным коэффициентом деления, делитепя 3 частоты с дробным коэффициентом деления, линии 4 задержки с отводами, мультиплексора 5, элемента 6 задержки , блока 7 управления и блока 8 привязки. Управляемый делитель 2 частоты с дробным коэсЬфициентом деления (управляемый ДДКД 2) состоит из линии 9 задержки с отводами, мультиплексора 10 элемента 11 задержки, блока 12 добавления - исключения импульсов и счетчика 13 импульсов.

Делитель 3 частоты с дробным коэффициентом деления (ДДКД 3) состоит из линии 14 задержки с отводами, мультиплексора 15, элемента 16 задержки, счетчика 17 импульсов. Задающий ге- ератор 1 импульсов, управляемый ДЦКД 2, ДДКД 3, линия 4 задержки, мультиплексор 5, элемент 6 задержки, бло 8 привязки и блок 7 управления соединены последовательно. Вход и отводы линии 4 задержки подключены к сигнальным входам мультиплексора 5, а вькоды блока 7 управления - к управляющим входам мультиплексора 5.

Вход, выход и отводы линии 9 задержки подключены к сигнальным входам гультиплексора 10, а его выход через последовательно соединенные элмент 11 задержки и блок 12 добавления - исключения импульсов подключен к счетному входу счетчика 13, выходы разрядов которого соединены с управляющими входами мультиплексора 10. Вход линии 9 задержки с отводами является входом управляемого ДЦКД 2, а выход мультиплексора 10 - его выходом. Выход мультиплексора 10 и выход элемента 11 задержки подключены соответственно к первому и второму сигнальным Езходам блока 8 привязки, пер0

вый и второй выходы сигналов состояния б:1окп 12 добавления - исключения импульс.on подключены к двум входам формирования сигналов разрешения и запрета блока 8 привязки, два попарно обт,единепн1.1е управдяю1 и1е входы блока 12 добавления - исключения и блока 7 управления соединены с первым и вторым виходами блока 8 привязки, третий выход которого соединен с входом выборки блока 7.

Вход, вькод и отводы линии 14 задержки ДДКД 3 подключены к сигналь5 ньп-1 входам мультиплексора 15, а его вькод через элемент 16 задержки соединен с входом счетчика 17 импульсов, вькоды разрядов которого подключены к управляющим входам мультиплексора 15

0 и входам формирования сигналов разрешения и запрета блока 8 привязки. Вход линии 14 задержки с отводами является входом ДДКД 3, выход мультиплексора 15, являющийся выходом ДЦКД 3, подключен к третьему сигнальному входу блока. 8 привязки и входам линии 4 задержки и мультиплексора 5, четвертый сигнальный вход блока 8 привязки соединен с выходом элемента 6 задержки, а два внешние входа блока 8 привязки являются управляющими входами цифрового управляемого генератора. Выход мультиплексора 5 подключен к входу элемента 6 задержки и является выходом цифрового урравляемого генератора.

5

0

5

0

5

0

5

Задаюш 1й генератор 1 состоит из кварцевого генератора 18 и формирователя 19 импульсов. Блок 7 управления состоит из RS-триггеров 20 и 21, элементов И-НЕ 22 и 23 и реверсивного счетчика 24 импульсов. Блок 8 привязки состоит из трех схем 25 - 27 привязки.

Схема 25 привязки состоит из двух FlS-триггеров 28 и 29, элемента И-НЕ 30,элемента И 31, счетчика 32 импуль- с;ов с дешифратором 33 (элемент И) состояния, элементов И 34 и 35, элемента И-НЕ 36, элемента 37 задержки и инвертора 38. Схема 26 привязки состоит из элемента -НЕ 39, осуществляющего формирование управляющего сигнала (сигналом рс-прешения и запрета), элемента И.-НК 0 и RS-тригге- ра 41. Схема 27 пр .ииг ки состоит из элемента И-НЕ 2, ixS-Tpnri epa 43, де- иифратора 44 спс,нянин, юрмирующего сигнал запрета, TI-г-и. ита И-НУ 45 и

314

инвертора 46. Элемент 47 задержки осуществляет задержку сигнала установки триггеров 41, 43, 20 и 21. Блок добавления - исключения импульсов состоит из двух RS-триггеров 48 и 49, элемента И-НЕ 50, D-триггера 51, элементов И-НЕ 52 - 54, элемента 55 задержки и инвертора 56. С помощью блока 12 добавления - исключения импульсов производится подстройка фазы выходного сигнала управляемого ДЦКД2.

Цифровой генератор функционирует следующим образом.

Делители с дробными коэффициентами деления - управляемый ДДКД 2 и ДЦКД 3 - делят частоту генератора в соответствии с вьфажением

m ЗГ

где t j. и , - период сигнала задающего генератора и выходного сигнала; m - число, зависящее от количества делителей с дробным коэффициентом деления.

Изменение фазы задающего генератора на величину дискрета, равного 2 u/ktl , приводит к изменению фазы выходного сигнала на величину

f /v l --Sb Ji tji l (2)

,r ki1

а одновременное изменение фазы выходного сигнала на величину с противоположным знаком приводит к суммарному изменению временного положения импульсов в выходной последовательности на величину

)

(3)

т.е. на величину, равную t 2 ir/k Ck+1).

В рассматриваемом устройстве , при этом соотношение периодов Цг,йр. и tg на выходах ге-нератора 1, дели-, телей 2 и 3 имеет вид

,/(k-1); t,,,,ktB,/(k+1).

(}

а дускрет линий 9, 14 и 4 задержки соответственно составляет t /k-1; tewn/H Число дискретов для линий 9,14 и 4 задержки соответственно составляет (k-2); k; (k-2).

Импульсная последовательность частоты задающего генератора 1 с выхода формирователя 19 импульсов поступает на вход линии 9 задержки управляемого ДЦКД 2. В зависимости

8

от состояния счетчика 13 импульсов, с помощью которого формируется управляющий код для мультиплексора 10, одик из отводов линии 9 задержки, вход или выход, коммутируется на выход мультиплексора 10. Выходной сигнал последнего через элемент 11 задержки и блок 12 добавления - исключения импульсов поступает на вход счетчика 13 импульсов и увеличивает lia единицу его содержимое. В результате на выход мультиплексора 10 коммутируется соседний отвод линии 9 задержки, и задержка выходного сигна

ла мультиплексора 10 увеличивается

на

20

дискрет подстройки, равный rfV, и,

к I

следовательно, период выходного сигнала увеличивается на дискрет подстройки и составляет

42 k-1

k-Г в

В следующем периоде процесс повто- ряется. Формирование сигнала часто- выи ДДКЦ 3 отличается лишь тем, что управляющий код на входы мультиплексора 15 подается с инверсных выходов разрядов счетчика 17 импульсов. При этом каждый импульс, поступающий через элемент 16 задержки на вход счётчика 17 импульсов, уменьшает на единицу значение управляющего кода, и задержка выходного импульса мультиплексора 15 в каждом периоде уменьшается на дискрет подстройки, равный tgj/(k+1). Период выходного сигнала.

следовательно, равен

tg -tgt;/(k+l)(k+l)

40

.

Выходной сигнал мультиплексора 15 подается на вход линии 4 задержки, выходы которой коммутируются на вь1ход цифрового управляемого генератора с 45 помощью мультиплексора 5, управляемого кодом, формируемьтм в блоке 7 управления. При отсутствии управляющих импульсов значение управляющего кода не меняется, и один из выходов ли- 50 НИИ 4 задержки остается постоянно подключенным с помощью мультиплексора 5 к выходу.

Коррекция фазы выходного сигнала производится под воздействием импульсе сов управления, поступающих на вход блока 8 привязки, в котором производится привязка управляющ1-гх импульсов к выходным импульсам управляемого ДДКД 2, задержанным элементом 11

задержки, н nocjit. човательная ai-i - вязка сформиронанных в блоке 8 управляющих импульсов к выходным импульсам ДДКД 3 и мультиплексора 5. Последовательная привязка необходима для определения момента коррекции временного положения выходных импульсов в линии 4 задержки и мультиплексоре 5, чтобы обеспечить коррекцию одного и того же импульса в управляемом ДДК,Ц 2 и на выходе.

При коррекции фазы выходного сигнала управляемого ДДКД 2 на опережение очередной импульс выходного сигнала не проходит на вход счетчика 12 и код последнего не изменяется. При коррекции фазы выходного сигнала на отставание очередной импульс поступает непосредственно на вход второго разряда счетчика, что соответствует записи в счетчик 12 импульсов двух импульсов. В соответствии с изложенным алгоритмом с помощью линии 4 задержки, мультиплексора 5 и блока 7 на выходе производится коррекция фаз того же импульса, что и в управляемо ДДКД 2, но с противоположным знаком.

Элементы 6 и 11 задержки предназначены для предотвращения подачи на выход мультиплексоров 5 и 10 в течение периода входного сигнала двух импульсов с двух соседних отводов линий 9 и 4 задержки при кЪррекции фаз входных сигналов на отставание. Элемент 16 задержки предотвращает коммутацию выходов линии 14 задержки в момент присутствия сигнала на выходе мультиплексора 15.

Процесс коррекции фазы происходит следующим образом.

Импульсы управления на S-входы триггеров 28 и 29 схемы 25 привязки блока 8 могут поступать в произвольные моменты времени, имеют отрицательную полярность и при коррекции фазы выходного сигнала ДДКД 2 на опе- р ежение поступают на вход триггера 28 а при коррекции на отставание - на вход триггера 29. Импульс коррекции фазы на опережение перебрасывает RS- триггер 28 в состояние 1, следствием чего является подача высокого разрешающего потенциала на вход элементов И 35 и 31. В результате этого открьгаается вход счетчика 32 импульсов для импульсов, поступающих с выхода управляемого ДДКД 2. Необходимость в счетчике 32 импульсов обус

5

0

5

0

5

0

5

5

лонлена случайностью момента поступления импульса коррекции и, следовательно, возможностью сбоя за счет дробления на входе элемента И 31 стро- бирующего импульса с выхода управляемого /ЩКД 2 положительным перепадом разрешающего потенциала на втором входе элемента И 31. Счетчик 32 импульсов, формируя на выходе необходимой длительности импульс, позволяет повысить надежность работы.

Для осуществления привязки импульсов управления к выходному импульсу управляемого ДДК,Д 2 с неискаженным срезом достаточно использовать счетчик 32 импульсов с коэффициентом пересчета, равным трем, с дешифратором 33, настроенным на двоичный код числа 2. Схема в этом случае осуществляет привязку к срезу второго импульса, поступающего на вход счетчика 32, если счетчик 32 импульсов меняет свое состояние по отрицательному перепаду (срезу) входного импульса. Формирование импульса необходимой длительности на выходе дешифратора 33 осуществляется выбором величины задержки элемента 37. Импульс с выхода дешифратора 33 через открытый элемент И 35 поступает на входы триггеров 49 и 21 и переводит их в состояние 1. Этот же импульс через элемент И-НЕ 36, выполняющий функцию ИЛИ по нулям, и элемент 37 задержки восстанавливает нулевое состояние счетчика 32 и, пройдя через инвертор 38, переводит триггер 28 в нулевое состояние. При этом на входы элементов И 31 и 35 подается сигнал запрета. Низким уровнем напряжения с инверсного выхода триггера 49 закрываются входы элементов И-НЕ 50 и 53, в результате чего очередной импульс с выхода мультиплексора 10 не проходит на вход счетчика 13 и счетного триггера 51, формирующего младший разряд управляю- щег о кода мультиплексора 10. Управляющий код мультиплексора не изменяется, при этом очередной импульс на выходе и вся последовательность смещаются в сторону опережения на дискрет подстройки . Установка ri первоначальное состояние триггера 49 производится задержанным на элементе 55 и инвертированным элементом 56 импульсом. Элементы 55, 36 и 48 (49) задерживают импу;1ьс на его длительность .

14

Для осуществления коррекции фазы последовательности на выходе устройства, с помощью линии 4 задержки, мультиплексора 5 и блока 7 необходимо определить момент поступления на вход линии задержки импульсной последовательности, коррекция фазы которой произведена в управляемом ДЦКД 2 Определение этого момента обеспечивается с помощью схем 26 и 27 привязки В результате переброса триггера 49 в состояние 1 импульсом управления с элемента li-HE 39, выполняющего функцию ИЛИ по нулям, на вход элемента И-НЕ 40 подается разрешение, и последним импульсом с нескорректированным значением фазы с выхода уп- ра1зляемого ДЦКД 2 RS-триггер 41 переводится в положение 1. С выхода триггера 41 на элемент И-НЕ 42 подается разрешение, и последний импульс с нескорректированной фазой с выхода ДДКД 3 через элемент И-НЕ 42 перебрасывает триггер 43 в состояние 1, в результате чего на вход элемента И-НЕ 45 подается разрешение. Последний импульс с нескорректированной фазой в выходной последовательности через элемент И-НЕ 45, инвертор 46 и элемент И-НЕ 23 поступает на вход счетчика 24 импульсов и изменяет его состояние на единицу. Под действием нового значения управляющего кода производится переключение отводов линии 5 задержки. Величина задержки выходных имеульсов увеличивается на дискрет и, начиная со следующего импульса, выходная последовательность изменяет фазу на величину дискрета подстройки. Задержанный элементом 47 импульс с выхода элемента И-НЕ 45 устанавливает триггеры 21, 41 и 43 в

исходное состояние.

Разрешение на второй вход элемента И-НЕ 45 подается с дешифратора 44 состояния счетчика 17 импульсов. Дешифратор 44, выполненный на элементе И-НЕ, с числом входов, равным разрядности управляющего кода, выделяет минимальное значение управляющего кода, при котором вход линии 14 задержки коммутируется непосредственно на выход мультиплексора 15 и низким уровнем напряжения на своем выходе закрывает вход элемента И-НЕ 45, что обеспечивает запрет привязки выходного импульса цифрового управляемого генератора к выходному импульсу мультиплексора 15, прошедшему на выход

15448

непосредственно с входа линии 14 задержки ,

Временные диаграммы (фиг. 2) ил- 5 люстрируют процесс коррекции фазы выходного сигнала в цифровом управляемом генераторе.

При коррекции фазы выходного сигнала на опережение фаза сигнала за- 10 дающего генератора с помощью ДЦКД 2 корректируется на отставание (фиг.2), при этом положение импульса (фиг.2а)

изменяется на величину

biL k-1

и соответ

ствует моменту t, что приводит к изменению временного положения вспомогательного сигнала на выходе управляемого ДЦК,Ц 2 (фиг. 26) и выходного сигнала (фиг. 2г). Следуюпщй импульс задающего генератора формируется в момент t, вспомогательного сигнала - в момент t, а выходного сигнала - в момент t. Одновременная коррекция временного положения (фазы) выходного сигнала на опережение на величину

- приводит к тому, что очередной

импульс выходного сигнала занимает положение tj. Таким образом, коррек- ция фазы выходного сигнала на опере2 Г

жение составляет величину гтт;-тг«

k(k-1)

При коррекции фазы выходного сигнала на отставание , (фиг. За - в ) фаза сигнала задающего генератора в управляемом ДДКД 2 корректируется на опережение, а фаза вьцсодного сигнала - на отставание.

Предлагаемый цифровой управляемый

генератор по сравнению с известным позволяет значительно повысить точность подстройки фазы выходного сигнала бее увеличения объема оборудования

Формула изобретения 1. Цифровой управляемый генератор, содержащий задающий генератор импульсов, линию задержки с отводами, мультиплексор, элемент задержки и блок

управления, выходы которого подключены к управляющим входам мультиплексора, сигнальные входы которого соединены с входом, выходом и отводами линии задержки, а выход мультиплексора

подключен к выходу цифрового управляемого генератора, отличающийся тем, что, с целью повьшде- ния точности подстройки фазы выходного сигнала, в него введены повледова91Д

тельно соединенные управляемьш делитель частоты с дробным коэффициентом деления и га делителей частоты с дробным коэффициентом деления, а также блок привязки выход задающего генера тора импульсов подключен к счетному йходу управляемого делителя частоты с дробным коэффициентом деления, пер- вый и второй выходы которого подключены соответственно к первому и второму сигнальным входам блока привязки, последующие сигнальные входы которого подключены к выходам делителей чаЬтоты с дробными коэффициентами деления и к выходу элемента задержки, подключенного к выходу мультиплексора, входы формирования сигналов раз- рещения и запрета блока привязки подключены к третьему и четвертому выходам управляемого делителя частоты с дробным коэффициентом деления и дополнительным выходам т-го делителя частоты с дробным коэффициентом деления, основной выход которого подключен к входу линии задержки с отводами, первый и второй выходы блока привязки соединены соответственно с первый и вторым управляющими входами упрайляемого делителя частоты с дробным коэффициентом деления и параллельно - с первым и вторым управляющими входами блока управления соответственно, третий выход блока привязки соединен с входом выборки блока управления, управляющие входы блока привязки являются управляющими входами цифрового управляемого генератора.

2, Генератор по п. 1, отличающийся тем, что управляе- делитель частоты с дробным коэффициентом деления содержит линию задержки с отводами, мультиплексор, элемент задержки, блок добавления- исключения импульсов и счетчик импульсов, счетный вход которого подключен к первому выходу блока добав8V

ления-исключения импульсов, второй выход которого подключен к первому управляющему входу мультиплексора,

выход которого подключен к элементу

задержки и является первым выходом

управляемого делителя частоты с дробным коэффициентом деления, счетный вход которого подключен к входу ЛИНИИ задержки с отводами, вход, выход и отводы которой подключены к сигнальным входам мультиплексора, остальные управляющие входы которого подключены к выходам разрядов счетчи- ка импульсов, первый и второй входы блока добавления-исключения импульсов подключены к управляющим входам управляемого делителя частоты с дробным коэффициентом деления, третий и чет- вертый выходы которого подключены соответственно к третьему и четвертому выходам блока добавления-исключения импульсов, вход которого подключен к выходу элемента задержки и является вторым выходом управляемого делителя частоты с дробным коэффициентом деления .

3. Генератор по п. 1, о т л и - чающийся тем, что каждый из делителей частоты с дробным коэффициентом деления содержит линию задержки с отводами, мультиплексор, элемент задержки и счетчик импульсов, выходы разрядов которого подключены к управляющим входам мультиплексора и дополнительным выходам делителя частоты с дробным коэффициентом деления, вход которого подключен к входу линии за- держки с отводами, вход, выход и отг воды которой подключены к сигнальным входам мультиплексора, выход которого явлАется основным выходом делителя с дробным коэффициентом деления и под- клйчен к входу элемента задержки, выход которого подключен к счетному входу счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой управляемый генератор | 1986 |

|

SU1378022A1 |

| Программируемый делитель частоты | 1980 |

|

SU871340A2 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| Широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты | 2019 |

|

RU2716222C1 |

| Корреляционное устройство дляОпРЕдЕлЕНия зАдЕРжКи | 1979 |

|

SU849226A1 |

| Цифровой синтезатор сигналов | 1988 |

|

SU1525694A1 |

| Цифровой управляемый генератор | 1989 |

|

SU1748247A1 |

| Устройство фазирования шкалы времени электронных часов | 1990 |

|

SU1746356A1 |

| Цифровой умножитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU824440A1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ВЫСОКОЧАСТОТНОГО СИГНАЛА | 1989 |

|

SU1734562A1 |

Изобретение относится к импульсной технике и предназначено для повышения точности подстройки фазы сигнала управляемого генератора. С этой целью в устройство введены m последовательно соединенных делителей частоты с дробными коэффициентами деления, построенных на основе линии задержки с отводами, мультиплексоров и счетчиков, и блок привязки. Введение новых блоков и функциональных связей ведет к сокращению отводов в линиях задержки и уменьшению таким образом объема оборудования. При этом величина дискрета подстройки, ранее определяющаяся величиной дискрета задержки, уменьшается до разности величин дискретов задержки линий, входящих в состав делителей частоты с дробными коэффициентами делений. 2 з.п. ф-лы, 3 ил. с б

| Устройство синхронизации | 1975 |

|

SU644044A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-08-07—Публикация

1987-01-13—Подача